Изобретение относится к автоматике, вычислительной и информационно- измерительной технике и может быть использовано для преобразования выходных сигналов цифровых измеритель- ,ных приборов., представленных в виде разрядного двоично-десятичного кода, в аналоговый сигнал по логарифмическому закону.

Цель изобретение - упрощение преобразователя .

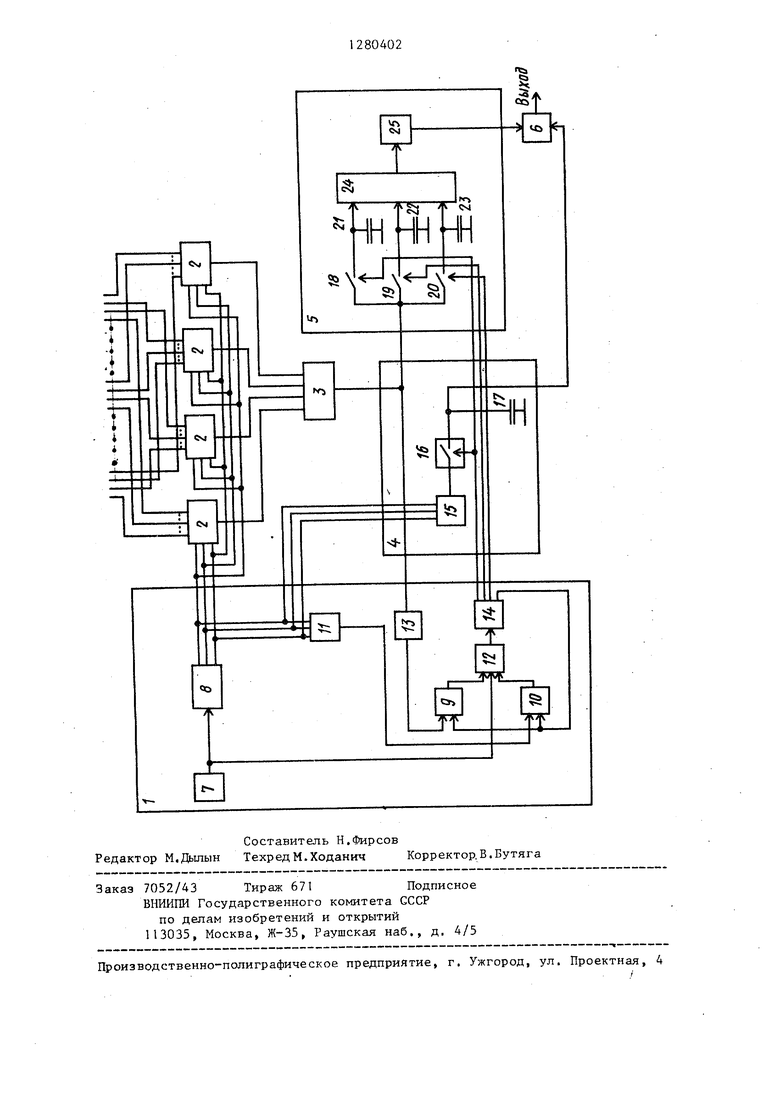

На чертеже представлена блок схема устройства.

Цифроаналоговый логарифимический преобразователь coctoит из блока 1 выделения старших значащих разрядов кода входного числа преобразователя, группы мультиплексоров 2, дифроана- логового преобразователя 3, блока 4 определения характеристики логарифма, блока 5 определения мантиссы логарифма, выходного--сумматора 6, Блок 1 содержит генератор 7 импуль- С9В, счетчик 8, два триггера 9 и 10, два элемента II и 12, компаратор 13, распределитель 14 импульсов. Блок 4 содержит Цифроаналоговый преобразователь 15, ключ 16, запоминающий конденсатор 17, Блок 5 содержит три ключа 18, 19, 20, три запоминающих конденсатора 21, 22 и 23, весовой аналоговый сумматор 24, логарифмический преобразователь 25,

Преобразователь работает следующим образом.

Входной сигнал, представленный в N разрядном двоично-десятичном коде, подается на входы четырех мультиплексоров 2, которые поразрядно, начиная со старшего разряда, направ

-

ляют входной сигнал на входы четырехразрядного цифроаналогового преобразователя 3, Преобразователь 3 пре- образует цифровой сигнал каждого десятичного разряда в аналоговый сиг- нал.

Управление мультиплексорами осуществляется выходными сигналакш счетчика 8, поступающими с его инверсных выходов на адресные входы мультиплексоров 2, Число разрядов счетчика 8 равно , Нулевой адрес (наличие сигналов соответствующих 1 на инверсных выходах) соответствует под- ключению старшего разряда входного сигнала. Одновременно выходные сигналы счетчика 8 поступают на входы схемы I 1 и на входы . разрядного

10

15

20

25

30

35

цифроаналогового преобразователя 15, При выходных сигналах счетчика 8, соответствующих, например, нулевому адресу, на выходе элемента 11 формируется сигнал 1, который с помощьна, триггера 10 устанавливает на первом входе элемента 12 сигнал 1, На выходе преобразователя 15 формируется при этом аналоговый сигнал, величина которого пропорциональна выходному сигналу счетчика 8 и номеру подключенного к преобразователю 3 разряда входного сигнала.

Синхронизация устройства осуществляется выходными сигналами генератора 7, При подключении к входам преобразователя 3 первого не равного нулю разряда входного сигнала компаратор 13 формирует сигнал, который с помощью триггера 9 устанавливает

12 сигнал

на втором входе элемента , тем самым разрешая проход импульсных сигналов с выхода генерато- ра 7 на вход распределителя 1.

Выходные сигналы распределителя 14 управляют ключами 16 и 18 следующим образом, С приходом первого импульса на вход распределителя 14 на ё го первом выходе формируется сигнал, замыкающий ключи 16 и 18, При этом величина выходного сигнала преобразователя 15, пропорциональна номеру старшего не равного нулю разряда, соответствует характеристике десятичного логарифма входного сигнала. Выходной сигнал преобразователя 15 при этом запоминается на конденсаторе 17 и поступает на первый вход сумматора 6, Выходной сиг- нал преобразователя 3, величина которого соответствует коду старшего не равного нулю разряда входного сигнала, запоминается на конденсаторе 21, С приходом второго импульса на вход распределителя 14 на его гтором выходе формируется сигнал, замыкающий ключ 19, и аналоговьй сигнал, величина.которого соответствует коду следующего разряда входного сигнала, запоминается на конденсаторе 22, С приходом третьего импульса на вход распределителя 14 на его третьем выходе формируется сигнал, замыкающий ключ 20, и аналоговьй сигнал, величина которого пропорциональна коду следующего разряда входного сигнала, запоминается на конденсаторе 23, С приходом четвертого |импульса на вход распределитепя 9

3

происходит сброс тригг нулевое состояние и пр на вход распределителя мент 12 прекращается. чивается цикл цифроана образования, следующий ся с появления на выхо кода, соответствующего су. Выходные сигналы з конденсаторов 21, 22 и на первый, второй и тр сумматора 24, выходной рого, равный и,2ч U + 0,01Ugb,,2j поступаегарифмического преобра Выходной сигнал преобр пропорциональный десяти му выходного сигнала су

k IgU

&ЫХ 21

соответствует

мантиссе логарифма входного сигнала и поступает на второй вход сумматор 6. Сумматор 6 осуществляет суммировние мантиссу и характеристики логарифма входного сигнала. На выходе сумматора 6, являющемся выходом уст- ройст ва, формируется сигнал, соответствующий десятичному логарифму, входного сигнала.

Формула изобретения

Цифроаналоговый логарифимический преобразователь, содержащий группу мультиплексоров, информационные входы которых являются информационным входом преобразователя, блок выделения старших значащих разрядов кода входного числа преобразователя, блок определения характеристик логарифма блок определения мантиссы логарифма отличающийся тем, что, с целью упрощения преобразователя, в него введены цифроаналоговый преобразователь и выходной сумматор, выход которого является выходом преобразователя, причем блок выделения старших значащих разрядов кода входного сигнала числа содержит генератор импульсов, счетчик, два элемента И, два триггера, компаратор и распределитель импульсов, первый выход которого соединен с входами установки в ноль первого и второго триггеров, выходы которых подключены к первому и второму входам первого элемента И, соединенного выхо.5 5

0

5

0

5

0

5

0

5

дом с входом распределителя импульсов, выход генератора импульсов подключен к третьему входу первого элемента И и счетному входу счетчика, инверсные выходы которого соединены с входами второго элемента И, соединенного выходом с входом установки в единицу первого триггера, вход установки в единицу второго триггера соединен с выходом компара- ;тора, блок определения характеристики логарифма содержит последовательно соединенные цифроаналоговый преобразователь, ключ и запоминающий конденсатор, другая обкладка которого подключена к шине нулевого потенциала, блок определения мантиссы логарифма содержит аналоговый логарифмический преобразователь, весо- - вой аналоговый сумматор, три запоминающих конденсатора и три ключа, информационные входы которых соединены между собой, а выходы соединены с соответствующими входами весового аналогового сумматора и через соответствующие запоминающие конденсаторы подключены к шине нулевого потенциала, выход весового аналогового сумматора соединен с информационным входом аналогового логарифмического преобразователя, соединенного выходом с первым входом выходного аналогового сумматора, второй вход которого подключен к выходу ключа блока определения характеристики логарифма, инверсные выходы счетчика блока выделения старших значащих разрядов кода входного числа преобразователя подключены к цифровым входам цифро- аналогового преобразователя блока определения характеристики логарифма и к управляющим входам мультиплексоров группы, выходы которых подключены к цифровому входу цифроаналогового преобразователя, выход которого подключен к входу компаратора блока выделения старших значащих разрядов кода входного числа и к информационным входам первого, второго и третьего ключей блока определения мантиссы логарифма, управляющие входы которых соединены соответственно с вторым, третьим и четвертым выходами распределителя импульсов блока выделения старших значащих разрядов кода входного числа преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный фильтр | 1983 |

|

SU1131028A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| Следящий функциональный преобразователь | 1976 |

|

SU634308A1 |

| Устройство для логарифмирования чисел | 1980 |

|

SU926655A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| Аналого-цифровое интегрирующее устройство | 1985 |

|

SU1275483A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Логарифмический преобразователь | 1979 |

|

SU840951A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Станок для кантования с трех сторон бревен | 1926 |

|

SU4900A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-12-30—Публикация

1984-10-23—Подача