Изобретение относится к вычисли- тельной технике и предназначено для использования в микропроцессорных системах, содержащих два процессора.

.Цель изобретения - увеличение быстродействия использовании общей памяти с одновременным упрощением протоколов обмена между микропроцессорными системами и общей памятью. .

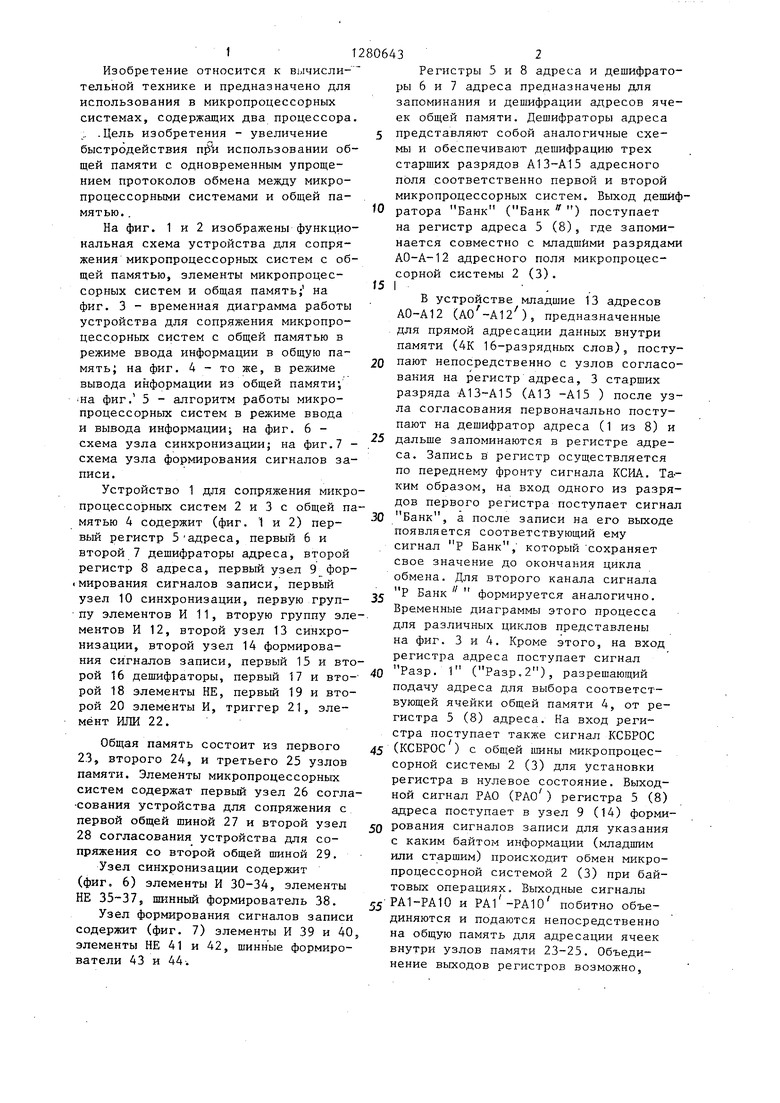

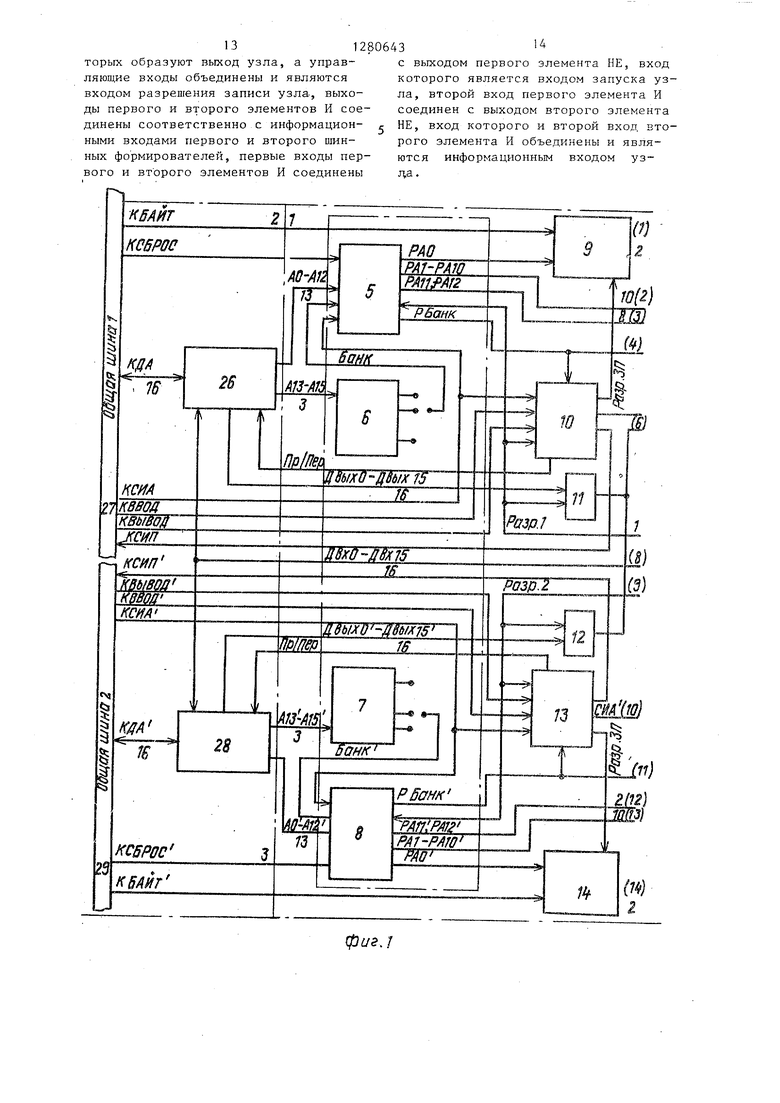

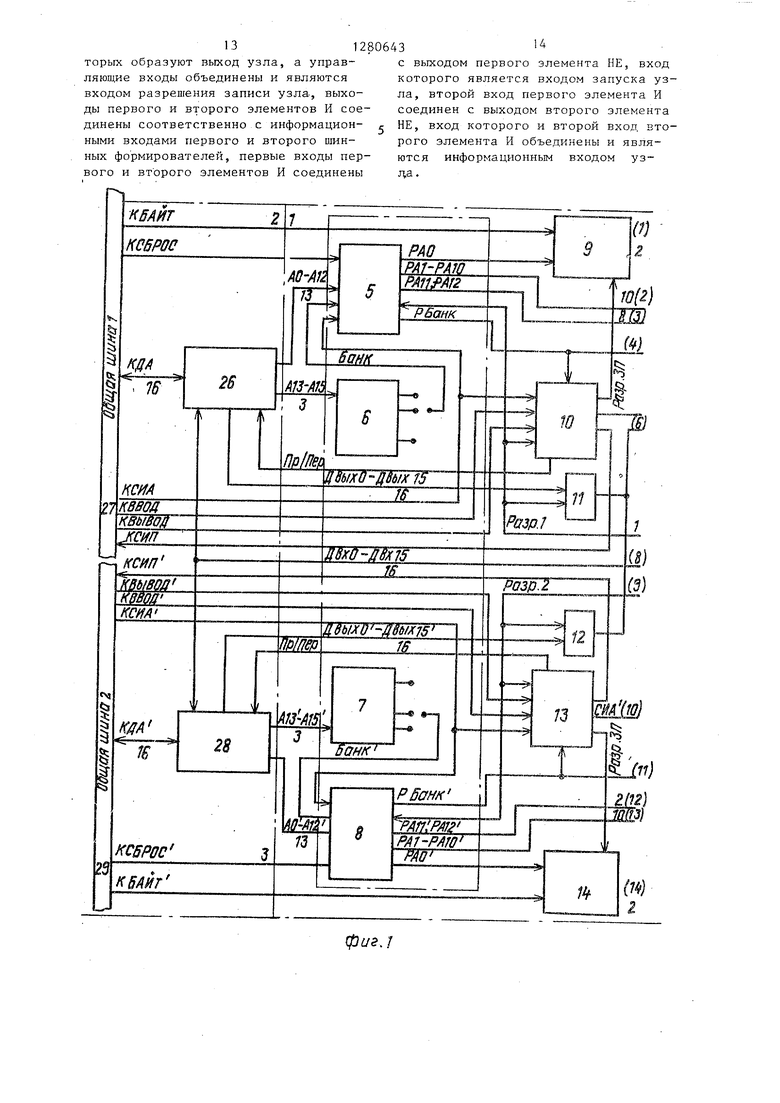

На фиг. 1 и 2 изображены функциональная схема устройства для сопряжения микропроцессорных систем с общей памятью, элементы микропроцессорных систем и общая память; на фиг. 3 - временная диаграмма работы устройства для сопряжения микропроцессорных систем с общей памятью в режиме ввода информации в общую память; на фиг. 4 - то же, в режиме вывода информации из общей памяти;

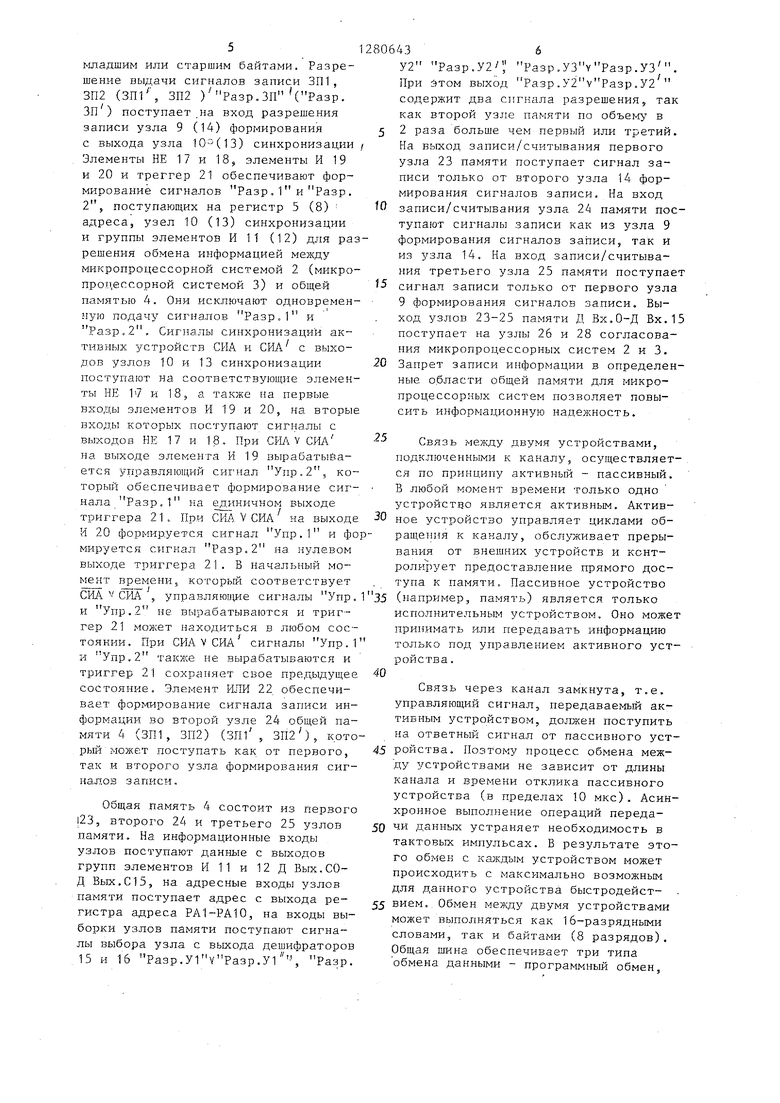

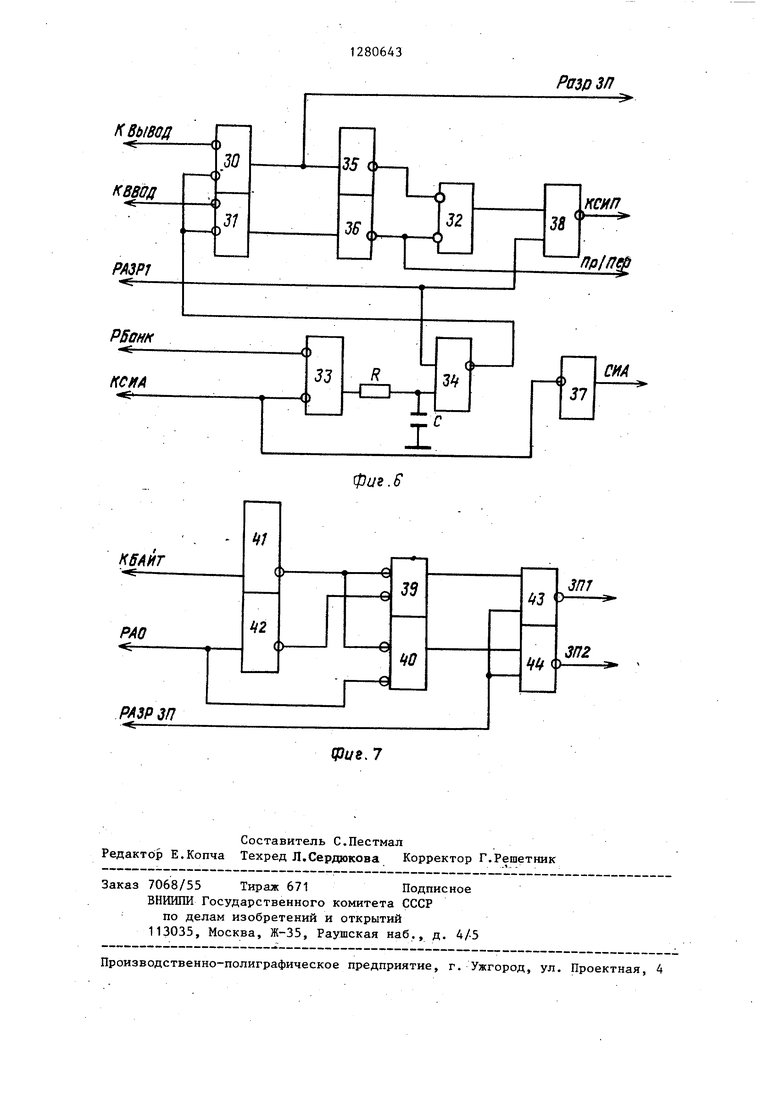

на фиг. 5 - алгоритм работы микропроцессорных систем в режиме ввода и вывода информацииJ на фиг. 6 - схема узла синхронизации; на фиг.7 - схема узла фо рмирования сигналов записи.

Устройство 1 для сопряжения микропроцессорных систем 2 и 3 с общей памятью 4 содержит (фиг. 1 и 2) пер- вьш регистр 5 адреса, первый 6 и второй 7 дешифраторы адреса, второй регистр 8 адреса, первый узел 9 фор- мирования сигналов записи, первый узел 10 синхронизации, первую группу элементов И 11, вторую группу элементов И 12, второй узел 13 синхронизации, второй узел 14 формирования сигналов записи, первый 15 и второй 16 дешифраторы, первый 17 и второй 18 элементы НЕ, первый 19 и второй 20 элементы И, триггер 21, элемент ИЛИ 22.

Общая память состоит из первого 23, второго 24, и третьего 25 узлов памяти. Элементы микропроцессорных систем содержат первый узел 26 согла сования устройства для сопряжения с первой общей шиной 27 и второй узел 28 согласования устройства для сопряжения со второй общей шиной 29.

Узел синхронизации содержит (фиг, 6) элементы И 30-34, элементы НЕ 35-37, шинньш формирователь 38.

Узел формирования сигналов записи содержит (фиг. 7) элементы И 39 и 40 элементы НЕ 41 и 42, шинные формирователи 43 и 44.

Регистры 5 и 8 адреса и дешифраторы 6 и 7 адреса предназначены для запоминания и дешифрации адресов ячеек общей памяти. Дешифраторы адреса

представляют собой аналогичные схемы и обеспечивают дешифрацию трех старших разрядов А13-А15 адресного поля соответственно первой и второй микропроцессорных систем. Выход депшфратора Банк (Банк ) поступает на регистр адреса 5 (8), где запоминается совместно с младшими разрядами АО-А-12 адресного поля микропроцессорной системы 2 (3).

I . .

В устройстве младшие 13 адресов АО-А12 (АО -А12 ), предназначенные для прямой адресации данных внутри памяти (4К 16-разрядньгх слов), поступают непосредственно с узлов согласования на регистр адреса, 3 старших разряда А13-А15 (А13 -А15 ) после узла согласования первоначально поступают на дешифратор адреса (1 из 8) и

дальше запоминаются в регистре адреса. Запись в регистр осуществляется по переднему фронту сигнала КСИА. Та-- ким образом, на вход одного из разрядов первого регистра поступает сигнал

Банк, а после записи на его выходе появляется соответствующий ему сигнал Р Банк, который сохраняет свое значение до окончания цикла обмена. Для второго канала сигнала

Р Банк формируется аналогично. Временные диаграммы этого процесса для различных циклов представлены на фиг. 3 и 4. Кроме этого, на вход регистра адреса поступает сигнал

Разр. Г (Разр,2), разрешающий подачу адреса для выбора соответствующей ячейки общей памяти 4, от регистра 5 (8) адреса. На вход регистра поступает также сигнал КСБРОС

(КСБРОС ) с общей шины микропроцессорной системы 2 (3) для установки регистра в нулевое состояние. Выходной сигнал РАО (РАО ) регистра 5 (8) адреса поступает в узел 9 (14) формирования сигналов записи для указания с каким байтом информации (младшим или старшим) происходит обмен микропроцессорной системой 2 (3) при байтовых операциях. Выходные сигналы

РА1-РА10 и PAl -PA10 побитно объединяются и подаются непосредственно на общую память для адресации ячеек внутри узлов памяти 23-25. Объединение выходов регистров возможно.

ак как используются элементы с

. 1280643 сос.17 гр щи пе ны 15 с ры Р ге ме по по вы и об об ра Р

тоянием высокого импеданса. Выходные сигналы PAtI, РА12 (РМГ, РА12 ) и Р (Р Банк ) регистра 5 (8) адреса подаются на дешифратор 15 (16

Узел 10 (13) синхронизации предназначен для выработки сигнала управления направлением передачи данных, сигнала синхронизации пассивного устройства, сигнала стробирования записи и согласованного сигнала синхронизации активного устройства,

На вход узла 10 (13) синхронизаци поступает сигнал синхронизации актив ного устройства КСИА (КСИА ), пред- назйаченный для выработки сигнала синхронизации пассивного устройства КСИП (КСИП ). На другой вход узла синхронизации поступает сигнал КВВОД (КВВОД ) с общей шины 27 (29) микропроцессорной системы 2 (3), предназначенный для формирования сигналов чтения информации из общей памяти 4. На вход узла синхронизации поступает также сигнал КБЫВОД (КВЫВОд ) с общей шины микропроцессорной системы 2 (3), предназначенный для формирования сигналов записи информации в общую память 4, а также поступает сигнал Р Банк (Р Банк ) для разрешения формирования сигналов КСИП Разр. Зп, Пр/Пер, (КСИп , Разр. Зп , Пр/Пер ) в случае адресации общей памяти. Сигнал Разр. 1 (Разр. 2) служит для разрешения формирования сигналов КСИП, Разр.Зп

Пр/Пер - (КСИП , Разр. Зп , Пр/Пер ) в случае предоставления доступа микропроцессорной системы 2 (3) к Общей памяти 4. Выходной сигнал синхронизации пассивного уст - ройства КСИП (КСИП ) вырабатывается в ответ на сигналы КВВОД или КВЫВОД (КВВОД или КВЫВОД ) и является признаком, что данные приняты.. Выходной сигнал Разр. Зп (Разр. Зп ) предназначен для формирования сигналов записи информации в общую память. Вькодной сигнал Пр/Пер (Пр/Пер ) обеспечивает формирование сигнала управления направлением передачи информации между общей памятью и микропроцессорной системой 2 (3) при чтении или записи информации. Этот сигнал поступает на узел 26 (28) согласования микропроцессорной системы 2(3). Выходной сигнал СНА (СИА) поступает на элементы НЕ

л

.17 (18) и И 19 (20). На первые входы группы элементов И 11 и Т2, с.остоя- щих из 16 элементов 2 И каждый, на первые входы поступают выходные данные Д Вых.О-Д Вых.15 (Д Вых.о -Д Вых. 15) микропроцессорных систем 2 (3) с узлов 26 (28) согласования, а вторые входы стробируются сигналами Разр. 1 (Разр. 2) с выходов триггера 21. Выходные сигналы групп элементов И 11 и 12 .объединены попарно по схеме проводного ИЛИ за счет использования элементов с состоянием высокого импеданса (например К155Ш18) и подаются непосредственно на вход общей памяти 4. Дешифратор 15 (16) обеспечивает формирование сигналов разрешения выбора узлов 23-25 памяти Разр. УГ , Разр.У2, Разр. УЗ

I / и

(Разр. УГ, Разр.У2 , Разр.УЗ )

в выбранном банке общей памяти 4. На вход дешифратора 15 (16) поступают сигналы РАН, РА12 (РАп , РА12 ) регистра 5 (8) адреса, которые-представляют собой 11-е и 12-е разряды адресного поля общей шины 27 (29) микропроцессорных систем 2 (3). Кроме этого, дешифратор 15 (16) стро- бируется сигналом Р Банк (Р Банк )

с выхода регистра 5 (8) адреса. Первые выход дешифратора 15 Разр.У соединяется с первым выходом дешифратора 16 Разр.У (проводное ИЛИ) и поступает на узел 23 памяти общей памяти 4. Второй выход дешифратора 15 Разр.У2 аналогично соединяется с вторым выходом дешифратора 16 Разр. У2 (проводное ИЛИ) и подается на сегмент 24 общей памяти 4.- Третий

выход дешифратора 15 Разр.УЗ соединяется аналогично с третьим выходом дешифратора 16 Разр.УЗ (проводное ШШ) и поступает на сегмент 2 памяти общей памяти 4. Узел 9 (14) формирования сигнало записи предназначен для выработки записи информации ЗП1 (ЗП1 ) для младшего байта и ЗП2 (ЗП2 ) для старшего байта Информационных слов, поступающих с-микропроцессорной системы 2 (3) в общую память 4. При этом наличие активного значения сигнала КБАЙТ (КБАЙТ ). поступающего с микропроцессорной системы 2 (3) на вход узла 9 (14)

формирования, является признаком работы с байтами. На другой вход узла 9 (14) формирования поступает сигнал РАО.(РАО ) с регистра 5 (8) адреса, который определяет работу с

младшим или старшим байтами. Разрешение выдачи сигналов записи ЗП

У2 Разр.У2/; Разр..УЗ

ч /

ЗП2 (ЗПГ , ЗП2 ) РазрЛП (Разр. ЗП ) поступает .на вход разрешения записи узла 9 (14) формирования с выхода узла 10(13) синхронизации/ Элементы НЕ 17 и 18, элементы И 19 и 20 и треггер 21 обеспечивают формирование сигналов Разр., 2, поступающих на регистр 5 (8) адреса, узел 10 (13) синхронизации и группы элементов И И (12) для разрешения обмена информацией между микропроцессорной системой 2 (микропроцессорной системой 3) и общей памятью 4. Они исключают одновременную подачу сигналов Разр.1 и Разр,2, Сигналы синхронизации активных устройств СИА и СИА с выходов узлов 10 и 13 синхронизации поступают на соответствуюш;ие элементы НЕ Iv и 18, а также на первые входы элементов И 19 и 20, на вторые входы которых поступают сигналы с выходов НЕ 17 и 18. При CI L V СИА на выходе элемента И 19 вырабатыба- ется уцравляющий сигнал Упр.2, который обеспечивает формирование сигнала Разр.1 на единичном выходе триггера 21. При СИА VСИА на выходе И 20 формируется сигнал Упр.1 и формируется сигнал Разр,2 на нулевом выходе триггера 21. В начальный мо- который соответствует

При зтом выход Разр..У2 содержит два сигнала разрешения, т как второй узле памяти по объему в

5 2 раза больше чем первый или трети На выход записи/считывания первого узла 23 памяти поступает сигнал за писи только от второго узла 14 фор мирования сигналов записи. На вход

to записи/считывания узла 24 памяти п тупают сигналы записи как из узла формирования сигналов записи, так из узла 14. На вход записи/считыва ния третьего узла 25 памяти поступ

5 сигнал записи только от первого уз 9 формирования сигналов записи. Вы ход узлов 23-25 памяти Д Вх,0-Д Вх поступает на узль; 26 и 28 согласов ния микропроцессорных систем 2 и 3

20 Запрет записи информации в определ ные области общей памяти для микро процессорных систем позволяет повы сить информационную надежность.

- 5 Связь между двумя устройствами, подключенными к каналу, осуществля ся по принципу активньм - пассивны В любой момент времени только одно устройство является активным. Акти

0 ное устройство управляет циклами о ращения к каналу, обслуживает преры вания от внешних устройств и конт ролирует предоставление прямого до тупа к памяти. Пассивное устройств

NieHT времени,

СИА СИА 5 управляющие сигналы Упр. (например, память) является только

и Упр.2 не вырабатываются и триггер 21 может находиться в любом соснаходитьсятонкий. При СИА V СИА сигналы

Упр.1 вырабатываются и

и Упр.2 также не триггер 21 сохраняет свое предыдущее состояние. Элемент ИЛИ 22 обеспечивает формирование сигнала записи информации во второй узле 24 общей памяти 4 (ЗП1, ЗП2) (ЗП1 , ЗП2 ), который может поступать как от первого, так и второго узла формирования сигналов записи.

Общая память 4 состоит из первого 123, второго 24 и третьего 25 узлов памяти. На информационные входы узлов поступают данные с выходов групп элементов И 11 и 12 Д Вьгх.СО- Д ВЫХ.С15, на адресные входы узлов памяти поступает адрес с выхода регистра адреса РА1-РА10, на входы выборки узлов памяти поступают сигналы выбора узла с выхода дешифраторов

15 и 16 Разр.,У1

Разр.

806436

У2 Разр.У2/; Разр..

ч / И

При зтом выход Разр..У2 содержит два сигнала разрешения, так как второй узле памяти по объему в

5 2 раза больше чем первый или третий. На выход записи/считывания первого узла 23 памяти поступает сигнал записи только от второго узла 14 формирования сигналов записи. На вход

to записи/считывания узла 24 памяти поступают сигналы записи как из узла 9 формирования сигналов записи, так и из узла 14. На вход записи/считывания третьего узла 25 памяти поступает

5 сигнал записи только от первого узла 9 формирования сигналов записи. Выход узлов 23-25 памяти Д Вх,0-Д Вх.15 поступает на узль; 26 и 28 согласования микропроцессорных систем 2 и 3.

20 Запрет записи информации в определенные области общей памяти для микропроцессорных систем позволяет повысить информационную надежность.

Связь между двумя устройствами, подключенными к каналу, осуществляется по принципу активньм - пассивный. В любой момент времени только одно устройство является активным. Активное устройство управляет циклами обращения к каналу, обслуживает прерывания от внешних устройств и контролирует предоставление прямого доступа к памяти. Пассивное устройство

исполнительным устройством. Оно может принимать или передавать информацию только под управлением активного устройства .

40

Связь через канал замкнута, т.е. управляющий сигнал, передаваемый активным устройством, должен поступить на ответный сигнал от пассивного уст45 ройства. Поэтому процесс обмена между устройствами не зависит от длины канала и времени отклика пассивного устройства (в пределах 10 мкс). Асинхронное выполнение операций переда50 чи данных устраняет необходимость в тактовых импульсах. В результате этого обмен с устройством может происходр ть с максимально возможным для данного устройства быстродейст55 вием. Обмен между двумя устройствами может выполняться как 16-разрядными словами, так и байтами (8 разрядов). Общая шина обеспечивает три типа обмена данными - программный обмен.

обмен в режиме прямого доступа и обмен в режиме прерывания программы. В предлагаемом устройстве используется программынй обмен - передача данных по инициативе и под управлением программы. Конструктивно общая шина 27 (29) выполнена в виде печатной платы, обеспечивающей необходимые электрические соединения между контактами розеток, к которым подключают-fO программно по команде или при пусся различные устройства.

Как адрес, так и данные (слова или байты) передаются по одним и тем же 16-ти линиям адреса/данных КДА, Любой цикл обращения к каналу начинается с адресации пассивного устройства. После завершения адресной части цикла активное устройство выполняет прием или передачу данных, кото

рые выполняются асинхронно и требуют ответа от адресуемого устройства.

Функция синхронизации при передаче адреса и приеме/передаче данных выполняют сигналы управления каналом КСИА, КБАЙТ, КВВОД, КВЫВОД и КСИП.

Сигнал синхронизации активного устройства КСИА вырабатывается активным устройством. Передний фон этого- сигнала означает, что адрес находится на линиях КДА. Сигнал КСИА сохраняет активньй уровень до окончания текущего цикла обращения к каналам.

Сигнал синхронизации пассивного устройства КСИП информирует активное устройство о том, что данные приняты с линий КДА или данные установлены на информационных линиях. Этот сигнал вырабатывается в ответ на сигнал КВВОД и КВЫВОД. Сигнал КВВОД вы- рабатьшается во время действия сиг- нала КСИА и означает ввод данных по отношению к активному устройству. Он вырабатывается когда активное .устрой

ство готово принять данные от пассивного.

Сигнал КВЫВОД означает, что по отношению к активному устройству выполняется операция вывода, и на линиях КДА помещены истинные данные. Пассивное устройство, отвечая на сигнал КВЬЮОД, должно вырабатывать от- ветньм сигнал КСИП, чтобы завершить операцию передачи данных.

Сигнал вывода байта КБАЙТ используется в двух случаях: он вырабатывается в адресной части цикла для указания, что далее следует операция

вывода, а не ввода, и вырабатывается при передаче данных и цикле вывода для указания, что выводится байт..

Сигнал КСБРОС вырабатывается про- |цессором, чтобы выполнить начальную установку всех устройств, подключенных к каналу. Этот сигнал вырабатывается при каткдом включении питания. Этот же сигнал может вырабатываться

ке программы.

Для выполнения любой команды процессору требуется выполнить хотя бы одну операцию обращения к каналу. Для некоторых команд требуется выполнить несколько операций. Первой такой операцией для всех команд яв- ляется ввод данных из ячейки памяти. Если для выполнения команды не требуется обращаться за операндами к памяти или к внешним устройствам, дополнительных циклов канала не требуется. Если выполняется команда с обращением к памяти, то в этом случае могут выполняться любые из следующих циклов: ВВОД, ВВОД-ПАУЗА-ВЫВОД, ВЫВОД. Цикл ВВОД аналогичен операции считывания, цикл ВЫВОД - записи. Кроме того, цикл ВВОД-ПАУЗА-ВЫВОД включает ввод данных, выполнение арифметико-логических операций и вывод результата операции без повторений передачи адреса, т.е. результат записывается по адресу последнего выбранного операнда.

Цикл ВВОД. Направление передачи при. вьшолнении операций обмена данными определяется по отношению к активному устройству. При выполнении цикла ВВОД данные передаются от пассивного устройства к активному. Временная диаграмма выполнения цикла ВВОД представлена на фиг. 3. При этом в начальный момент времени Т( выполняется цикл обмена между общей памятью и микропроцессорной системой 2. После окончания этого цикла осуществляется обмен межну общей памятью и микропроцессорной системой 3 (начало в момент Т,). Во время прохожде

ния этого цикла в момент времени Тд начинается обмен между общей памятью и микропроцессорной системой 2. При этом после окончания адресной части цикла вырабатывается сигнал Разр. 1 только после окончания цикла обмена (снятие сигнала КСИА ) между общей памятью и системой 3. Цикл обмена

.- 25

между общей памятью и системой 2 при этом увеличивается на время Т,,; .

Порядок операций в режиме ВВОД следующий,

Система (активное устройство) в ад- 5 ресной части пе едает по линиям КДА адрес. Не менее чем через 150 не после установки адреса активное устройство вырабатывает сигнал КСИА, . предназначенный для запоминания адре-tO са во входной логике выбранного устройства. Пассивное устройство дешифрирует адрес и запоминает его. Актив- ioe устройство снимает адрес с линий КДА и вырабатывает сигнал КВВОД, сиг- 15 нализируя о том, что оно готово при- нять данные от пассивного устройства, и ожидает поступления сигнала КСИП. Пассивное устройство помещает данные на линии -КДА и вырабатывает сиг- 20 нал КСИП; сигнализирующий о том, что данные находятся в канале. Если сигнал КСИП не вырабатывается в течение 10 МКС после выработки сигнала КВВОД, то активное устройство системы переходит к обслуживанию внутреннего прерывания по ошибке обращения к шине. Активное устройство принимает сигнал КСИП, принимает данные, снимает сигнал КВВОД. Пассивное уст- -30 ройство снимает сигнал КСИП, завершая операцию передачи данных. Активное устройство снижает сигнал КСИА по заднему фронту сигнала КСИП, завершая тем самым цикл ВВОД. 35

Цикл ВЫВОД. Данные передаются от активного устройства к пассивному. Временная диаграмма выполнения цикла ВЫВОД представлена на фиг.4. Последовательность обмена в моменты 40 времени Т|, Т, Tj аналогична циклу ВВОД.

Порядок операций в режиме ВЫВОД с ле ующий.45Активное устройство в адресной части цикла передает по линиям КДА адресе. Не менее чем через 150 не после установки адреса вырабатывает- ся сигнал КСИА. Пассивное устрой- 50 ство дешифрует.адрес и запоминает его. Активное устройство снимает адрес с линии КДА. Активное устройство помещает данные на линии КДА и вырабатывает сигнал КВЫВОД, означаю- 55 щий, что на линиях ВДА помещены данные. Пассивное устройство принимеет данные с линий КДА и вырабатывает сигнал КСИП, означающий, что данные

приняты пассивным устройством. Если сигнал КСИП не вырабатывается в течение 10 мс после выработки сигнала КВЫВОД, то система переходит на обслуживание внутреннего прерывания по ошибке обращения к каналу. Активное устройство, получив сигнал КСИП, снимает сигнал КВЫВОД и через 250 не после поступления сигнала КСИП с линий КДА снимаются данные. Пассивное устройство снимает сигнал К€ИП, завершая операцию приема данных. Активное устройство снимает сигнал КСИА, завершая цикл шины ВЫВОД.

Сигнал КБАЙТ в части передачи данных может быть как пассивным, так и активным, определяя тем самым вывод 16-разрядного слова или вывод байта.

В цикле ВВОД-ПАУЗА-ВЫВОД адресная часть и ввод данных выполняется аналогично циклу ВВОД. Однако сигнал КСИА остается активным и после окончания ввода данных, что позволяет осуществлять вывод модифицированных данных без повторения адресной части цикла.

На фиг. 5 приведен алгоритм реализации циклов ВВОД и ВЫВОД, который соответствует описанным режимам ВВОД и ВЬ15ЮД.

НА фиг. 3 и 4 приведены временные диаграммы обмена информацией между активным устройством микропроцессорных систем 2 и 3 и устройством 1 для сопряжения микропроцессорных систем с общей памятью соответственно в режимах ВВОД и ВЫВОД. Одновременно оди из процессоров может функционировать в режиме ВВОД, а второй - в режиме ВЫВОД и наоборот. Кроме.этого, в режиме ожидания доступа к общей памяти может находиться как первая, так и вторая микропроцессорная системы.

Формула изобреения

1. Устройство для сопряжения двух микроэвм с общей памятью, содержащее два регистра адреса, два дешифратора адреса, две группы элементов И, причем установочные входы первого и второго регистров адреса являются входами устройства соответственно для подключения к установочным выходам первой и второй микроэвм, первые информационные входы первого и второго регистров адреса являются входами устройства для подключения к младшим

разрядам адресных выходов первой и второй микроэвм соответственно, входы первого и второго дешифраторов адреса яйляются адресными входами устройства для подключения к старшим разрядам адресных выходов первой и второй микроэвм, первые входы элементов И первой и второй групп образуют первую и вторую группы входов устройства для подключения к группам информационных выходов первой и второй микроэвм соответственно, группа младших разрядов информационных выходов первого и второго регистров адреса образует группу выходов устройства для подключения к группе адресных входов общей памяти, выходы элементов И первой и второй групп образуют группу выходов устройства для подключения к группе информационных входов общей памяти, входы записи пе первого и второго регистров адреса являются входами устройства для подключения к синхровыходам первой и

второй микроэвм, при этом выходы пер I

вого и второго дешифраторов адреса соединены с вторыми информационными входами первого и второго регистров адреса соответственно, отличающееся тем, что, с це- лью увеличения быстродействия, в устройство введены два узла синхронизации, два узла формирования сигналов записи, два дешифратора, триггер

два элемента И, два элемента НЕ, элемент ИЛИ, причем входы запуска первого и второго узлов формирования ей:- налов записи являются входами устройства для подключения к выходам фор- мата даниых первой и второй микроЭВМ соответственно, первые и вторые вход запуска первого и второго узлов синхронизации являются входами устройства для подключения к выходам ввода и вывода первой и : торой микро- ЭВМ соответственно, первые синхровы- ходы первого и второго узлов синхронизации являются выходами устройства для подключения к синхровходам первой и второй микроэвм соответственно выход первого узла формирования сигналов .записи соединен с первым входом элемента ИЛИ и является выходом устройства для подключения к первому входу записи-чтения общей памяти, выход второго узла формирования сигналов записи соединен с вторым входом элемента ИЛИ и является выходом

устройства для подключения к второму входу записи-чтения общей памяти,- выход элемента ИЛИ является выходом устройства для подключения к третьему входу записи-чтения общей памяти, первые, вторые и третьи выходы первого и второго дешифраторов являются выходами устройства для подключения к первому, второму и третьему входам выборки общей памяти соответственно, вторые синхровыходы первого и второго узлов синхронизации являются выходами устройства для подключения к входам приема-передачи первой и второй микроэвм соответственно, при этом первые информационные выходы первого и второго регистров адреса сое- динены с информационными входами первого и второго узлов формирования сигналов записи соответственно, входы разрешения записи которых соединены с третьими синхровыходами первого и второго узлов синхронизации соответственно, четвертые синхровыходы которых соединены с входами первого и второго элементов НЕ соответственно и с первыми входами первого и второго элементов И соответственно, выходы которых соединены с единичным и нулевым входами триггера соответственно, единичньш и нулевой выходы которого соединены с вторыми входами элементов И первой и второй групп соответственно, с входами блокировки первого к второго узлов синхронизации соответственно, с разрешающими входами первого и второго

5

п 5-

0

регистров адреса, соответственно, группы старших разрядов информационных выходов которых соединены с группами информационных входов первого и второго дешифраторов соответственно, стробирующие входы которых соединены с вторыми информационными выходами первого и второго регистров . адреса соответственно, и с первыми синхровходами первого и второго узлов синхронизации соответственно, вторые синхровходы которых соединены с входами записи первого и второго регистров адреса соответственно, выходы первого и второго элементов НЕ соединены с вторыми входами второго и первого элементов И соответственно.

2. Устройство по п. 1, отличающееся тем, что узел формирования сигналов записи содержит два элемента И, два элемента НЕ и два шинных формирователя, выходы ко13

торьгх образуют выход узла, а управляющие входы объединены и являются входом разрешения записи узла, выходы первого и второго элементов И соединены соответственно с информационными входами первого и второго шинных формирователей, первые входы первого и второго элементов И соединены

0643

14

с выходом первого элемента НЕ, вход которого является входом запуска узла, второй вход первого элемента И соединен с выходом второго элемента г НЕ, вход которого и второй вход второго элемента И объединены и являются информационным входом узда.

фиг. 7

фие. 2

«. у

X2I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух микроЭВМ с общей памятью | 1988 |

|

SU1674141A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1984 |

|

SU1211744A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1988 |

|

SU1524062A2 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1605239A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство управления обменом информацией между ЭВМ и внешним устройством | 1986 |

|

SU1413639A1 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

Изобретение относится к вычислительной технике и предназначено для использования в микропроцессорных системах, содержащих два процессора Основной целью изобретения является увеличение быстродействия при использовании общей памяти с одновременным упрощением протоколов обмена между микропроцессорными системами и общей памятью, причем одновременно один из процессоров может функционировать в режиме ВВОД, а второй - в режиме ВЫВОД, и наоборот. Устройство содержит два регистра адреса, два дешифратора адреса, две группы элементов И, два узла синхронизации, два узла формирования сигналов записи, два дешифратора, два элемента И, два элемента НЕ, триггер, элемент ИЛИ 1 з.п. ф-лы, 7 ил. S (Л ю 00 о 4 СО

.ХШЕ-ИУ

-.цробеньсимолане имеет значении

CPf/e.J

КСКА KBblBOff

KClfft

квмт

PA3PJ

хз:

г

- -

ОС /ь7/та

Г2

JLI-ZX.

с

ум9емь cutHOjro Heitneem

ОС /ь7/та X аАнные

Г2

-Kz:

Фие.

f/l/C J

Nk

fJejoe avar yo jOffcaf

/70 /(/i

6A// aS /77/ca

3oeffOfff/ a//f/e a /fsccf

C fj /TJifff

сс/гма c/npoSu/}o awi

дь/dai/a a/wA/jf O/17 ffof/f i/ ffa

/CC

дь/ffai/a ff/r frpffifeccff/ a a

/(

ПЛ oSpaSofffff/ ifiy ffS/ aufew /ra

ф1/е// a// 3dff

fj/yt/e CM/, с л/frt/f КВЫдОД и дамммг

Cffff/m/f да МА/х

fPus.S

C///f/77 /e /ггх/7

A

С

Сп7О/7

Разр ЗЛ

фиа.е

| Маршан М.А., Балдо Дж., Конте Дж | |||

| Сравнение различных одно- шинных микропроцессорных архитектур по их производительности | |||

| Экспресс- информация Вычислительная техника, 1983, № 40, с | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Патент США № 4325116, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-04-05—Подача