Изобретение относится к вычислительной технике и предназначено для использования в микропроцессорных системах, содержащих два процессора.

Цель изобретения -увеличение быстродействия устройства при работе с общей памятью.

На фиг. 1 и 2 изображены функциональная схема устройства для сопряжения микропроцессорных систем с общей памятью, элементы микропроцессорных систем и обща. память; на фиг.З - схема узла cw. xpo- чизации; на фиг.4 - схема узла формирования сигналов записи; на фиг.5 схема узла формирования сигналов разрешения.

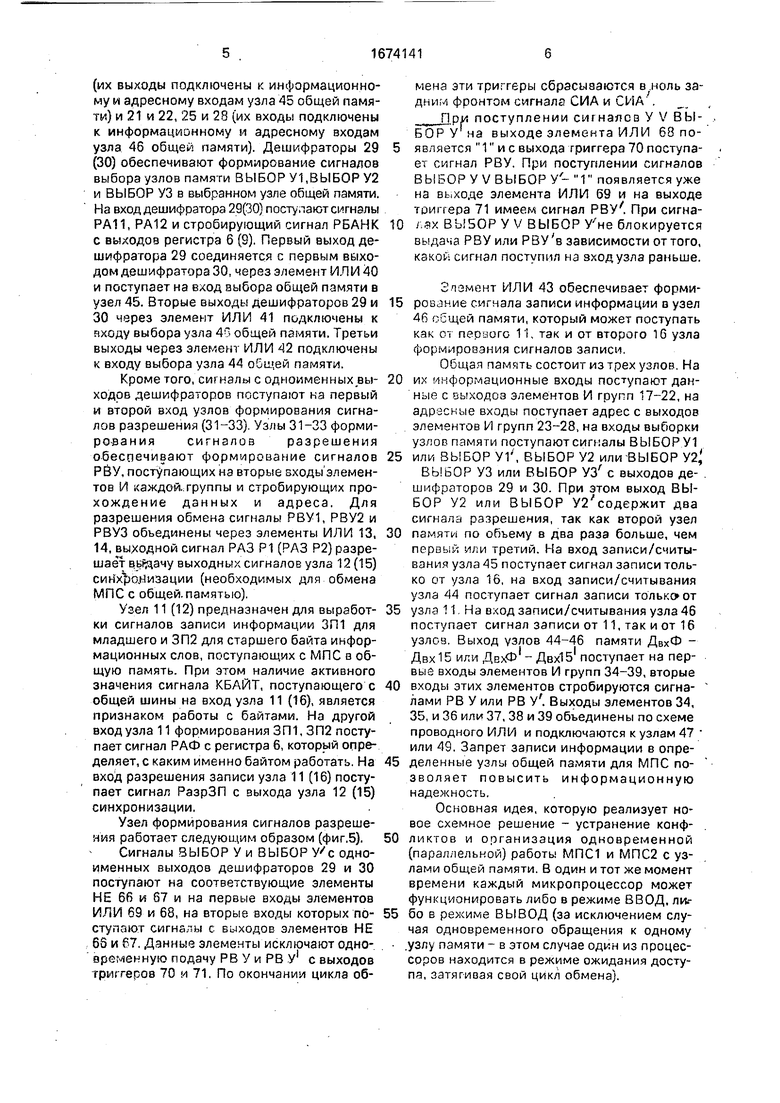

Устройство 1 дли сопряжения микропроцессорных систем 2 и 3 с общей памятью 4 содержит (фиг,1 и 2) второй элемент ИЛИ 5, первый регистр 6 адреса, первый 7 и второй 8 дешифраторы адреса, второй регистр 9 адреса, третий элемент ИЛИ 10. первый узел 11 формирования сигналов записи, первый узел 12 синхронизации, седьмой и восьмой элементы ИЛИ 13, 14, второй узел 15 синхронизации, второй узел 16 формирования сигналов записи, с первой по двенадцатую группы элементов И 17-28, первый 29 и второй 30 дешифраторы, узлы 31-33 узлы

io 1

формирования сигналов разрешения, три- надцатую-восемнадцатую группы 34-39 элементов И, четвертый-шестой и первый 40-43 элементы ИЛИ.

Общая память состоит из первого 44, второго 45 и третьего 46 узлов памяти. Элементы микропроцессорных систем содержат первый узел 47 согласования устройства для сопряжения с первой общей шиной 48 .и второй узел 49 согласования устройства для сопряжения со второй общей шиной 50.

Узел синхронизации содержит (фиг.З) элементы И 51-55, элементы НЕ 56-58, шинный формирователь 59.

Узел формирования сигналов записи содержит (фиг.4) элементы И 60-61, элементы НЕ 62 и 63, шинные формирователи 64 и 65.

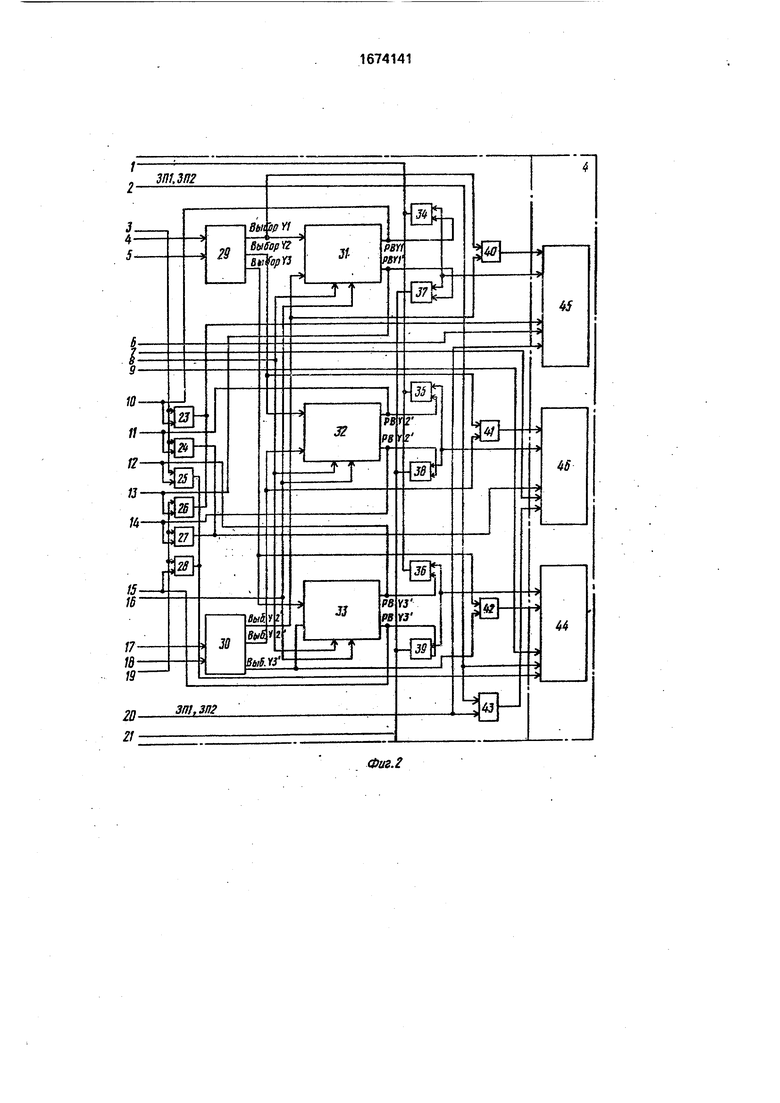

Узел формирования сигналов разрешения содержит (фиг.5) элементы НЕ 66 и 67, элементы ИЛИ 68 и 69 и триггеры 70 и 71.

Регистры 6 и 9 адреса и дешифраторы 7 и 8 адреса предназначены для запоминания и дешифрации адресов ячеек общей памяти. Дешифраторы адреса обеспечивают дешифрацию трех старших разрядов А13-А15 адресного поля соответственно первой и второй микропроцессорных систем. Выход дешифратора БАНК (Банк) поступает на регистр 6 (9) адреса, где запоминается совместно с младшими разрядами АФ-А12 адресного поля микропроцессорной системы 2 (3).

В устройстве младшие 13 адресов АФ- А12 (АФ-А12), предназначенные для прямой адресации данных внутри памяти (4К16 - разрядных слов), поступают непосредственно с узлов 47 (49) согласования на регистры 6 (9) адреса. Запись в регистр осуществляется по переднему фронту сигнала КСИА. Таким образом, на вход одного из разрядов регистра адреса поступает сигнал БАНК, а после записи его на выходе появляется соответствующий ему сигнал РБАНК, который сохраняет свое значение до окончания цикла обмена. Для второго канала сигнал РБАНК формируется аналогично. Кроме того, на вход разрешения регистра адреса поступает сигнал 1, который поддерживает регистр в открытом состоянии, разрешая подачу адреса для выбора, соответствующей ячейки общей памяти. На вход регистра 6 поступает также сигнал с выхода элемента ИЛИ 5 для начальной установки регистра канальным сигналом КСБРОС с общей шины или СИА с выхода узла 12 синхронизации (по окончании цикла обращения к памяти задний

Фронт СИА устанавливает регистр адреса в ноль

Выходной сигнал РАФ с регистра адреса поступает в узел 11 (16) формирования сигналов записи для указания, с каким байтом информации (младшим или старшим) происходит обмен при байтовых операциях. Выходные сигналы РА1-РА10 поступают на первые входы элементов И групп 23-25. Вы0 ходные сигналы регистра 6 РА11, РА12 и РБАНК подаются на дешифраторы 29 (30).

Узел 12 (15) синхронизации предназначен для выработки сигнала управления направлением передачи данных ПРПер,

5 сигнала КСИП, сигнала разрешения записи РазрЗП для узла 11 (16) и согласованного сигнала СИА-КСИА.

На вход узла 12 (15) синхронизации поступает сигнал КСИА, предназначенный для

0 выработки сигнала КСИП.

На его другой вход поступает сигнал КВВОД (КВЫВОД) с общей шины 48 (50) МПС 2 (3), предназначенный для формирования сигналов чтения (записи) информации

5 из общей памяти 4 (в общую память). На вход узла 12 (15) поступает также сигнал РБАНК для разрешения формирования сигналов КСИП, РазрЗП, ПР/Перв в случае адресации общей памяти. Сигнал Разр1

0 служит для разрешения формирования данных сигналов в случае предоставления доступа к общей памяти. Выходной сигнал КСИП вырабатывается в ответ на КВВОД и КВЫВОД и является признаком того, что

5 данные приняты. Выходной сигнал РазрЗП предназначен для формирования сигналов записи информации в общую память. Выходной сигнал ПР/Пер обеспечивает формирование сигнала управления

0 направлением передачи данных между МПС и общей памятью при чтении или записи информации. Этот сигнал поступает на узел 47 (49) согласования. Выходной сигнал СИА поступает на первые входы установки

5 первого-третьего 31-33 узлов формирования сигналов разрешения. На первые входы элементов И групп 17, 19 21 поступают выходные данные с блока 47. Каждая группа состоит из 16 элементов И. Первые входы

0 этих элементов стробируются сигналами разрешения выбора узла (РВУ) с первых выходов узлов 31-33 формирования сигналов разрешения. Выходные сигналы групп элементов И 17 и 18,23 и 26 объединены попар5 но по схеме проводного ИЛИ за счет использования элементов с состоянием высокого импеданса и подаются непосредственно на информационный и адресный входы узла 44 общей памяти.-Аналогичным образом включены группы 19 и 20, 24 и 27

(их выходы подключены к информационному и адресному входам узла 45 сбщей памяти) и 21 и 22, 25 и 2Я (их входы подключены к информационному и адресному входам узла 46 , памяти). Дешифраторы 29 (30) обеспечивают формирование сигналов выбора узлов памяти ВЫБОР У1,ВЫБОР У2 и ВЫБОР УЗ в выбранном узле общей тмяти. На вход дешифратора 29(30) постулэютсигнроы РА11, РА12 и стробирующий сигнал РБАНК с выходов регистра 6 (9). Первый выход дешифратора 29 соединяется с первым выхо дом дешифратора 30, через элемент И ПИ 40 и поступает на вход выбора оОщей пзмчти в узеп 45. Вторые выходы дешифратор 29 и 30 через элемент ИЛИ 41 подключены к ходу выбора узла 4 общей памяти. Третьи выходы через элемот ИЛИ 42 подключены к входу выбора узпа 44 оСи ей памяти.

Кроме того, от налы с сдноимснны/, в; ходов дешифраторов поступают ь-j лериий и второй вход узлов формирования сигналов разрешения (31-33) Узлы 31-33 формирования сигналов разрешения обеспечивают формирование сиголов РВУ, поступающих на вторые зходы элементов И каждой, группы и стробирующ х прохождение данных и адреса. Для разрешения обмена сигналы РВУ1, Р8У2 и РВУЗ объединены через элементы ИЛИ 13, 14, выходной сигнал РАЗ Р1 (РАЗ Р2) разрешает выдачу выходных сигналов узла 1 (15) син/ оЯизации (необходимых для обмена МПС с общей.памятью).

зел 11 (12) предназначен для выработки сигналов записи информации ЗП1 для младшего и ЗП2 для старшего байта информационных слов, поступающих с МПС и общую память. При том наличие активного значения сигнала КБАЙТ, поступающего с общей шины на вход узла 11 (16) является признаком работы с байтами. На другой вход узла 11 формирования ЗП1, ЗП2 поступает сигнал РАФ с регистра 6, который определяет, с эким именно байтом работать. На вход разрешения записи узла 11 (16) поступает сигнал РазрЗП с выхода узла 1 (15) синхронизации.

Узел формирования сигналов разрешения работает следующим образом (фиг.5).

Сигналы ВЫБОР У и ВЫБОР Ус одноименных выходов дешифраторов 29 и 30 посгупают на соответствующие элементы НЕ 66 и 67 и на первые входы элементов 69 и 63, на вторые входы которых по- сту.Г Юг сигня ы с выходов элементов НС 60 и Г7. Дзнны э элементы исключают одно- чр чениую подачу РВ У и РВ У с выходов ipi-1, гегсэ 70 и 71. По окончании цикпз обмена эти триггеры сбрасываются в ноль задним фронтом сигналя СИА и СНА

При поступлении сигналов У V ВЫБОР У на выходе элемента ИЛИ 68 по5 является 1 и с выхода триггера 70 поступаем сигнал РВУ. При поступлении сигналов ВЫБОР У V ВЫБОР V- 1 появляется уже на вьходе элемента ИЛИ 69 и на выходе тиипера 71 имеем сигнал РВУ . При сигна0 i 9х ВЫБОР У V ВЫБОР Уне блокируется выдача РВУ или РВУ в зависимости от того, кзкоЈ1 сигнал поступил нэ зход узла раньше.

Элемент ИЛИ 43 обеспсчипает форми5 роюние сигнала записи информации о узел 4 г С щей памяти, который может поступать кчк ci первого 11. так и от второго 16 узла формировэниясигналов записи.

Общая памчти состоит из трех узлон. На

0 их информационные входы поступают данное с выходов элементов И royt п 17-22, на адресные входы поступает адрес с выходов элементов И групп 23-28, на входы выборки yjfiOD памяти поступают сигналы ВЫБОР У1

5 или ВЫБОР УГ, ВЫБОР У2 или ВЫБОР У2, BolbOP УЗ или ВЫБОР УЗ с выходов дешифраторов 29 и 30. При этом выход ВЫБОР У2 или ВЫБОР У2 содгржит два сигнала разрешения, так как второй узел

0 памяти по объему в два раза больше, чем порвь.й или третий. На вход записи/считывания узла 45 поступает сигнал записи только от узла 16, на вход записи/считывания узла 44 поступает сигнал записи только от

5 узла 11 На вход записи/считывания узла 46 поступает сигнал записи от 11. так и от 16 узлов. Выход узлов 44-46 памяти ДВхФ - Двх1Б или Двхф Двх15 nociynaeT на первые входы элементов И групп 34-39, вторые

0 входы этих элементов стробируются сигналами РВ У или РВ У . Выходы элементов 34. 35, и 36 или 37, 38 и 39 объединены по схеме проводного ИЛИ и подключаются к узлам 47 или 49. Запрет записи информации в опре5 деленные узлы общей памяти для МПС позволяет повысить информационную надежность.

Основная идея, которую реализует новое схемное решение - устранение конф0 ликтов и организация одновременной (параллельной) работы МПС1 и МПС2 с узлами общей памяти. В один и тот же момент времени каждый микропроцессор может функционировать либо в режиме ВВОД, лиг

5 бо в режиме ВЫВОД (за исключением случая одновременного обращения к одному узлу памяти - в этом случае один из процессоров находится в режиме ожидания доступа, затягивая свой цикл обмена).

В устройстве конфликт между процессорами устраняется тем, что сигналы РАЗР1 и РАЗР2 формируются в ответ на выходные сигналы дешифраторов 29 и 30 соответственно, которые вырабатываются только при обращении МПС к общей памяти. Сигнал СИА с выхода узла 12 (15) синхронизации теперь подается на вход элемента ИЛИ 5 (10), где вместе с канальным сигналом КСБРОС формируется сигнал обнуления регистра 6 (9) адреса. Это необходимо для того, чтобы по окончании цикла обмена сбросить сигналы Р БАНК и ВЫБОР У и задним фронтом сигнала СИА сбросить сигналы РВ У с выходов узлов формирования сигналов разрешения и соответственно сигнала РАЗР1 (РАЗР2).

На разрешающий вход регистра адреса подается сигнал 1, поддерживая регистр постоянно в открытом состоянии. Это возможно, так как обеспечена одновременная работа обеих МПС с общей памятью - адреса и данные разделены в группах элементов И, их прохождение стробируется сигналами РВУ.

Выходные сигналы дешифраторов 29 и 30 ВЫБОР У с одноименных выходов подаются на входы узлов формирования сигналов разрешения (РВ У). Данные узлы запрещают одновременную выдачу сигналов разрешения выбора одного и того же узла памяти. Так как при нулевых сигналах на обоих входах триггера он может находиться в любом из своих состояний (запоминает предшествующую информацию), то на одном из единичных выходов узлов 31 -33 от предшествующих циклов обмена сохраняется 1 (что соответствует наличию сигнала РВ У и, следовательно, и РАЗР). Это приводит к появлению сигнала КСИП на выходе узла 12 (15) синхронизации, как реакция на появление сигнала КВВОД или КВВЫВОД, даже если обмен МПС с общей памятью не происходит. В этом случае КСИП является признаком ложной установки данных на линиях КДА, Чтобы избежать этого, необходимо после каждого цикли обмена сбрасывать содержимое триггера - это возможно при добавлении в узел еще одного триггера. Если на входы установки триггеров подать сигналы СИА и СИА соответственно с выходов узлов 12 (15) синхронизации, то задний фронт этих сигналов будет сбрасывать выходные сигналы РВ У и соответственно РАЗР.

Группы элементов И 17-22 и 23 - 28 предназначены для передачи данных с линий КДА каждой МПС выбранному блоку памяти, а также для передачи адреса s соответствии с сигналами ВЫБОР У и РВ У,

последний из этих сигналов стробирует прохождение данных и адреса. Поскольку каждый дешифратор 29 и 30 вырабатывает по 3 сигнала ВЫБОР У( по числу узлов памяти) и

соответственно этим сигналам вырабатывается 6 (по 3 для каждой МПС) сигналов в РВ У, то для мультиплексирования данных или адреса требуется 6 групп элементов И. Раздельная передача данных и адреса

0 каждому узлу общей памяти необходима, чтобы обеспечить возможность одновременной работы каждой МПС с памятью.

Появление групп И 34-39 в полном соответствии с изложенным объясняется не5 обходимостью раздельного поступления данных на КДА каждой МПС от любого узла общей памяти, что обеспечивает возможность параллельной работы МПС с общей памятью.

0 Элементы ИЛИ 40-42 необходимы для того, чтобы подать на вход выбора кристалла каждого узла общей памяти один из двух сигналов: ВЫБОР У или ВЫБОР У;. Схема просюдного ИЛИ здесь не годится, так как

5 эти сигналы в то жо время подаются на разные входы узлов 31-33 формирования сигналов разрешения.

Связь между двумя устройствами, подключенными к каналу, осуществляется по

0 принципу активный-пассивный. Активное устройство управляет циклами обращения к каналу, обслуживает прерывания от внешних устройств и контролирует предоставление прямого доступа к памяти. Пассивное

5 устройство (например, память) является только исполнительным устройством. Оно может принимать или передавать информацию только под управлением активного устройства.

0 Связь через канал замкнута, т.е. управляющий сигнал, передаваемый активным устройством, должен поступить на ответный сигнал от пассивного устройства. Поэтому процесс обмена между устройствами не за5 висит от длины канала и времени отклика пассивного устройства. Асинхронное выполнение операций передачи данных устраняет необходимость в тактовых импульсах. В результате этого обмен с каждым устрой0 ством может происходит с максимально возможным для данного устройства быстродействием. Обмен между двумя устройствами может выполняться как 16-разрядными словами, так и байтами (8 разрядов).

5В устройстве используется программный обмен - передача данных по инициативе и под управлением программы .

Как адрес, так и данные передаются по одним и тем же 16 линиям адреса-данных

КДА. Любой цикл обращения к каналу начинается с адресации пассивного устройства. После завершения адресной части цикла активное устройство выполняет прием или передачу данных, которые выполняются асинхронно и требуют от адресуемого устройства.

Для выполнения любой команды процессору требуется выполнить хотя бы одну операцию обращения к каналу. Для некоторых команд требуется выполнение нескольких операций. Первой такой операцией является ввод данных из ячейки памяти. Если для выполнения команды не требуется обращаться за операндами к памяти или к внешним устройствам, дополнительных циклов канала не требуется. Если выполняется команда с обращением к памяти, то в этом случае могут выполняться любые из следующих циклов: ВВОД. ВВОД-ПАУЗА- ВЫВОД, ВЫВОД. Цикл ВВОД аналогичен операции считывания, цикл ВЫВОД/зэпи- си. Кроме того, цикл ВВОД-ПАУЗА-ВЫВОД включает ввод данных, выполнение арифметико-логических операций и вывод результата операции без повторений передачи адреса, т.е. результат записывается по адресу последнего выбранного операнда.

Цикл ВВОД. Направление передачи при выполнении операций обмена данными определяется по отношению к активному устройству. При выполнении цикла ВВОД данные передаются от пассивного устройства к активному. При этом в один момент времени могут начать обмен с общей памятью обе МПС. При обращении к разным узлам памяти обмен происходит параллельно. Если происходит обращение к одному узлу памяти (например, к первому), то обмен продолжает тот процессор, который раньше выработал сигнал ВЫБОР У (1) (т.е. первым начал обмен), другой же вынужден продлевать свой цикл обращения к данному узлу памяти и лишь после завершения цикла обмена первым процессором получает доступ к данному узлу, завершая цикл обмена с ним.

Порядок операций в режиме ВВОД следующий.. Система (активное устройство) в адресной части передает по линиям КДА адрес. Не менее чем через 150 не после установки адреса активное устройство вырабатывает сигнал КСИА, предназначенный для запоминания адреса во входной логике выбранного устройства.

Пассивное устройство дешифрирует адрес и запоминает его. Прохождение адреса от активного устройства к пассивному обеспечивается сигналами ВЫБОР У, РВ У и РАЗР1, которые вырабатываются с приходом КСИА. Активное устройство снимает ад-.

рее с линий КДА и вырабатывает сигнал KB ВОД, сигнализируя о том, что оно готово принять данные от пассивного устройства и ожидает поступления КСИП Пассивное уст- 5 ройство помещает данные по линии КДА и вырабатывает КСИП, сигнализирующий о юм, что данные находятся в канале. Активное устройство принимает КСИП, принимает данные, снимает сигнал КВВОД.

0 Пассивное устройство снимает сигнал КСИП, завершая операцию передачи данных. Активное устройство снимает сигнал КСИА, завершая цикл В ВОД (одновременно снимгет сигнал ВЫБОР У).

5 Цикл ВЫВОД. Данные передаются от активного устройства к пассивному. Последовательность обмена аналогична ииклу ВВОД. Порядок операций в режиме ВЫВОД следующий.

0 Активное устройство передает в адресный части цикл по линиям КДА адрес. Не менее чем через 150 не после установки адреса вырабатывается сигнал КСИА. По его переднему фронту вырабатываются сигна5 лы ВЫБОР У, РВ У и РАЗР1, разрешающие прохождение адреса к пассивному устройству. Пассивное устройство дешифрирует адрес и запоминает его. Активное устройство снимает адрес с линий КДА, помещает на

0 них данные и вырабатывает сигнал КВЫ- ВОД, означающий, что на КДА помещены данные. Пассивное устройство принимает данные с линий КДА и вырабатывает сигнал КСИП, означающий, что данные приняты

5 пассивным устройством. Активное устройство, получив сигнал КСИП. снимает сигнал КВЫВОД и через 250 не после поступления КСИП с линий КДА снимаются данные. Пассивное устройство снимает сигнал КСИП.

0 завершая операцию приема данных. Активное устройство снимает сигнал КСИА. завершая цикл ВЫВОД.

Сигнал КБАЙТ в части передачи данных, может быть как активным, так и пассивным,

5 определяя тем самым вывод 16-разрядного слова или байта.

Формула изобретения 1. Устройство для сопряжения двух мик- роЭВМ с общей памятью, содержащее два

0 регистра адреса, два дешифратора адреса, две группы элементов И, два узла синхронизации, два дешифратора, два узла формирования сигналов записи, элемент ИЛИ, причем первые информационные входы

5 первого и второго регистров адреса являются входами устройства для подключения к младшим разрядам адресных выходов первой и второй микроЭВМ соответственно, входы первого и второго дешифраторов адреса являются адресными входами устройства для подключения к старшим разрядам адресных выходов первой и второй микро- ЭВМ, первые входы элементов И первой и второй групп образуют первую и вторую группу информационных входов устройства для подключения к группам информационных выходов первой и второй микроЭВМ соответственно, входы записи первого и второго регистров адреса являются синх- ровходами устройства для подключения к синхровыходам первой и второй микро- ЭВМ, выходы первого и второго дешифраторов адреса соединены с вторыми информационными входами первого и второго регистров адреса соответственно, вхо- ды запуска первого и второго узлов формирования сигналов записи являются входами устройства для подключения к выходам формата данных первой и второй микроЭВМ соответственно, первый и вто- рой входы запуска первого и второго узлов синхронизации являются выходами устройства для подключения к выходам ввода и вывода первой и второй микроЭВМ соответственно, первые выходы первого и второго узлов синхронизации являются выходами устройства для подключения к синхровхо- дам первой и второй микроЭВМ соответственно, выход первого узла формирования сигналов записи соединен с первым входом первого элемента ИЛИ и является выходом устройства для подключения к входу записи-чтения первого узла общей памяти, выход второго узла формирования сигналов записи соединен с вторым входом первого элемента ИЛИ и является выходом устройства Для подключения к входу записи-чтения второго узла общей памяти, выход первого элемента ИЛИ является выходом устройства для подключения к входу запи- си-чтения третьего узла общей памяти, вторые выходы первого и второго узлов синхронизации являются выходами устройства для подключения к входам приема-передачи первой и второй микроЭВМ соответственно, первые выходы первого и второго регистров адреса соединены с информационными входами первого и второго узлов формирования сигналов записи соответственно, входы разрешения записи кото- рых соединены с третьими выходами первого и второго узлов синхронизации со- ответственно, группа старших разрядов информационных выходов регистров адреса соединена с группами информационных входов первого и второго дешпфра горов соответственно, стробирующие входы которых соединены с вторыми выходами первого и второго регистров адресч соответственно и с входами разрешения перво

го и вк рого узпов синхронизации соответ- стзенно, синхровходы которых соединены с синхровходами устройства отличающееся тем, что, с целью увеличения быстродействия при использовании общей памяти, в устройство введены семь элементов ИЛИ, шестнадцать групп элементов И, три узла формирования сигналов разрешения, при этом разрешающие входы первого и второго регистров адреса соединены с шиной единичного потенциала устройства, установочные входы первого и второго регистров адреса соединены с выходами втоосго и третьего элементов ИЛИ соответственно, первые входы которых являются входами устройства соответственно для подключения к установочным выходам персой и второй микроЭВМ, а вторые входы соединены соответственно с третьими выходами узлов синхронизации, третий вылод первого узла синхронизации соединен с первыми установочными входами первого, второго третьего узлов формировчния сигналов разрешения, а третий выход второго узла синхронизации - с вторыми установочными входами узлов формирования сигналов разрешения, первые входы первого, второго и третьего узлов формирования сигналов разрешения соединены соответственно с первым, вторым и третьим выходами первого дешифратора, а вторые входы первого, второго и третьего узлов формирования сигналов разрешения соединены соответственно с первым, вторым и третьим выходами второго дешифратора, первые выходы первого и второго дешифраторов через четвертый элемент ИЛИ соединены с первым входом выборки второго узла общей памяти, вторые выходы первого и второго дешифраторов соединены через пятый элемент ИЛИ с входом аыборки третьего узла общей памяти, третьи выходы первого и второго дешифраторов соединены через шестой элемент ИЛИ с входом выборки первого узла общей памяти, первые входы элементов И третьей и четвертой групп подключены к первой и второй группам информационных Е1ходов устройства соответственно, первые входы элементов И пятой и шестой групп подключены к порвой и второй группам информационных вводов устройства, группа выходов младших разрядов первого регистра адреса соединена с первыми входами элементов И седьмой, ведьмой и девятой групп, группа ВЫХОДОР младших разпядов второго регистра адреса соединена с первыми входами злемечгов И десятой, одиннадцати и двенадцатой групп, пераый выход пераого узл Ф армирования сигналов разрешения соеди- нем с вторыми входами элементов И первой,

седьмой и тринадцати . рупп ii лерьым в -о- дом селимого элемента ИЛИ, л-г/сд второго узла формирования сы идлов разрешения соединен с вторыми входами элемен тов И третьей, чосьмой и четырнадцатой групп и вторым входом седьмого элемента ИЛИ, первый выход третьего узла формирование сигналов разрешения соединен с вторыми входами элементов И пятой, девятой и пятнадцатой групп и третьим входом седь мого элемента ИЛИ вь,,;од которого соеди ней с разрешающим входом первого снгг ронизации второй г,ыход перво-о узла формирования сигналов ра рошения roe/in- нен г. вторыми входами элементов И вгорог, десятой и шестнадцатой групп и первым входом вгк.ьмого элемента ИЛИ, второй ы- ход огорого уз та формирован с и г на, ов разрешения соединен с вторыми вход. ии элементов И четвертой, одчмпэдцэтоj , семнадцатой групп и вторым входом вось мог;, элемента ИЛИ втопой выход третьего узла Формирования сигналов разрешения соединен с вторыми входами эл ментов И шестой, двенадцатой и восемнадцатой групп и третьим входом восьмою элемежа ИЛИ, выход которого соединен с разрешающим входом второго узла синхронизации, выходы элементов И первой и второй гру,.п образуют группу выходов устройства для подключения к группе информационных входов второго узла общей памяти, выходы алиментов И тринадцатой и шестнадцатой групп образуют группу выходов устройства для подключения к группе адресных входов второго узла общей памяти, выходы элементов И третьей и четвертой групп образуют группу выходов устройства для подключения к группе информационных входов третьего узла общей памяти, выходы элементов И четырнадцатой и семнадцатой групп образуют группу выходов устройства для подключения к группе адресных входов третьего узла общей памяш, выходы элементов И пятой и шестой групп образуют группу выходов устройства для подключения к группе информационных входов пербоч У,ЛС общей памяти, выходы элементов I пятнадцатой восемнадцатой i рупп образ/ют группу f ыходоч /строиства для подключения к группеадресн.,л входов первого узла памяти, группа г-хсдоз устройства для подключения к группе информационных выходов оторого узла общой памяти соединена с первыми входами элементов И i-едьмой и восьмой групп, группа входов ус0 пойства для подключения к группе инфор- мг- ,ионных заходов третьего узла общей nar.iKtv соединена с перзыгим входами элементов И девятой и десятой групп, группа ВУОДСГ vcrpouc oa wa подключения к груп пь информационных выходов первого узла об цей ПЗМРТИ соединена с первыми входа- ЭЛСГ- НТОЕ И oди, i дцaтcй и двенадцатой групп, выходы элементов И if. .«адцагой, четырнадцатой и пятнадцатой

O групп объедянсиь и соединены с группой устрпГстпа для подключения к ipvnn0 информационных пходов первой ML юоЭОМ, выходы злементиь И ше гнад- цатэй, семнадцатой и оосемпадцатой групп

5 о5ьелин°ны и соединены с группой выходов устройства дл подключения к группе ин- формзционных аходов второй микроЭВМ.

2 Устройство по п. 1, о т л и ч а ю ш е е- с я теп 4io узел формирования сигналов

0 разрешения содержит два элемент а НЕ, два элемента ИЛ V, и два триггера, причем входы первою и втсртго элементов НЕ являются и вторым входами узла cooTceiCT- венсо и соединены с первыми входами вто5 OOIG и первого олиментов ИЛИ гоответствеино, выходы первого и второго элементов НЕ соединены с вторыми входами первого и второю элементов ИЛИ соот- ве.стврчно, а выходы первою и второго

0 элементов ИЛИ соединены с установочными входами первого и второго триггеров со- ответственно, входы сброса которых являются первым и вторым установочными входами узла, выходы первого и второго

5 триггеров являются первым и вторым выходами узла соответственно.

Фиг.1

f:

S &

I

:su

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух микро эвм с общей памятью | 1985 |

|

SU1280643A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

Изобретение может быть использовано для создания многомашинных вычислительных комплексов. Цель изобретения состоит в увеличении быстродействия устройства при обмене информацией двух микроЭВМ с общей памятью за счет введения семи элементов ИЛИ, шестнадцати групп элементов И, трех узлов формирования сигналов разрешения. Введение указанных узлов в устройство реализует одновременный доступ обеих микроЭВМ к общей памяти, так как в устройстве реализованы раздельные каналы обращения каждой микроЭВМ к любому из трех блоков общей памяти и осуществлен новый принцип формирования сигналов разрешения. В связи с этим увеличивается быстродействие устройства, так как существенно сокращаются простои микроЭВМ, связанные с ожиданием предоставления доступа к общей памяти. Устройство содержит регистры адреса, дешифраторы адреса, группы элементов И, узлы синхронизации, дешифраторы, узлы формирования сигналов записи. 1 з.п. ф-лы, 5 ил.

Cr, CA|

$ Ј

fc-

T)

Ј tTi

p Ко

СЛ

c&

Фиг.5

| Горбачев С.Ф., Демин А.П | |||

| Оперативное запоминающее устройство с внешним скоростным каналом ввода-вывода информации в микроЭВМ Электроника-бО | |||

| - Микропроцессорные средства и системы, 1988, 3, с | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Устройство для сопряжения двух микро эвм с общей памятью | 1985 |

|

SU1280643A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-07-20—Подача