15

11282327

Piaобретение относится к технике аналого-цифрового преобразования сигналов и может быть использовано в быстродействующих информационно- измерительных системах, где находят применение цифровые методы обработки аналоговой информации.

Цель изобретения - повышение надежности за счет упрощения преобразователя и повьпиение быстродействия.

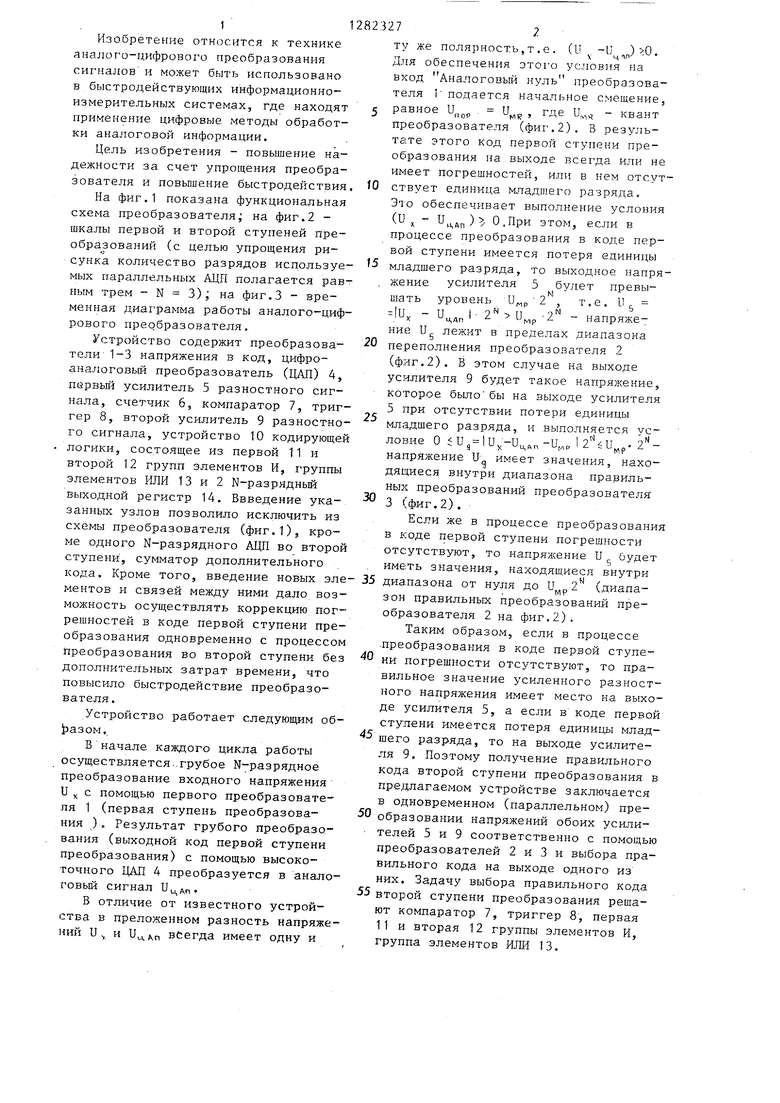

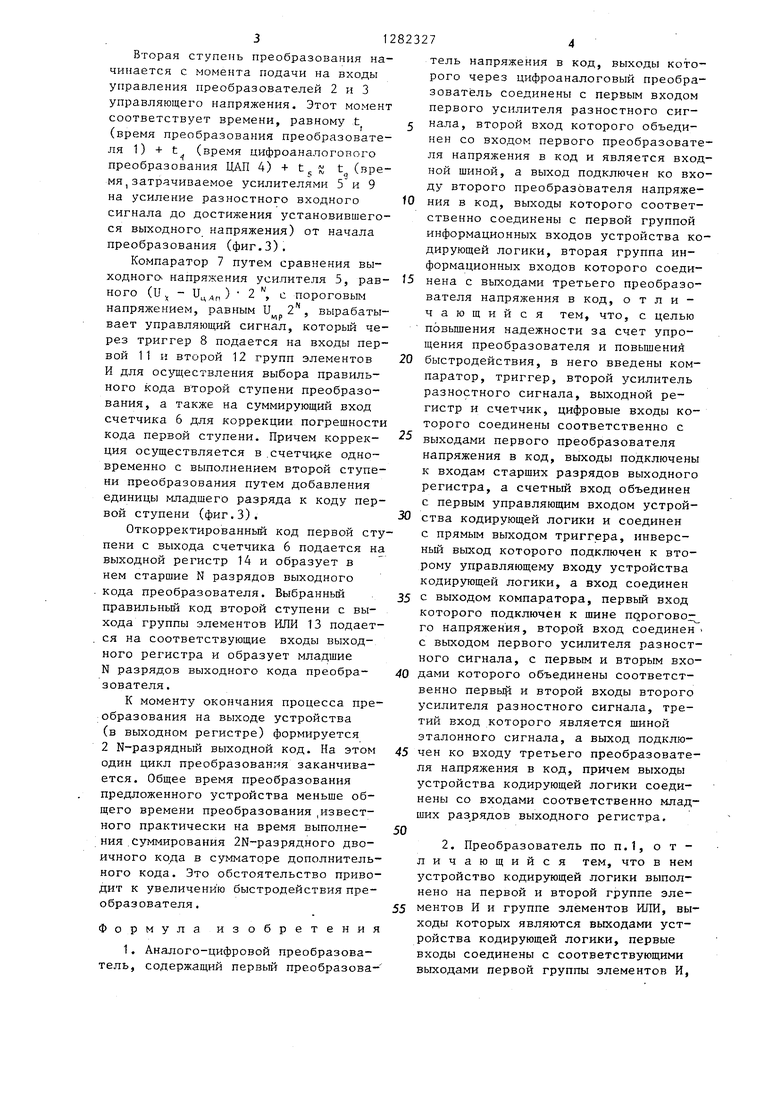

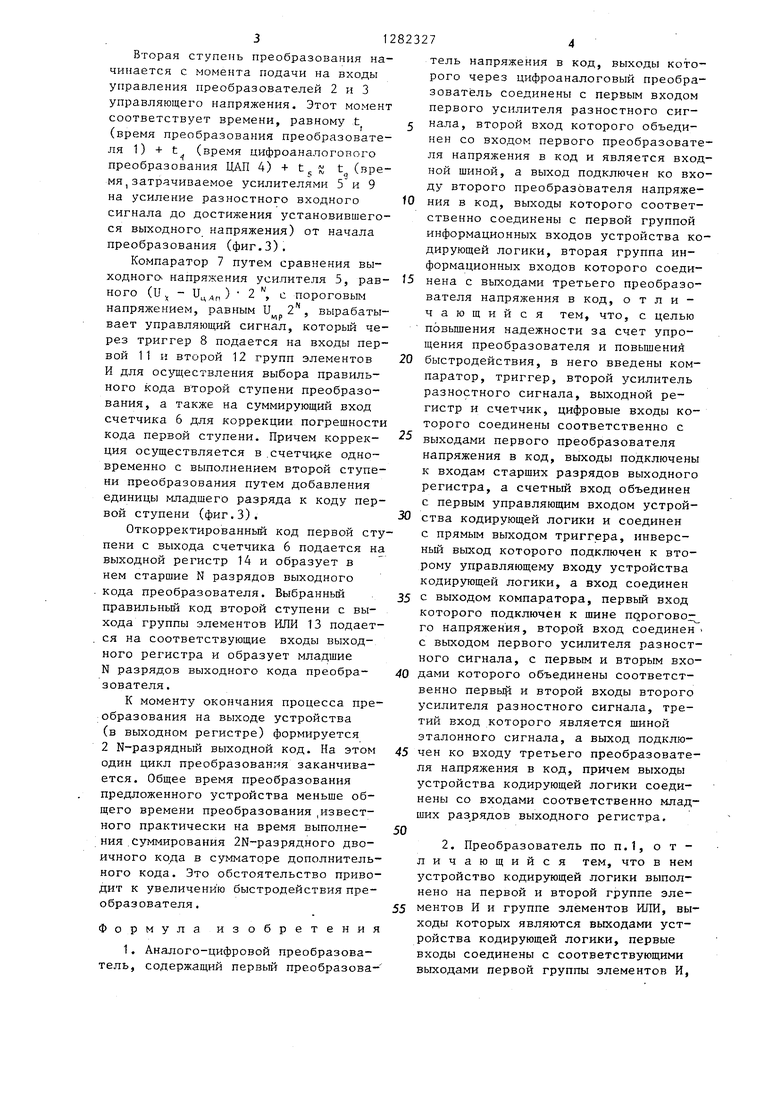

На фиг.1 показана функциональная схема преобразователя; на фиг.2 - шкалы первой и второй ступеней преобразований (с целью упрощения рисунка количество разрядов используемых параллельных АЦП полагается равным трем - N 3); на фиг.З - временная диаграмма работы аналого-цифрового преобразователя.

Устройство содержит преобразователи 1-3 напряжения в код, цифро- аналогов м преобразователь (ЦАП) 4, первьй усилитель 5 разностного сигналагер

го сигнала, устройство 10 кодирующей логики, состоящее из первой 11 и второй 12 групп элементов И, группы элементов ИЛИ 13 и 2 N-разрядньй выходной регистр 14. Взведение указанных узлов позволило исключить из схемы преобразователя (фиг.1), кроме одного N-разрядного АЦП во второй ступени , сумматор дополнительного кода

2

ту же полярность,т. е . (U . ) чО. Для обеспечения этого услов тя на вход Аналоговый нуль преобразователя I подается начальное смещение,

равное и,р Д квант преобразователя (фиг.2). В результате этого код первой ступени преобразования на выходе всегда или не имеет погрешностей, или в нем отсут ствует единица младшего разряда. Эю обеспечивает выполнение условия (и - ). О.При этом, если в процессе преобразования в коде первой ступени имеется потеря единицы младшего разряда, то выходное напря

правы бнапряжеfO

жение усилителя 5 будет

по

шать уровень и„р z , т.е ,,.2 .IUx - УцАп

t, счетчик 6, компаратор 7, триг- , второй усилитель 9 разностно20

25

ние Ug лежит в пределах диапазона переполнения преобразователя 2 (фиг.2). В этом случае на выходе усилителя 9 будет такое напряжение которое было бы на выходе усилителя 5 при отсутствии потери единицы младшего разряда, и выполняется ус ловие О . -и„,„-и,,р l2 ilJ

- цлг

МР

напряжение U имеет значения, нахо дягз;иеся внутри диапазона правильных преобразований преобразователя 3 (фиг.2).

Если же в процессе преобразовани в коде первой ступени погрешности отсутствуют, то напряжение U буде иметь значения.

находящиеся внутри Кроме того, введение новых эле- 35 диапазона от нуля до 2 (диапаментов и связей между ними дало возможность осуществлять коррекцию погрешностей в коде первой ступени преобразования одновременно с процессом Преобразования во второй ступени без дополнительных затрат времени, что повысило быстродействие преобразователя.

Устройство работает следующим об- ija3OM.

Б начале каждого цикла работы осуществляется..грубое N-разрядное преобразование входного напряжения и с помощью первого преобразователя 1 (первая ступень преобразования ). Результат грубого преобразования (выходной код первой ступени преобразования) с помощью высокоточного ЦАП 4 преобразуется в анало- говьм сигнал отличие от известного устройства в преложенном разность напряжений и и всегда имеет одну и

5

327

2

ту же полярность,т. е . (U . ) чО. Для обеспечения этого услов тя на вход Аналоговый нуль преобразователя I подается начальное смещение,

равное и,р Д квант преобразователя (фиг.2). В результате этого код первой ступени преобразования на выходе всегда или не имеет погрешностей, или в нем отсутствует единица младшего разряда. Эю обеспечивает выполнение условия (и - ). О.При этом, если в процессе преобразования в коде первой ступени имеется потеря единицы младшего разряда, то выходное напряправы бнапряже

жение усилителя 5 будет

по

шать уровень и„р z , т.е ,,.2 .IUx - УцАп

0

5

ние Ug лежит в пределах диапазона переполнения преобразователя 2 (фиг.2). В этом случае на выходе усилителя 9 будет такое напряжение, которое было бы на выходе усилителя 5 при отсутствии потери единицы младшего разряда, и выполняется условие О . -и„,„-и,,р l2 ilJ

- цлг

МР

напряжение U имеет значения, нахо- дягз;иеся внутри диапазона правильных преобразований преобразователя 3 (фиг.2).

Если же в процессе преобразования в коде первой ступени погрешности отсутствуют, то напряжение U будет иметь значения.

находящиеся внутри 35 диапазона от нуля до 2 (диапа0

5

зон правильных преобразований преобразователя 2 на фиг.2).

Таким образом, если в процессе .преобразования в коде первой ступени погрешности отсутствуют, то правильное значение усиленного разностного напряжения имеет место на выходе усилителя 5, а если в коде первой ступени имеется потеря единицы младшего разряда, то на выходе усилителя 9. Поэтому получение правильного кода второй ступени преобразования в предлагаемом устройстве заключается в одновременном (параллельном) пре0 образовании напряжений обоих усили- телей 5 и 9 соответственно с помощью преобразователей 2 и 3 и выбора правильного кода на выходе одного из них. Задачу выбора правильного кода

5 второй ступени преобразования решают компаратор 7, триггер 8, первая 11 и вторая 12 группы элементов И, группа элементов ИЛИ 13.

3

Вторая ступень преобразования начинается с момента подачи на входы управления преобразователей 2 и 3 управляющего напряжения. Этот момен соответствует времени, равному t (время преобразования преобразователя 1)

+ t (время цифроаналогового преобразования ЦАП 4) + t к t (время, затрачиваемое усилителями 5 и 9 на усиление разностного входного сигнала до достижения установившегося выходного напряжения) от начала преобразования (фиг.З),

Компаратор 7 путем сравнения вы- ходногск напряжения усилителя 5, равного (и - 2 , с пороговым напряжением, равным U 2, вырабатывает управляющий сигнал, который через триггер 8 подается на входы первой 11 и второй 12 групп элементов И для осуществления выбора правильного кода второй ступени преобразования, а также на суммирующий вход счетчика 6 для коррекции погрешност кода первой ступени. Причем коррекция осуществляется в .счетчрусе одновременно с выполнением второй ступени преобразования путем добавления единицы младшего разряда к коду первой ступени (фиг.З).

Откорректированньй код первой стпени с выхода счетчика 6 подается н выходной регистр 14 и образует в нем старшие N разрядов выходного кода преобразователя. Выбранный правильный код второй ступени с выхода группы элементов ИЛИ 13 подается на соответствующие входы выходного регистра и образует младшие N разрядов выходного кода преобразователя .

К моменту окончания процесса преобразования на выходе устройства (в выходном регистре) формируется 2 N-разрядный выходной код. На этом один цикл преобразования заканчивается. Общее время преобразования предложенного устройства меньше общего времени преобразования ,известного практически на время выполнения суммирования 2N-paзpяднoгo двоичного кода в сумматоре дополнительного кода. Это обстоятельство приводит к увеличению быстродействия преобразователя .

Формула изобретени

1. Аналого-цифровой преобразователь, содержащий первьй преобразова

тель напряжения в код, выходы которого через цифроаналоговый преобразователь соединены с первым входом первого усилителя разностного сигнала, второй вход которого объединен со входом первого преобразователя напряжения в код и является входду второго преобразователя напряжения в код, выходы которого соответственно соединены с первой группой информационных входов устройства кодирующей логики, вторая группа информационных входов которого соединена с выходами третьего преобразователя напряжения в код, отличающийся тем, что, с целью повьпиения надежности за счет упрощения преобразователя и повьщ1ения

быстродействия, в него введены компаратор, триггер, второй усилитель разностного сигнала, выходной регистр и счетчик, цифровые входы которого соединены соответственно с

выходами первого преобразователя напряжения в код, выходы подключены к входам старших разрядов выходного регистра, а счетный вход объединен с первым управляющим входом устройства кодирующей логики и соединен с прямым выходом триггера, инверсный выход которого подключен к второму управляющему входу устройства кодирующей логики, а вход соединен

с выходом компаратора, первый вход которого подключен к шине пороговог; го напряжения, второй вход соединен с выходом первого усилителя разностного сигнала, с первым и вторым входами которого объединены соответственно первьщ и второй входы второго усилителя разностного сигнала, третий вход которого является шиной эталонного сигнала, а выход подключен ко входу третьего преобразователя напряжения в код, причем выходы устройства кодирующей логики соединены со входами соответственно младших разрядов выходного регистра.

2. Преобразователь по п.1, отличающийся тем, что в нем устройство кодирующей логики выполнено на первой и второй группе эле- ментов И и группе элементов ИЛИ, выходы которых являются выходами устройства кодирующей логики, первые входы соединены с соответствующими выходами первой группы элементов И,

ь1

первые входы которых объединены и являются первым управляющим входом устройства кодирующей логики, а вторые входы образуют вторую группу информационных входов устройства кодирующей логики, вторые входы группы элементов ИЛИ соединены с соответст2823276

вующими выходами второй группы элементов И, первые входы которых объединены и являются вторым управляющим входом устройства кодирующей логики, 5 а вторые входы образуют первую группу информационных входов устройства кодирующей логики.

e/7 ffflcrj СЛ7у/7€М6

npeoSpo3o6(

Временная диаграмма paffo/77e / /jfleff/rozaefioeo

Время Время . YU-/7fleoS- il -npeoff- .poxSof/t/j po3oSa M I /iy/7/ I //7 1I

Редактор В.Данко

Составитель В.Махнанов

Техред М.Ходанич Корректор Л.Пилипенко

Заказ 7286/58Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

is

OMOHvoHi e npeofpcfooSoff /

Фиг 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| Способ аналого-цифрового преобразователя и устройство для его осуществления | 1985 |

|

SU1305848A1 |

| Параллельно-последовательный преобразователь напряжения в код | 1982 |

|

SU1039027A2 |

| СЛЕДЯЩИЙ АЦП МНОГОРАЗРЯДНЫХ ПРИРАЩЕНИЙ | 2016 |

|

RU2619887C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Последовательно-параллельный аналого- цифровой преобразователь | 1978 |

|

SU743193A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2010 |

|

RU2442279C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1152088A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

Изобретение относится к технике аналого-цифрового преобразования сигналов и может быть использовано в быстродействующих информационно- измерительных системах, где находят применение цифровые методы обработки аналоговой информации. Целью изобретения является упрощение конструкции и повышение быстродействия аналого-цифрового преобразователя параллельно-последовательного типа за счет уменьшения количества применяемых параллельных преобразователей с четырех до трех и применения более простых устройств и за счет выполнения коррекции погрешностей старших разрядов (результата первой ступени преобразования) одновременно с процессом преобразования во второй ступени без дополнительных затрат времени. Устройство содержит параллельные преобразователи 1-3, ЦАП 4, усилитель 5 разностного сигнала, счетчик 6, компаратор 7, триггер 8, усилитель 9 разностного сигнала, устройство 10 кодирующей логики с элементами И 11, 12, ИЛИ 13, выходной регистр 14. 1 з.п. ф-лы, 3 ил. / с € оо ГчЭ ОО to « иг./

| Кондалев А.И | |||

| и др | |||

| Преобразователи формы информации для малых ЭВМ | |||

| Киев: Наукова думка, 1982, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электроника, 1982, № 9, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-07—Публикация

1984-03-11—Подача