дешифратор 5 подключает следующий блок 1. i памяти к микропроцессору. После обращения к последнему адресу последнего блока 1.N памяти происхоИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных систем на основе микропроцессоров,

Цель изобретения - расширение области применения устройства.

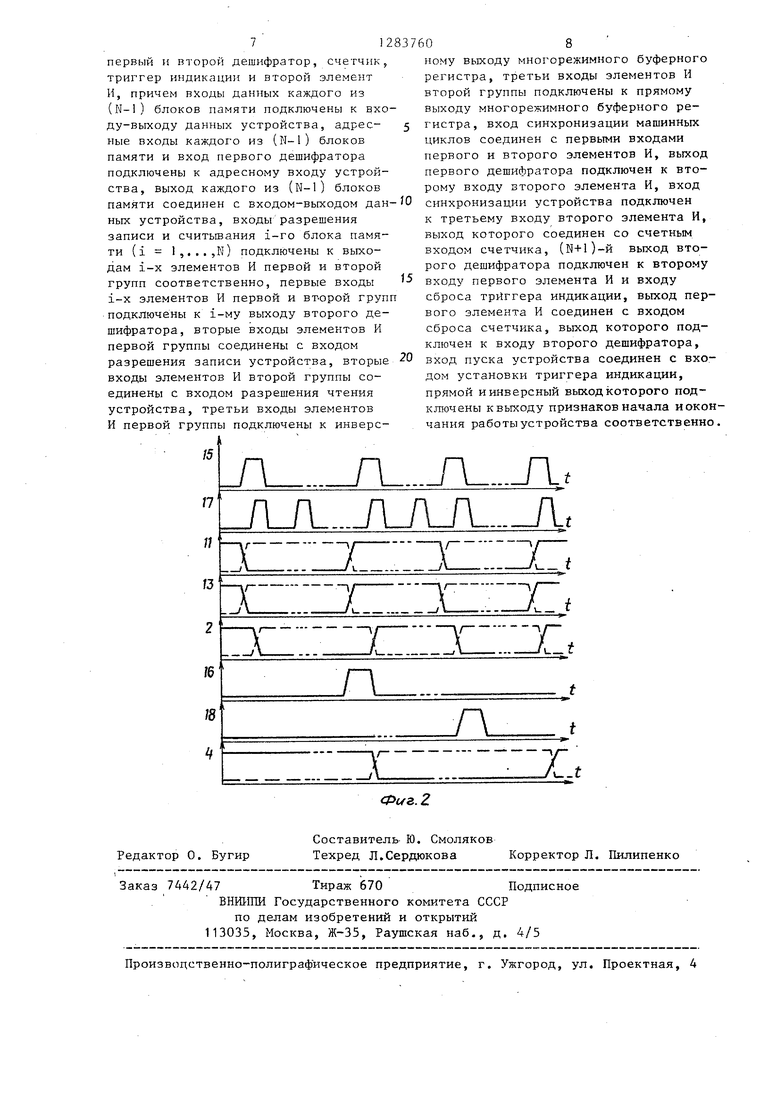

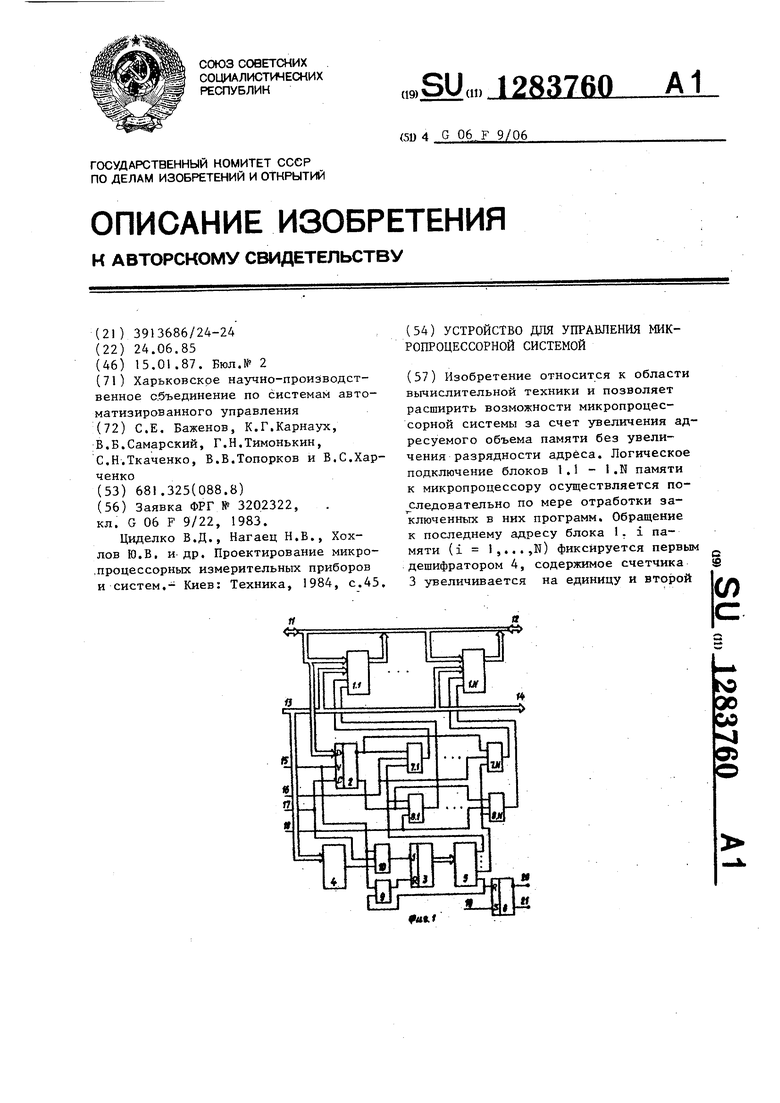

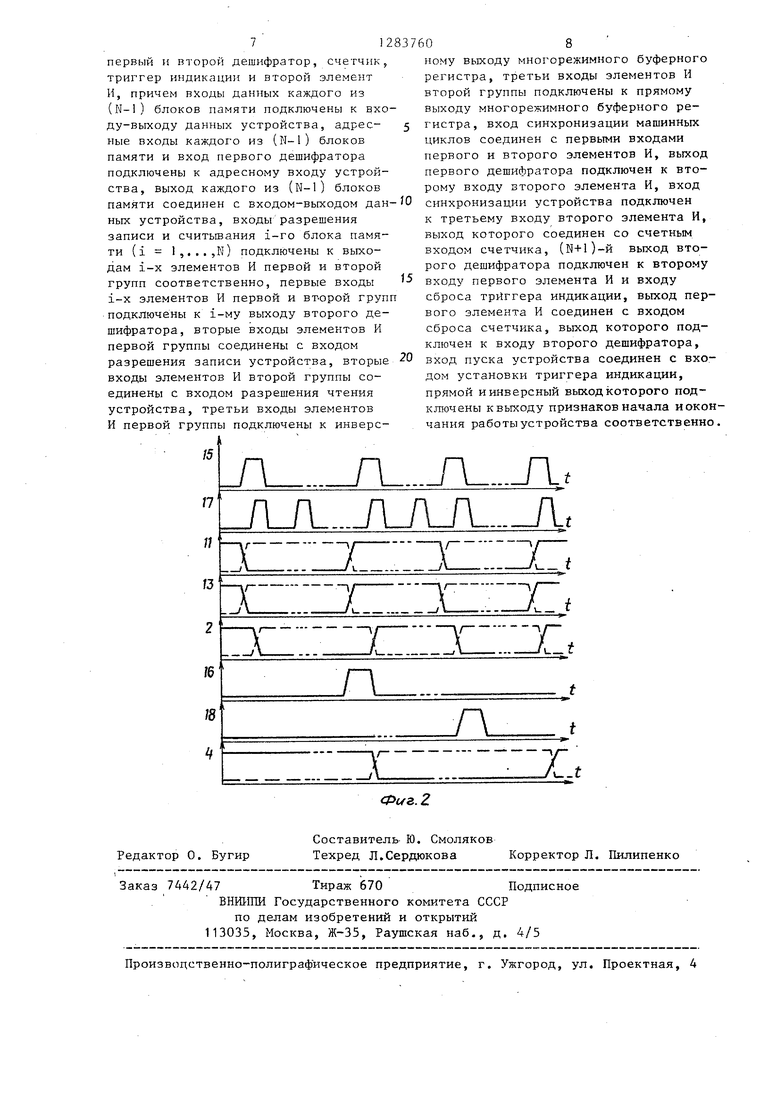

На фиг.1 представлена фукциональ- ная схема устройства; на фиг.2 - временная диаграмма работы устройства.

Устройство для управления микропроцессорной системой содержит блоки 1.1 - 1 .N памяти, многорежимный буферный регистр 2, счетчик 3, первый 4 и второй 5 дешифраторы, триггер 6 индикации, элементы И 7.1 - 7.N первой группы, элементы И 8.1- /8.N второй группы, первый 9 и вто- jрой 10 элементы И, первый II и вто- рой 12 вход-выход устройства, адресные вход 13 и выход 14 устройства, вход 15 синхронизации машинных цикл работы устройства, вход 16 разрешения записи информации, вход 17 син- хронизации устройства, вход 18 разрешения ввода информации, вход 19

пуска устройства, выходы 20 и 21

сигнализации соответственно окончания и начала пуска работы устройства. Первый вход-выход 11 устройства соединен с вторым входом-выходом 12 устройства, входами данных блоков 1,1 - 1,N памяти и информационным входом многорежимного буферного регистра 2. Адресный вход 13 устройства связан с адресными входами блоков 1,1- 1.N памяти, входом первого дешифратора А и адресным выходом 14 устройства. Вход 15 синхронизации машинных циклов устройства соединен с разрешающим входом многорежимного буферного регистра 2 и первыми входами элементов И 9 и О. Вход 16 разрешения записи информации устройства подключен к вторым входам эле

дит сброс счетчика 3. К микропродес- сору подключается первый блок .1 памяти и цикл работы повторяется. 2 ил.

5

О

5

0

0

5

ментов И 7.1-7.N первой группы. Вход

17синхронизации устройства соединен с входом синхронизации многорежимного буферного регистра 2 и третьим входом второго элемента И 10. Вход

18разрешения ввода информации связан с вторыми входами элементов И 8.1 - 8.N второй группы. Выходы блоков 1.1 - 1.N памяти соединены с первым входом-выходом II устройства. Выход элемента И 9 подключен к входу установки в нуль счетчика 3, выход которого соединен с входом второго дешифратора 5. Выходы второго дешифратора 5 соединены с первыми входами соответственно элементов И 7,1-7.N и 8.1 - 8.N первой и второй групп. Первый выход многорежимного буферного регистра 2 подсоединен к третьим входам элементов И 7.1 - 7,Й первой группы. Второй выход многорежимного буферного регистра 2 подключен к третьим входам элементов И 8.1 - 8.Ы второй группы. Выходы, элементов, И 7.1 - 7.и первой группы и выходы элементов И 8.I - 8.N второй группы соединены соответственно с входами разрешения записи и считьшания информации блоков 1.1 - 1.N памяти, (К+1)-ый выход второго дешифратора 5 связан с вторым входом элемента И 9 и нулевым входом триггера 6 индикации. Выход дешифратора 4 соединен с вторым входом второго элемента И 10, выход которого связан со счетным входом счетчика 3. Вход

19пуска устройства соединен с единичным входом триггера 6 индикации, единичный выход которого подключен к выходу 21 сигнализации начала работы устройства, а нулевой - к выходу 20 окончания работы устройства.

Блоки 1,1 - 1.N памяти предназначены для хранения информации, используемой для выполнеЬия заданной программы, Многорежимный буферный регистр 2 служит для записи н хранения соответствующих разрядов (первого и седьмого) кодов слов состояния микропроцессора. Счетчик 3 фиксирует количество блоков памяти устройства с которыми взаимодействует микропроцессор. Деи ифратор 4 npeAH jsHaueH для установления факта обращения микропроцессора к последней ячейке адресуемого блока памяти. Дешифратор 5 - для определения номера адресуемого микропроцессором блока Id памяти. Элементы И 7.1 - 7.И первой группы применяется для формирования сигналов разрешения записи информа- iции в блоки ,1 - 1,N памяти, эле-, менты И 8е1 8,N второй группы - для формирования сигналов разрешения считывания информации из блоков 1.1- 1.N памяти. Триггер 6 индикации используется для выработки и выдачи сигналов, управляющих индикацией начала и окончания работы устройства. Первый элемент И 9 предназначен для формирования сигнала установки в нуль счётчика 3, второй элемент И 10 - для выдачи имцульсов на счетный вход.счетчика 3, Первый вход- выход 11 устройства служит для связи с выходами Дд - Д (ВД - ВД) микропроцессоров серий КР580ИК80, Ад- ресньш вход 13 устройства соединен с выходами А,, - А, (ВА,-, - ВА, ) мик15

15

1

ропроцессоров тех же серий. Вход 15 синхронизации машинных циклов работы устройства предназначен для связи с выходом СИНХР (SYNC) указанных выше микропроцессоров, вход 6 разрешения записи информации - для соединения с выходом ЗП (WR) микропроцессоров указанных сериЙ9.вход 17 синхронизации устройства - для соединения с входом Ф (cpj) микропроцессоров указанных серий, вход.8 разустройства, в регистр 2 записываются первый и седьмой разряды кода слова состояния процессора. Единичное значение седьмого разряда кода слова 5 состояния процессора обусловливает выполнение цикла ffiMR (чтения информации из памяти), Нулевое значение первого разряда кода слова состояния процессора обусловливает выпол 0 нение цикла WO (записи информации в память),

При выполнении цикла МЕШ единичный сигнал появляется на втором вы-. ходе р истра 2, а при выполнении цикла WO - на первом. В соответствии с этим на соответств ующих выходах первой группы элементов И 7,1 - 7.N или второй группы элементов И 8.) - 8„И разрешено формирование единичных

20 сигналов. По этим сигналам осуществляется обращение (считывание или запись информации) в выбранный дешифратором 5 блок l.i памяти, В процессе функционирования микропроцессора при его обраш,ении к первому блоку 1.1 памяти содержимое счетчика 3 равно нулю. Возб ужденным является первый выход второго дешифратора 5, единичньй сигнал на выходе которого обусловливает работу цервог элемента И 7. первой группы. После того, как на адресном входе 13 устройства устанавливается код адреса последней ячейки первого блока 1.1

35 памяти на выходе первого дешифратора 4 формируется единичный сигнал. В результате этого в счетчик 3 записывается код 1. Активным становится второй выход дешифратора 5.

0 Единичный сигнал с этого выхода открывает второй элемент И 7.2, разрешая обращение микропроцессора к второму блоку 1.2 памяти. После завершения работы микропроцессора с

25

30

решения ввода информации устройства - последним блоком 1,N памяти единичдля соединения с выходом П (DB/N) микропроцессоров указанных с ерйй.

Микропроцессор начинает выполнение программы с обращения к первому блоку ,1 памяти. Перед выполнением машинного цикла работы устройства на первом входе-выходе 11 данных устройства появляется код слова состояния процессора. По импульсу синхрониза- цмм, поступающему через вход 15 устройства на разрешающий вход регистра 2, и по импульсу синхронизации, поступающему на вход синхронизации 17

анения ого и микуетйства ропроueHия ейке фратор есуепавойвания орма- эле-, ы - ешения в 1.1- и исачией наства. н для в т И четод-связи микАд-инен ) мик15

од 15 рабосвяанныхразя соропро17соедиоцесразустройства, в регистр 2 записываются первый и седьмой разряды кода слова состояния процессора. Единичное значение седьмого разряда кода слова 5 состояния процессора обусловливает выполнение цикла ffiMR (чтения информации из памяти), Нулевое значение первого разряда кода слова состояния процессора обусловливает выпол 0 нение цикла WO (записи информации в память),

При выполнении цикла МЕШ единичный сигнал появляется на втором вы-. ходе р истра 2, а при выполнении цикла WO - на первом. В соответствии с этим на соответств ующих выходах первой группы элементов И 7,1 - 7.N или второй группы элементов И 8.) - 8„И разрешено формирование единичных

20 сигналов. По этим сигналам осуществляется обращение (считывание или запись информации) в выбранный дешифратором 5 блок l.i памяти, В процессе функционирования микропроцессора при его обраш,ении к первому блоку 1.1 памяти содержимое счетчика 3 равно нулю. Возб ужденным является первый выход второго дешифратора 5, единичньй сигнал на выходе которого обусловливает работу цервого элемента И 7. первой группы. После того, как на адресном входе 13 устройства устанавливается код адреса последней ячейки первого блока 1.1

35 памяти на выходе первого дешифратора 4 формируется единичный сигнал. В результате этого в счетчик 3 записывается код 1. Активным становится второй выход дешифратора 5.

0 Единичный сигнал с этого выхода открывает второй элемент И 7.2, разрешая обращение микропроцессора к второму блоку 1.2 памяти. После завершения работы микропроцессора с

25

30

ный сигнал устанавливается на .(N+1 )-м выходе дешифратора 5. Этим сигналом по импульсу синхронизации с входа 15 устройства через элемент И 9 про- изойдет установка в нуль счетчика 3. На выход 20 устройства поступит сигнал окончания работы.

Предлагаемое устройство для управ- ления микропроцессорной системой работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (цепи установки в нуль элементов памяти устройства в исходное состояние и цепи подачи питания не показаны). По сигналу с входа 19 пуска уст.ройства триггер 6 устанавливается в. единичное состояние. Единичный сигнал с единичного вькода триггера 6 поступает на выход 21 устройства,сигнализируя о начале работы устройства. Единичный сигнал с первого выхода дешифратора 5 поступает на первые входы первых элементов И 7, и 8.i

.первой и второй групп о На вход-выход I1 устройства поступает код слова состояния процессора По импульсам синхронизации,; поступающим с входов 15 и 17 устройства, происходит запис значений первого и седьмого разрядов кода слова состояния процессора в регистр 2,,

Пусть микропроцессор выполняет цикл MEMR (чтения информации из памяти)., В этом случае на втором выходе регистра 2 появляется единичный сигнал, которой поступает на треты входы элементов И S.I - второй группы. После появления на входе i8 устройства сигнала DB/N (разрешения перевода шины данных микропроцессора в режим ввода информации) на вь ходе элемента И 8,1 формируется единичный сигнал. Этот сигнал поступает на вход разрешения считы.вания информации ггервого блока I 1 памяти и разрешает считывание из него, информации

Если выполняется цикл WO (записи информации в память)5 то единичньш сигнал появляется на первом выходе регистра 2 и поступает на третьи входы элементов И 7„1 - 7аЫ первой группы. После появления на входе 16 устройства сигнала разрешения записи на выходе первого элемента И 7,1 формируется единичный сигнал Этот сигнал постз ает на вход разрешения записи информации в блок 1,i памяти.

Независимо от того, какой выполняется цикл работы микропроцессором МЕШ или WO, после того как на адресном входе 13 устройства выставляется код, соответствующий адресу последней-ячейки блока 1. памяти, на выходе дешифратора 4 формируется един1-тчный сигнал, который поступает на второй вход элемента И 10, Единичный сигнал с входа 15 устрой :тва поступает на первый вход элемента И 10 и открывает его. По импульсу синхронизации5 поступающему с входа

10

15

837606

17 устройства на третий вход элемента И 10, на его выходе формируется единичный сигнал, по которому в счетчике 3 устанавливается код 1. В соответствии G этим кодом на втором вьгходе дешифратора 3 устанавливается единичный сигнал, который открывает вторые элементы И 7.-2 и 8.2 первой и второй групп. Работа устройства продолжается.. После того, как произойдет реализация программы,записанной в последнем блоке I.N памяти, и на адресном входе 13 устройства установится код последней ячейки памяти, произойдет аналогично описанному выше йзмен.ение содержимого счетчика 3: в Иен будет установлен код (N+1),

На последнем выходе (N+1)-м) дешифратора 5 устанавливается единичный сигнал. По этому сигналу происходит установка триггера 16 в нулевое состояние. По импульсу синхронизации, поступающему с входа 15 устройства, на выходе элемента И 9 формируется единичньй сигнал, который производит установку в нуль счетчика 3. Единичный сигнал с инверсного вькода триггера 6 поступает на выход 20 окончания работы устройства. Работа устройства заканчивается.

Формула изобретения

20

25

30

5

0

Устройство для управления микропроцессорной системой, содержащее первый блок памяти, многорежимный буферный регистр и первый элемент И, причем вход-выход данных устройства соединен с входом данных первого блока памяти, информационным входом многорежимного буферного регистра и вторым входом-выходом данных устройства, адресньй вход устройства соединен с адресным входом первого г; блока памяти, вход синхронизации машинных циклов устройства соединен с входом разрешения записи, многорежимного буферного регистра, вход синхронизации устройства соединен с входом синхронизации многорежимного буферного регистра, выход первого блока памяти соединен с входом- выходом данных устройства, отличающееся тем, что, с целью расширения класса решаемых задач путем увеличения объема адресуемой памяти без увеличения разрядности адреса, введены (N-) блоков памяти, первая и вторая группа элементов И,

0

5

первый и второй дешифратор, счетчик, триггер индикации и второй элемент Н, причем входы данных каждого из (N-1) блоков памяти подключены к входу-выходу данных устройства, адрес- ные входы каждого из (N-1) блоков памяти и вход первого дешифратора подключены к адресному входу устройства, выход каждого из (N-1) блоков памяти соединен с входом-выходом дан ных устройства, входы разрешения записи и считьтания i-ro блока памяти (i - 1,...,N) подключены к выходам i-x элементов И первой и второй групп соответственно, первые входы i-x элементов И первой и вт-орой груп подключены к i-му выходу второго дешифратора, вторые входы элементов И первой группы соединены с входом разрешения записи устройства, вторые входы элементов И второй группы соединены с входом разрешения чтения устройства, третьи входы элементов И первой группы подключены к инверс

O

5

0

ному вькоду многорежимного буферного регистра, третьи входы элементов И второй группы подключены к прямому выходу многорежимного буферного регистра, вход синхронизации машинных циклов соединен с первыми входами первого и второго элементов И, выход первого дешифратора подключен к второму входу второго элемента И, вход синхронизации устройства подключен к третьему входу второго элемента И, выход которого соединен со счетным входом счетчика, (И+1)-й выход второго дешифратора подключен к второму входу первого элемента И и входу сброса триггера индикации, выход первого элемента И соединен с входом сброса счетчика, выход которого подключен к входу второго дешифратора, вход пуска устройства соединен с входом установки триггера индикации, прямой и инверсный выход которого подключены квыходу признаков начала иокон- чания работы устройства соответственно.

....,

.г...лп

j

L i

r

Т.г

L i

r

Т.г

Редактор О. Бугир

Фиг. 2

Составитель Ю. Смоляков

Техред Л.Сердюкова Корректор Л. Пилипенко

Заказ 7442/47Тираж 670Подписное

ВНЮШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к области вычислительной техники и позволяет расширить возможности микропроцессорной системы за счет увеличения адресуемого объема памяти без увеличения разрядности адреса. Логическое подключение блоков 1.1 - 1.N памяти к микропроцессору осуществляется по- ледовательно по мере отработки заключенных в них программ. Обращение к последнему адресу блока 1. i памяти (1 I,...,N) фиксируется первым дешифратором 4, содержимое счетчика 3 увеличивается на единицу и второй с 9 (Л lfut.1

| Прибор для подогрева воздуха отработавшими газам и двигателя | 1921 |

|

SU320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Циделко В.Д., Нагаец Н.В., Хохлов Ю.В, и др | |||

| Проектирование микро- ,процессорных измерительных приборов и систем,- Киев: Техника, 1984, с.45. | |||

Авторы

Даты

1987-01-15—Публикация

1985-06-24—Подача