СО 00

ел

О

ел

113

Устройство относится к вычислительной технике и может быть применено в центральных процессорах в качестве управляющего блока.

Цель изобретения - сокращение объема блока памяти микрокоманд.

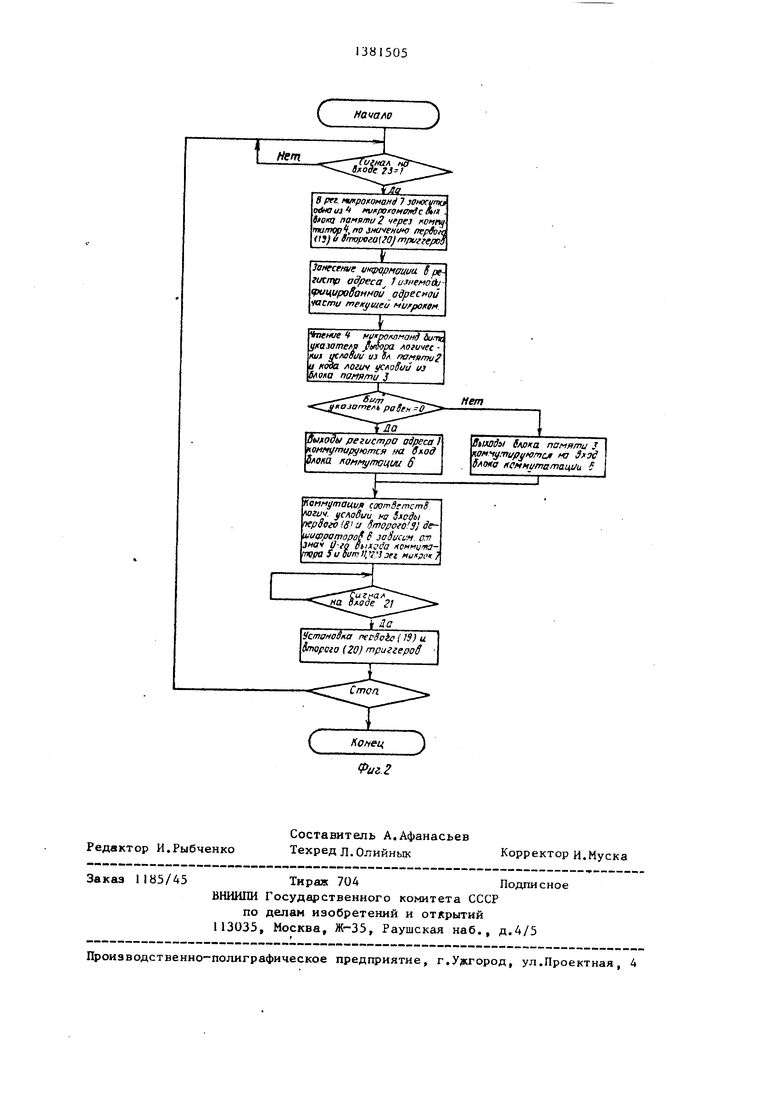

На фиг.1 представлена структурная схема устройства микропрограммного управления; на фиг.2 - блок-схема алгоритма работы устройства.

Устройство микропрограммного управления (фиг.1) содержит регистр 1 адреса, блок 2 памяти микрокоманд, блок 3 памяти кодов логических условий, первый 4 и второй 5 коммутаторы, регистр 6 микрокоманд, блок 7 коммутации, четвертый дешифратор 8, первый 9, второй 10 и третий 11 дешифраторы, элемент И-НЕ 12, первый 13 и второй 14 элементы И, первая 15 и вторая 16 группы элементов И, первьй 17 и второй 18 элементы ИЛИ, первьй 19 и второй 20 триггеры,входы 21-23 синхронизации устройства, входы первой 24 и второй 25 групп условий.

Цель изобретения достигается за счет частичного использования в качестве кодов полей логических условий значений адресов групп микрокоманд ветвлений. Возможность такого использования связана с тем,что группы микрокоманд ветвлений адресуются принудительно, т.е. в текущей микрокоманде содержится немодифицированный адрес группы микрокоманд ветвлений. Поэтому можно разместить группы микрокоманд ветвлений по адресам, равным значению их кодов логических условий, а в адресующих эти группы мик-рокомандах изменить соответствующим образом немодифицирован- ную адресную часть. Необходимо отметить, что в блоке памяти микрокоманд всегда можно разместить рядом пару групп микрокоманд ветвлений, либо имеющих одинаковые коды логических условий, либо у одной из них - код логического условия, равный адресу ее местоположения в блоке 2 памяти. Таким образом, имеется возможность использовать одно и то же поле логических условий для двух соседних групп микрокоманд ветвлений.

Устройство работает следующим образом., .

В каждом машинном такте биты немодифицируемой адресной части регистра

52

6микрокоманд, в котором находится текущая микрокоманда, поступают в регистр 1 адреса. По значению п-бита этого регистра происходит чтение rpynnbj четырех микрокоманд ветвлений и поля указателя выбора, логических условий из блока 2 памяти микрокоманд, а по значению (п-1)-бита регистра адреса происходит чтение полей логических условий из блока 3 памяти кодов логических условий.

В зависимости от значения бита .в поле указателя выбора логических условий коммутатор 5 подключает к входам блока 7 коммутации или,выход регистра адреса 1, или выход блока 3 памяти. Выход 0-го бита коммутатора 5 поступает на первый управлягаций

вход блока 7 коммутации и является идентификатором микрокоманды ветвления.

Выходы 0-го бита, а также первой и второй групп коммутатора 5 поступают соответственно на первый управляю щий и два информационных входа блока

7коммутации и являются для него соответственно битом идентификации микрокоманду ветвления, а также первым, и вторым полями логических условий.

Возможны три варианта расшифровки этих полей в зависимости от значения бита идентификации и бита признака

микрокоманды ветвления.

Безусловный переход. Бит признака микрокоманды ветвления равен О, а значение двух битов признака режима проверки логических условий определя-

ют соответственно биты 11 и 12 адресу следующей микрокоманды.

Условный переход с ветвлением на четыре направления. Бит признака микрокоманды ветвления и бнт иденти и-

кации равны I, а два бита признака режима проверки логических условий равны и. В этом случае коды полей логических условий через блок коммутации поступают соответственно на первый и второй дешифраторы в качестве условий для формировсшия битов 11 и 12 адреса.

Условный переход с ветвлением на два направления. Бит признака микрокоманды ветвления равен 1, бит идентификации равен и, а два признака режима проверки логических условий управляют передачей через блок коммутации полей лог ических условий на дешифраторы.

Формула изобретения

Устройство микропрограммного управления, содержащее регистр адреса, блок памяти микрокоманд, первый коммутатор, регистр микрокоманд, с пер- вого по четвертый дешифраторы, блок коммутации, первый и второй элементы ИЛИ, первый и второй элементы И, первую и вторую группы элементов И, элемент И-ПК, первый и второй тригге ры, информационные входы которых соединены соответственно с выходами первого и второго элементов ШШ, первый и второй информационные входы третьего дешифратора соединены с вы- ходами первого и второго триггеров, выход третьего дешифратора соединен с управляющим входом первого коммутатора, с первого по четвертый информационные входы и выход которого соединены соответственно с выходами нолей с первого по четвертый типов микрокоманд блока памяти микрокоманд и с информационным входом регистра микрокоманд, выход поля немодифици- руемой части адреса следующей микрокоманды которого соединен с информационным входом регистра адреса, выходы которого соединены с адресными входами блока памяти микрокоманд, выходы первого и второго признаков проверки логических условий регистра микрокоманд соединены соответственно с первыми входами первого и второго элементов И, а также с информацион- ными входами четвертого дешифратора, с первого по четвертый выходы которого соединены соответственно с первого по четвертый управляющими входами блока коммутации, причем четвер- тый выход четвертого дешифратора соединен с первым входом элемента И-НЕ, выход поля признака микрокоманды вет

д 5 0 5 Q д

5

вления регистра микрокоманд соединен с первым стробирумцим входом блока коммутации и вторым входом элемента И-НК, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первыми входами первого и второго элементов ШЩ, с второго по ()-й входы которых (где М - количество входов логических условий устройства) соединены с выходами элементов И первой и второй групп соответственно, первые входы соединены соответственно с входами первой и второй групп логических условий устройства, вторые входы элементов И первой и второй групп соединены срответственно с выходами первого и второго дешифраторов, входы которых соединены соответственно с первым и вторым выходами блока коммутации, с первого по третий входы синхронизации устройства соединены соответственно с входами синхронизации первого и второго триггеров, регистра адреса и регистра микрокоманд, отличающееся тем, что, с целью сокращения объема блока памяти микрокоманд, оно содержит блок памяти КОДОВ логических условий и второй коммутатор, первые и вторые информационные входы которого соединены с выходами блока памяти ко дов логических условий и с выходами регистра адреса, К-1 старших разрядов выхода которого (К-разрядность регистра адреса) соединены с адресными входами блока памяти кодов логи ческих условий, выход поля выбора кода логических условий блока памяти микрокоманд соединен с входом управления второго коммутатора, с первого по третий выходы второго коммутатора соединены соответственно с первым и вторым информационными входами и вторым стробирующим входом блока коммутации.

8 pft микрокоманд 7 зЧносити овна аз никропнон с Л/и .

fnoirQ памяти 2 через KOfinfj mamop f, по значение трвоп (13) о 8miimo{ 0) тринервЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1985 |

|

SU1283761A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1322280A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1322279A1 |

| Устройство для сбора диагностической информации о формировании адресов переходов микропрограмм | 1983 |

|

SU1290328A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1211724A1 |

Изобретение относится к вычислительной технике и может быть применено в центральных процессорах в качестве управляющего блока. Цель изобретения - сокращение объема блока памяти микрокоманд. Устройство содержит регистр 1 адреса, блок 2 памяти микрокоманд, блок 3 памяти кодов логических условий, коммутаторы 4 и 5, регистр 6 микрокоманд, блок 7 коммутации, дешифраторы 8, 9, 10 и 11, элемент И-НЕ 12, элементы И 13 и 14, группы 15 и 1Ь элементов И, элементы ИЛИ 17 и 18, триггеры 19 и 20. Введение блока 3 памяти кодов логических условий и коммутатора 5 приводит к достижению цели. 2 ил.

JL

JaivceHuf инд/дрнаиии. S ре- гмтр адреса 1 изнемоди- Ч u upo8anнpu адресной части те/ушей MUffOtten.

L

Чтение t ни ромнанд йи.тк указате/1Я Jfufopa логичес - л/д мловм из м памяти и ww /ioa/v усмбий из блояа памяти J

Л//77-

iifOjameAi, рабен 0

Сылоры регистра адреса I мннутируются на. 6f.off лока коммутации 6

Компутаиия caorr SfmcmS. югич. услобий на S edti кроого fS и второю 3 де- иафраторй( 6 jaSucL n. оя знач 0-10 Силура лр.«у«7- tivpo 5и QUIT а, 3зег wi/vc }

yamanoSna nfcdo ) и imopcio (20) триггеров

нет

Да

Конец

| Способ управления разгрузкой ковша экскаватора-драглайна | 1985 |

|

SU1263761A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Блок микропрограммного управления | |||

| Техническое описание ЩК | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-03-15—Публикация

1986-08-04—Подача