1

Устройство относится к вычисли- тельной технике и может быть применено при диагностике неисправностей центральных устройств микропрограммных ЭВМ.

Цель изобретения - сокращение оборудования за счет уменьшения объ ема блока памяти.

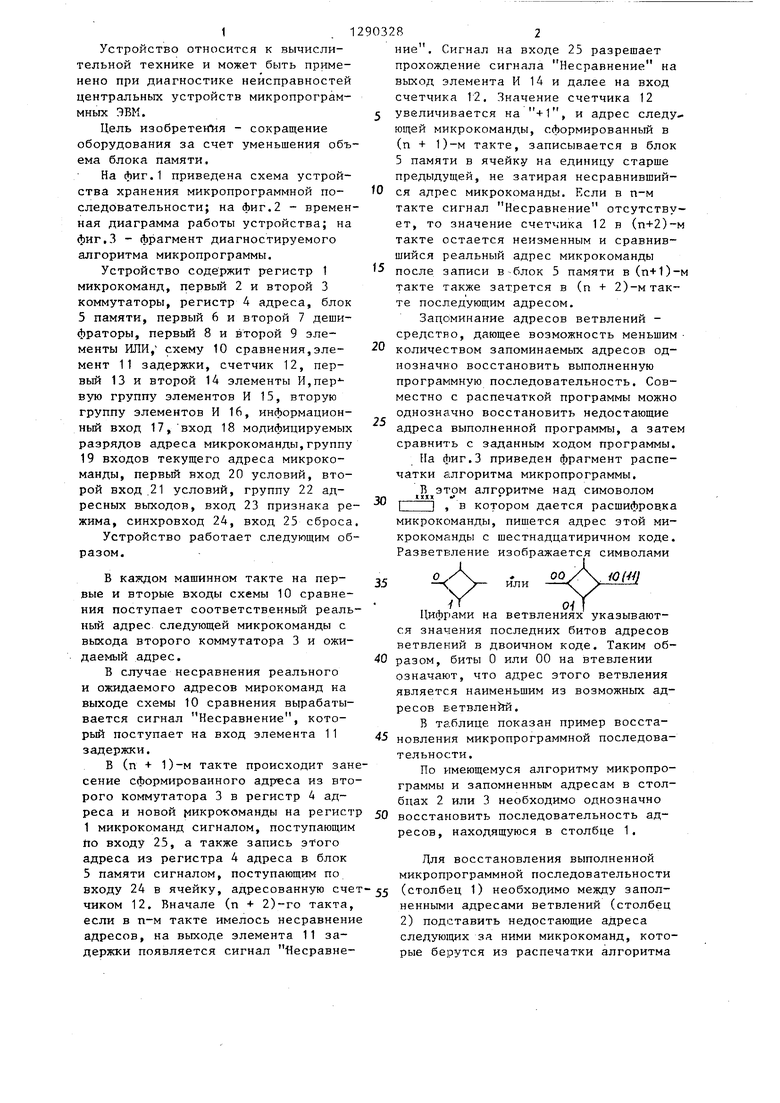

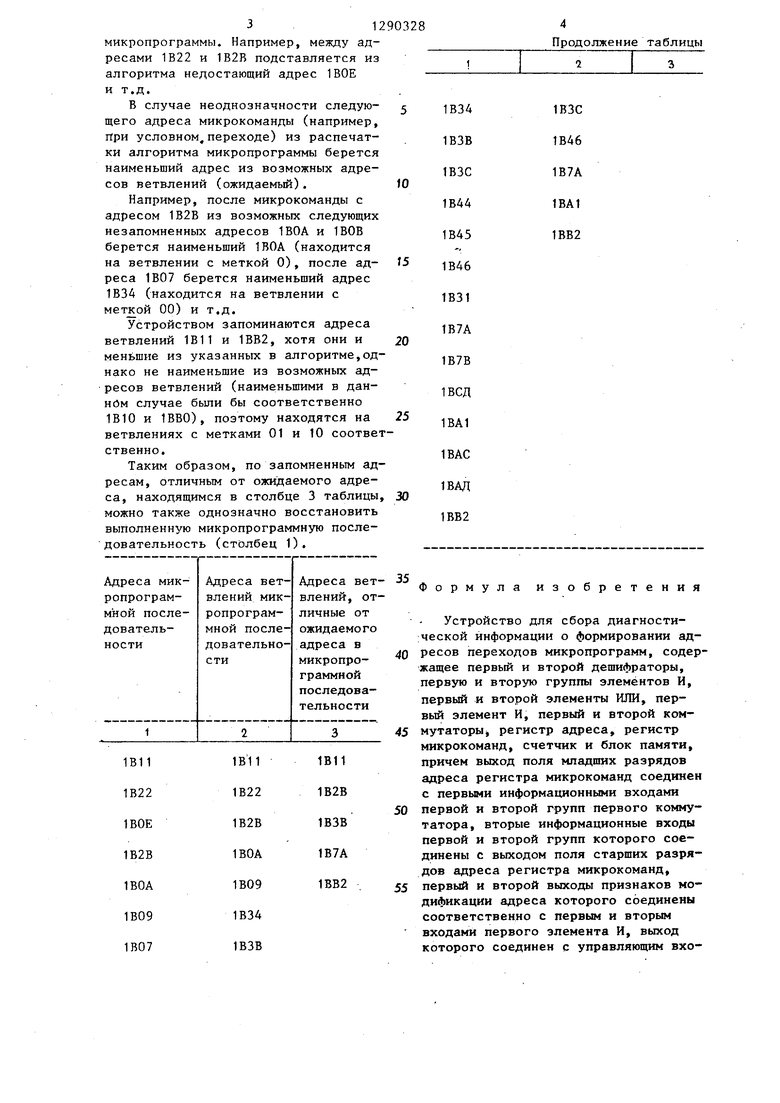

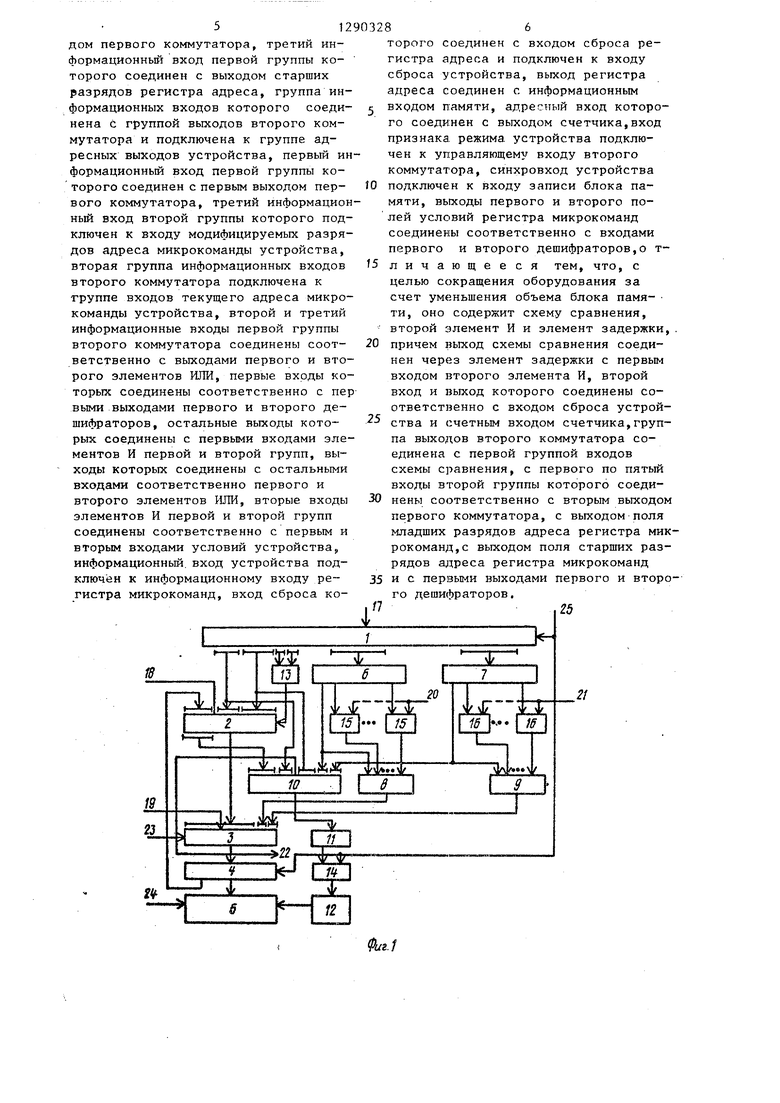

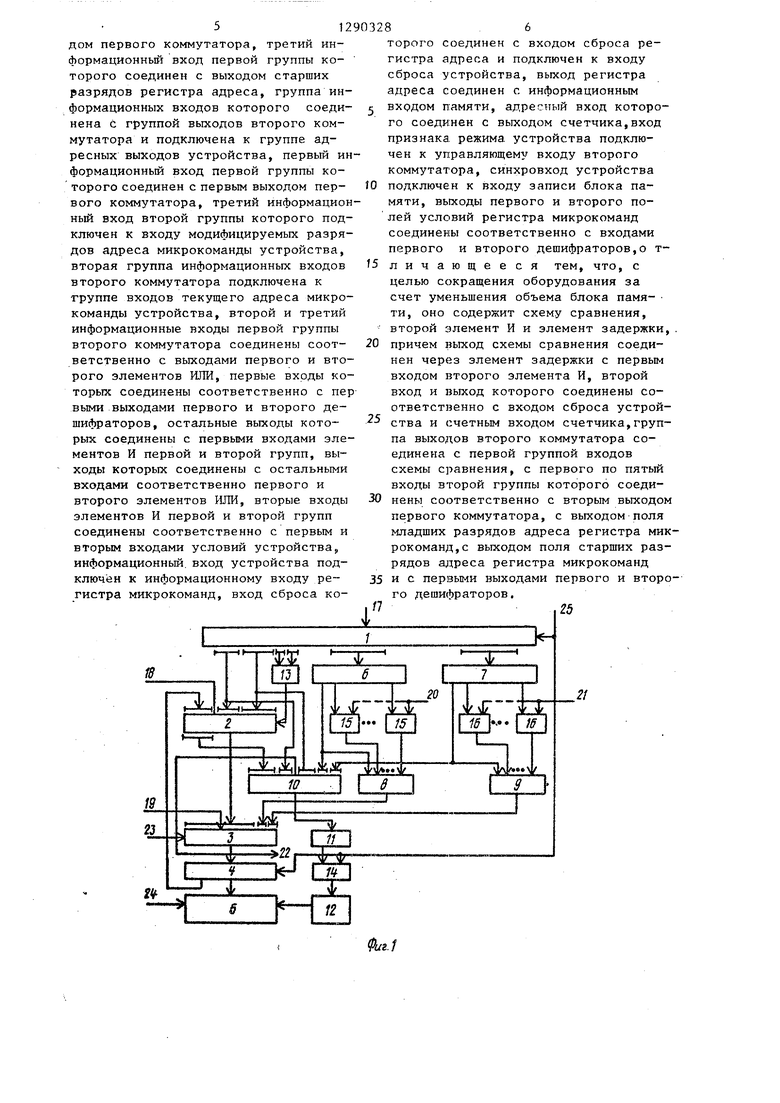

На фиг.1 приведена схема устройства хранения микропрограммной последовательности; на фиг.2 - времен нал диаграмма работы устройства; на фиг.З - фрагмент диагностируемого алгоритма микропрограммы.

Устройство содержит р-егистр 1 микрокоманд, первый 2 и второй 3 коммутаторы, регистр 4 адреса, блок 5 памяти, первый 6 и второй 7 дешифраторы, первьй 8 и второй 9 элементы ИЛИ, схему 10 сравнения,элемент 11 задержки, счетчик 12, первый 13 и второй 14 элементы Hjnep - вую группу элементов И 15, вторую группу элементов И 16, информационный вход 17, вход 18 модифицируемых разрядов адреса микрокоманды,группу 19 входов текущего адреса микрокоманды, первый вход 20 условий, второй вход .21 условий, группу 22 адресных выходов, вход 23 признака ре жима, синхровход 24, вход 25 сброса

Устройство работает следующим об разом.

Сигнал на входе 25 разрешает прохождение сигнала Несравнение на выход элемента И 14 и далее на вход счетчика 12. Значение счетчика 12 5 увеличивается на +1, и адрес следующей микрокоманды, сформированный в (п + 1)-м такте, записывается в блок 5 памяти в ячейку на единицу старше предыдущей, не затирая несравнивший- 10 ся адрес микрокоманды. Если в п-м

такте сигнал Несравнение отсутствует, то значение счетчика 12 в (п+2)-м такте остается неизменным и сравнившийся реальный адрес микрокоманды 5 после записи в -блок 5 памяти в (п+1)-м такте также затрется в (п + 2)-м такте последующим адресом.

Запоминание адресов ветвлений - средство, дающее возможность меньшим количеством запоминаемых адресов однозначно восстановить выполненную программную последовательность. Совместно с распечаткой программы можно однозначно восстановить недостающие адреса выполненной программы, а затем сравнить с заданньпу ходом программы.

На фиг.З приведен фрагмент распечатки алгоритма микропрограммы.

Б этом алгоритме над симоволом I 1 , в котором дается расшифровка микрокоманды, пишется адрес этой микрокоманды с шестнадцатиричном коде. Разветвление изображается символами

20

25

30

В каждом машинном такте на первые и вторые входы схемы 10 сравнения поступает соответственный реальный адрес следующей микрокоманды с выхода второго коммутатора 3 и ожидаемый адрес.

В случае несравнения реального и ожидаемого адресов мирокоманд на выходе схемы 10 сравнения вырабатывается сигнал Несравнение, кото- рьй поступает на вход элемента 11 задержки.

В (п + 1)-м такте происходит занесение сформированного адрвса из второго коммутатора 3 в регистр 4 адреса и новой {микрокоманды на регистр 1 микрокоманд сигналом, поступающим tio входу 25, а также запись этого адреса из регистра 4 адреса в блок 5 памяти сигналом, поступающим по входу 24 в ячейку, адресованную счетчиком 12. Вначале (п + 2)-го такта, если в п-м такте имелось несравнение адресов, на выходе элемента 11 задержки появляется сигнал Чесравне35

или

Цифрами на ветвлениях указываются значения последних битов адресов ветвлений в двоичном коде. Таким об- 40 разом, биты О или 00 на втевлении означают, что адрес этого ветвления является наименьшим из возможных адресов ветвлений.

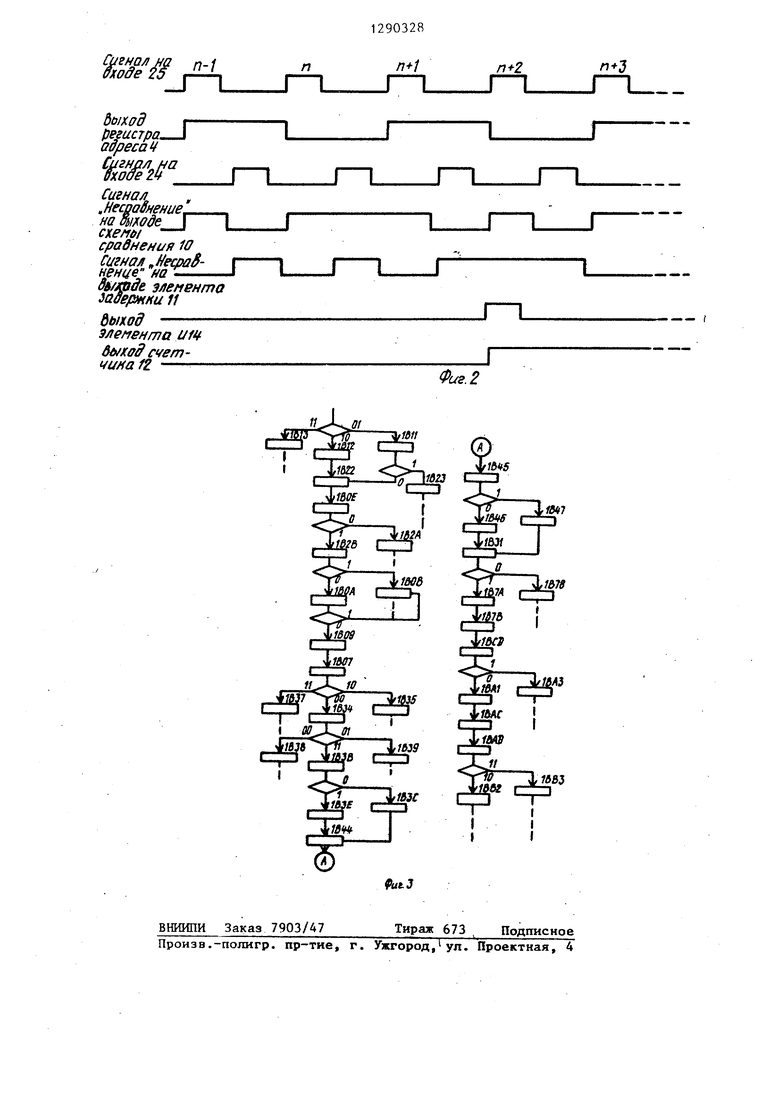

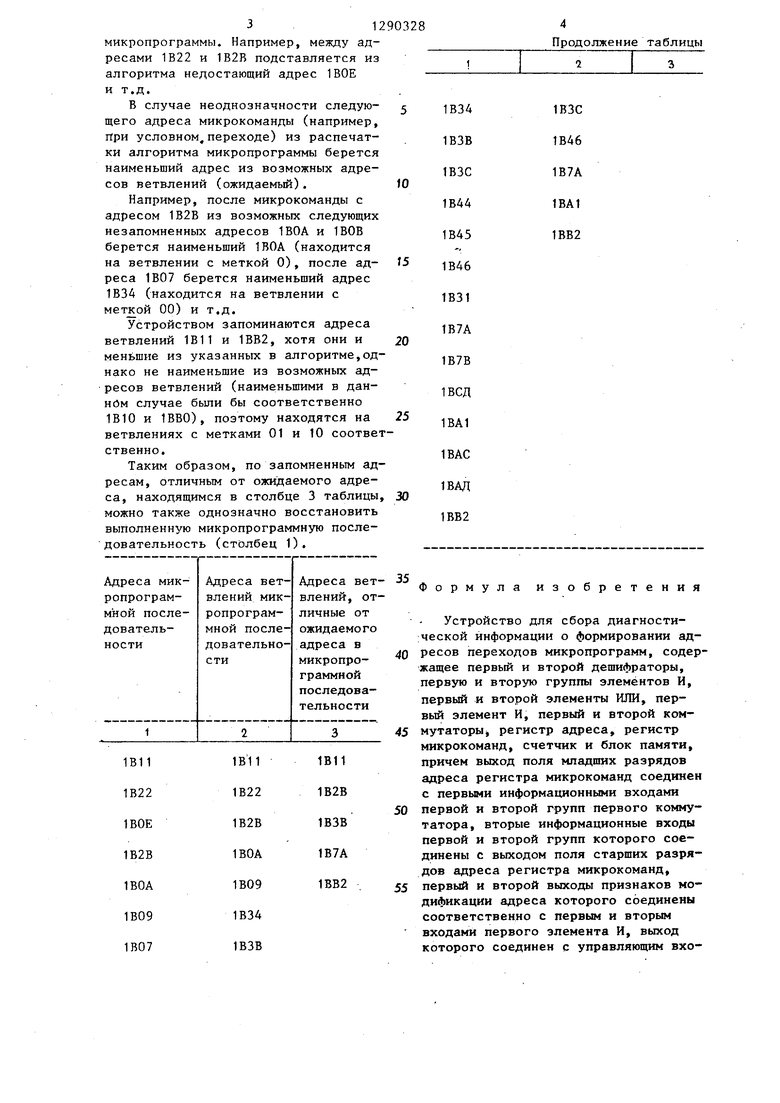

В таблице показан пример восста- 5 новления микропрограммной последовательности.

По имеющемуся алгоритму микропрограммы и запомненным адресам в столбцах 2 или 3 необходимо однозначно восстановить последовательность адресов, находящуюся в столбце 1.

50

Для восстановления выполненной микропрограммной последовательности (столбец 1) необходимо между заполненными адресами ветвлений (столбец 2) подставить недостающие адреса следующих за ними микрокоманд, которые берутся из распечатки алгоритма

312

микропрограммы. Например, между адресами 1В22 и 1В2В подставляется из алгоритма недостающий адрес 1ВОЕ и т.д.

В случае неоднозначности следую- щего адреса микрокоманды (например. При условном,переходе) из распечатки алгоритма микропрограммы берется наименьший адрес из возможных адресов ветвлений (ожидаемый).

Например, после микрокоманды с адресом 1В2В из возможных следующих незапомненных адресов 1ВОА и 1ВОВ берется наименьший 1ВОА (находится на ветвлении с меткой 0), после ад- реса 1В07 берется наименьший адрес 1В34 (находится на ветвлении с метлсой 00) и т.д.

Устройством запоминаются адреса ветвлений 1В11 и 1ВВ2, хотя они и меньшие из указанных в алгоритме,однако не наименьшие из возможных адресов ветвлений (наименьшими в данном случае были бы соответственно 1В10 и 1ВВО), поэтому находятся на ветвлениях с метками 01 и 10 соответственно.

Таким образом, по запомненным адресам, отличным от ожидаемого адреса, находящимся в столбце 3 таблицы можно также однозначно восстановить выполненную микропрограммную последовательность (столбец 1).

Продолжение таблицы

1

1ВЗС 1В46 1В7А 1ВА1 1ВВ2

35

Формула изобретения

Устройство для сбора диагностической информации о формировании ад40 ресов переходов микропрограмм, содержащее первый и второй дешифраторы, первую и вторую группы элементов И, первый и второй элементы ИЛИ, первый элемент И, первый и второй ком45 мутаторы регистр адреса, регистр микрокоманд, счетчик и блок памяти, причем выход поля младших разрядов адреса регистра микрокоманд соединен с первыми информационными входами

50 первой и второй групп первого коммутатора, вторые информационные входы первой и второй групп которого соединены с выходом поля старших разрядов адреса регистра микрокоманд,

55 первый и второй выходы признаков модификации адреса которого соединены соответственно с первым и вторым входами первого элемента И, выход которого соединен с управляющим вхо512

дом первого коммутатора, третий ин- формационньй вход первой группы которого соединен с выходом старших разрядов регистра адреса, группа информационных входов которого соеди- нена с группой выходов второго коммутатора и подключена к группе адресных выходов устройства, первый информационный вход первой группы которого соединен с первьм выходом пер- вого коммутатора, третий информационный вход второй группы которого подключен к входу модифицируемых разрядов адреса микрокоманды устройства, вторая группа информационных входов второго коммутатора подключена к группе входов текущего адреса микрокоманды устройства, второй и третий информационные входы первой группы второго коммутатора соединены соот- ветственно с выходами первого и второго элементов ИЛИ, первые входы которых соединены соответственно с пер выми выходами первого и второго дешифраторов, остальные выходы которых соединены с первыми входами элементов И первой и второй групп, выходы которых соединены с остальными входами соответственно первого и второго элементов ОТИ, вторые входы элементов И первой и второй групп соединены соответственно с первым и вторым входами условий устройства,, информационный, вход устройства под

5 0 0

5

торого соединен с входом сброса регистра адреса и подключен к входу сброса устройства, выход регистра адреса соединен с информационным входом памяти, адресный вход которого соединен с выходом счетчика,вход признака режима, устройства подключен к управляющему входу второго коммутатора, синхровход устройства подключен к входу записи блока памяти, выходы первого и второго полей условий регистра микрокоманд соединены соответственно с входами первого и второго дешифраторов,о т- личающееся тем, что, с целью сокращения оборудования за счет уменьшения объема блока памя- ти, оно содержит схему сравнения, второй элемент И и элемент задержки,. причем выход схемы сравнения соединен через элемент задержки с первым входом второго элемента И, второй вход и выход которого соединены соответственно с входом сброса устройства и счетным входом счетчика,группа выходов второго коммутатора соединена с первой группой входов схемы сравнения, с первого по пятый входы второй группы которого соединены соответственно с вторым выходом первого коммутатора, с выходом поля младших разрядов адреса регистра микрокоманд, с выходом поля старших разрядов адреса регистра микрокоманд

Сигнал ffxoffe

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1986 |

|

SU1381505A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1283761A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1322280A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1322279A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

Изобретение относится к области вычислительной техники и может применяться при диагностике неисправностей центральных устройств микропрограммных ЭВМ, Целью изобретения является сокращение оборудования за счет уменьшения объема блока. Устройство содержит схему сравнения, элемент задержки, два элемента И, два элемента ИЛИ, две группы эле-, ментов И, два дешифратора, регистр микрокоманд, два коммутатора, регистр адреса, блок памяти и счетчик. Указанная совокупность признаков позволяет достигнуть цель изобретения. 3 ил., 1 табл.

Сигнал ,НесоаОнение, на шоде скемд сравненая Ю

Сигнал HeajaS- ненце на

/jaide элемент задерзнки 11

дыход

элемента i/f

вб/Xffd cvem- t uHafZ -

Физ.2

Й5«7

ВНИШИ Заказ 7903/47

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Тираж 673

Подписное

| ЯДЕРНАЯ ПАРОПРОИЗВОДИТЕЛЬНАЯ УСТАНОВКА С РЕАКТОРОМ, ОХЛАЖДАЕМЫМ ВОДОЙ ПОД ДАВЛЕНИЕМ | 2000 |

|

RU2200990C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1983-12-19—Подача