Изобретеш е относится к вычислительной технике и может быть использовано, в частности, в автоматизированных системах контроля радиоэлектронной аппаратуры, а также в устройствах автоматики и телемеханики ,

Цель изобретения - повышение быстродействия контроля путем выявления каждого отказавшего блока без осуществления повторного запуска и пгрекоммутации,

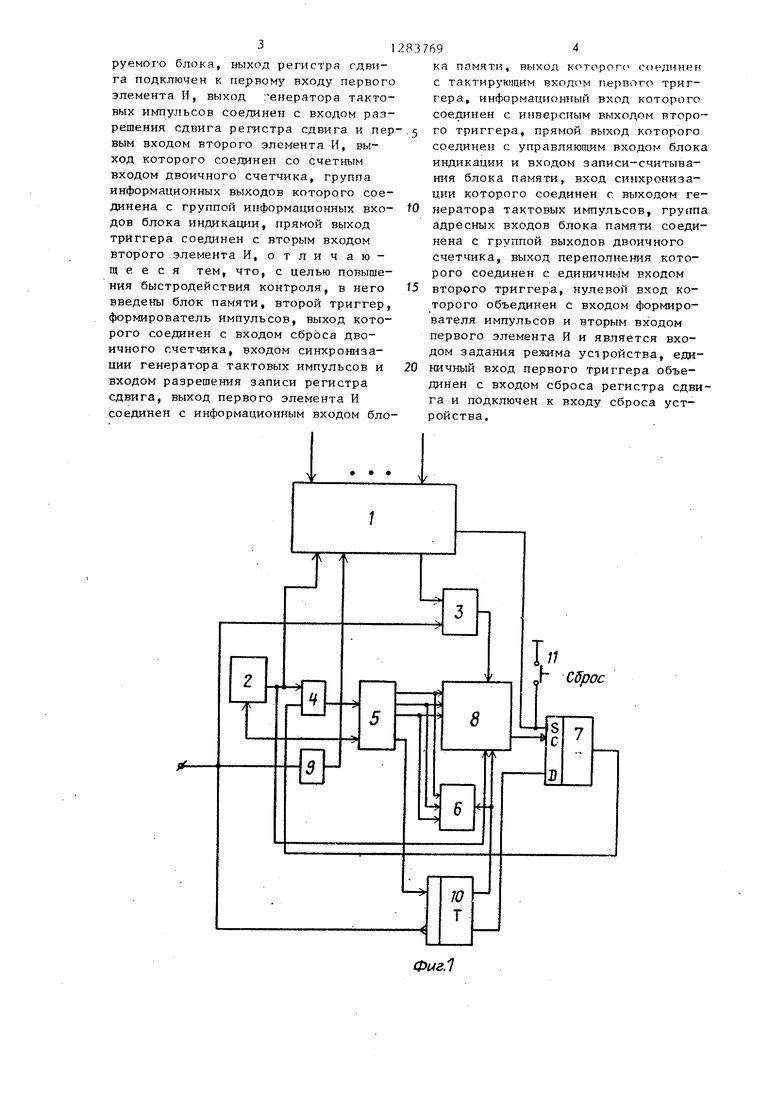

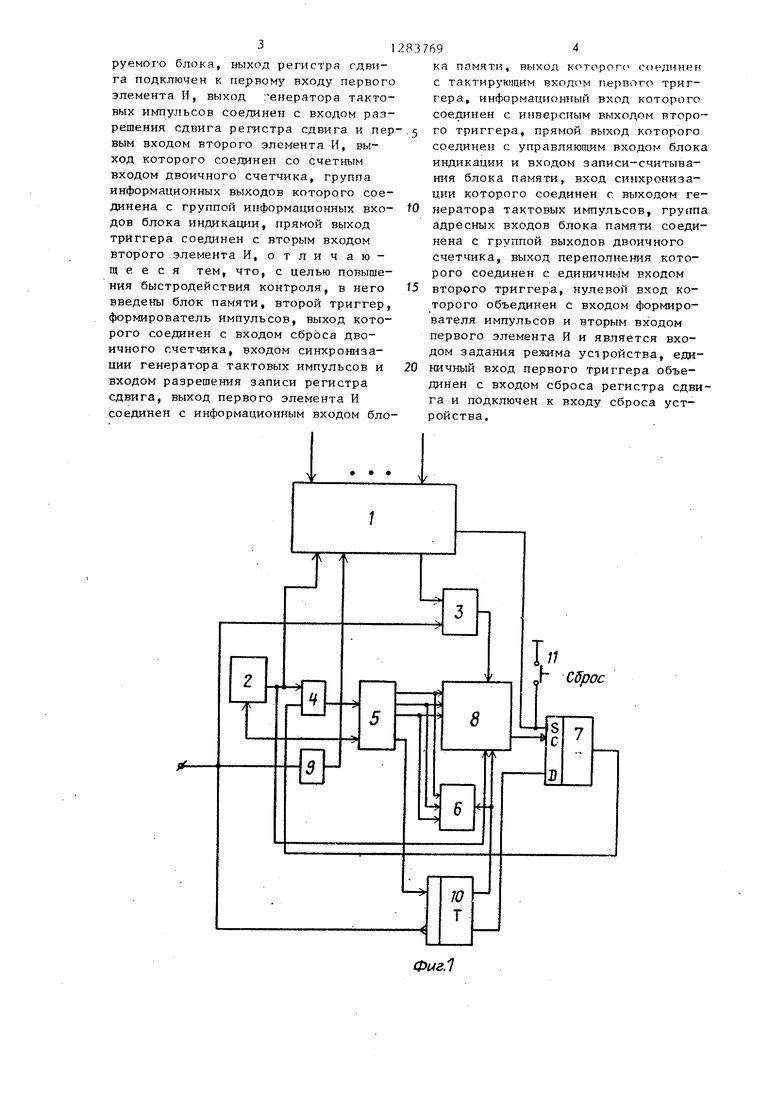

На фиг, 1 показана структурная схема устройства для контроля логических блоков; на фиг. 2 - временна диаграмма работы устройства.

Устройство содержит регистр 1 сдвига, генератор 2 тактовых импульсов, элементы И 3 и 4, двоичньй счетчик 5, блок 6 индикации, триггер 7, блок 8 памяти, формирователь 9 импульсов, второй триггер 10, вхо II сброса. Позициями 12-15 обозначены сигналы на выходах элементов устройства.

Устройство работает следующим образом.

При отсутствии команды Контроль напряжение О подается на вход элемента И 3, На вход информа1Ц1и блока памяти 8 при этом подается О, Отсутствие команды контроль ставит прямой выход второго триггера 1 в О, отключая блок индикации и определяя для блока 8 памяти режим записи. При нажатии кнопки Сброс по входу 11 происходит обнуление регистра 1 сдвига и установка выхода первого триггера 7 в 1, которая разрешает прохождение строби- рующего сигнала через вторую схему И 4 на тактирующий вход двоичного счетчика 5, По переднему фронту поступающего сигнала, т,е, переходу из низкого уровня в высокий, двоичный счетчик 5 меняет свое состояние, которое определяет адрес ячеек блока 8 памяти. Запись в блок 8 памяти осуществляется низким уровнем сигнала, поступающего с выхода генератора 2 тактовых импульсов на первый управляющий вход блока 8 памяти. Блок памяти 8 прописывается значением ноль до пор, пока не поступает команда Контроль (1), По этой команде формирователь импульса 9 ИЗ фронта управляющего сигнала устройства формирует импульс

15, которы11 обттуляет двоич1п 1Й счетчик 5, записывает входную информацию в ретттстр I сдвиг а и синхронизирует генератор 2 тактовых импульсов с поступлением команды Контроль, Это необходимо сделать, что- i бы исключить остатки импульса, поступающего с генератора 2 тактовых импульсов в момент прихода фронта сигналов Контроль 14, На нулевом входе второго триггера 10 устанавливается 1, Сигналом О на входе двоичного счетчика 5 и генератора 2 тактовых импульсов осущестапяется сброс с учетом задержек,

вносимых элементом И 4. Переход сигнала 15 из низкого в высокий осуществляется занесение информации в регистр 1 сдвига. Далее осуществляется повторная запись в ячейки блока 8 памяти той информшдии, которая была занесена в регистр 1 сдвига. Когда двоичный счетчик досчитывает до конца, т,е, прописывает все ячейки памяти (количество которых равно числу контролируемых логических блоков), на его управляющем выходе Переполнение появляется сигнал 1, которая устанавливает второй триггер

в единицу, переводя блок 8 памяти в режим считывания и включая блок 6 индикации, С инверсного выхода второго триггера 10 сигнал О поступает на установочный вход первого триггера 7, В момент, когда с блока 8 памяти считывается 1 на тактирующем входе первого триггера 7 появляется фронт, который устанавливает его выход в О, блокируя прохождение синхросигнала на вход двоичного счетчика. Блок индикации покажет номер перрого неисправного блока. При нажатии кнопки Сброс процедура чтения повторяется до тех

пор, пока снова не встретится в 6j:o- ке 8 памяти 1, указывающая номер второго неисправного блока и т.д.

Формула изобретения

Устройство для контроля логических блоков, содержащее регистр сдвига, генератрр тактовых импульсов, два элемента И, двоичный счетчик, блок индикации, триггер, причем

группа информационных входов регистра сдвига является группой информационных: входов устройства для подключения к группе выходов контролируемого блока, выход регистра сдвига подключен к первому входу первого элемента И, выход ; енбратора тактовых импульсов соединен с входом разрешения сдвига регистра сдвига и пер вым входом второго элемента Pi, выход которого соединен со Счетным входом двоичного счетчика, группа информационных выходов которого соединена с группой информационных входов блока индикации, прямой выход триггера соединен с вторым входом второго элемента И, отличающееся тем, что, с целью повышения быстродействия контроля, в него введены блок памяти, второй триггер, формирователь импульсов, выход которого соединен с входом сброса двоичного счетчика, входом синхронизации генератора тактовых импульсов и входом разрешения записи регистра сдвига, выход первого элемента И соединен с информационным входом бло837694

ка памяти, выход котороп. соединен с тактирующим входом первого трИ1- гера, информационный вход которого соединен с инверсным выходом второ.5 го триггера, прямой выход которого соединен с управляюпшм входом блока индикации и входом записи-считывания блока памяти, вход синхронизации которого соединен с выходом ге- tO нератора тактовых импульсов, группа адресных входов блока памяти соединена с группой выходов двоичного счетчика, выход переполнения которого соединен с единичным входом 5 второго триггера, нулевой вход которого объединен с входом формирователя импульсов и вторым входом первого элемента И и является входом задания режима ус1ройства, еди- 20 ничньш вход первого триггера объединен с входом сброса регистра сдвига и подключен к входу сброса устройства.

Фиг.1

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1985 |

|

SU1283771A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля фазовых искажений сигнала воспроизведения | 1987 |

|

SU1413673A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2029352C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1334146A1 |

Изобретение относится к вычислительной технике и может быть использовано, в частности, в автоматизированных системах контроля ра- диоэлектрон юй аппаратуры, а также в устройствах автоматики и телемеханики. Цель изобретения - повышение быстродействия контроля. Сущность изобретения состоит в том, что в устройство, содержащее регистр сдвига, генератор тактовых импульсов, два элемента И, двоичный счетчик, блок индикации, триггер, дополнительно введены блок памяти, второй триггер, формирователь импульсов. Устройство позволяет наря- ду с контролем неисправностей логических блоков осуществить режим запоминания отказавших блоков тестируемого устройства. 2 ил.

13

Записб

W 75

КочгтгрО/ ь

Фиг 2

Составитель Pi. Сафонова Редактор Л. Пчолинская Техред Л.Олейник Корректор А, Обручар

Заказ 7443/48Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, {Обнуление дВоичного счетчика 5

S Занесение i/ндуорма- в регистр 1

I Синкронизаци/t генератора 2

| Устройство для контроля логических блоков | 1978 |

|

SU723578A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля неисправностей | 1982 |

|

SU1024922A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-13—Подача