Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых объектов.

Цель изобретения - повьш1ение точности анализатора.

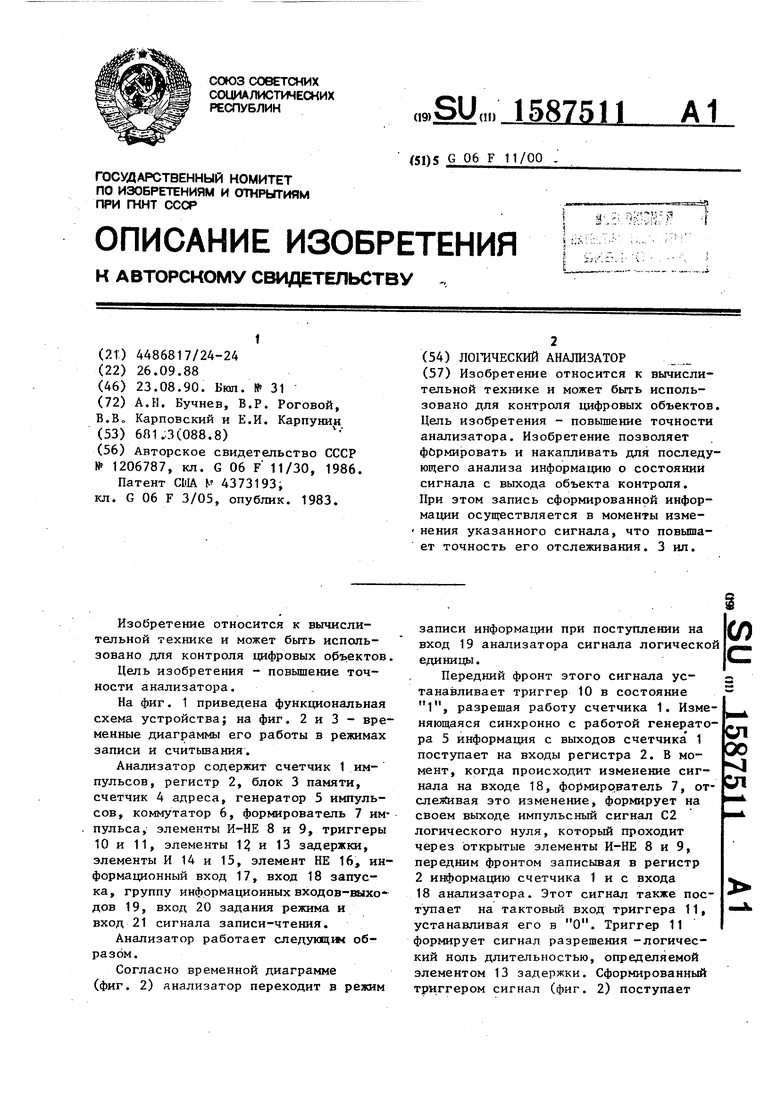

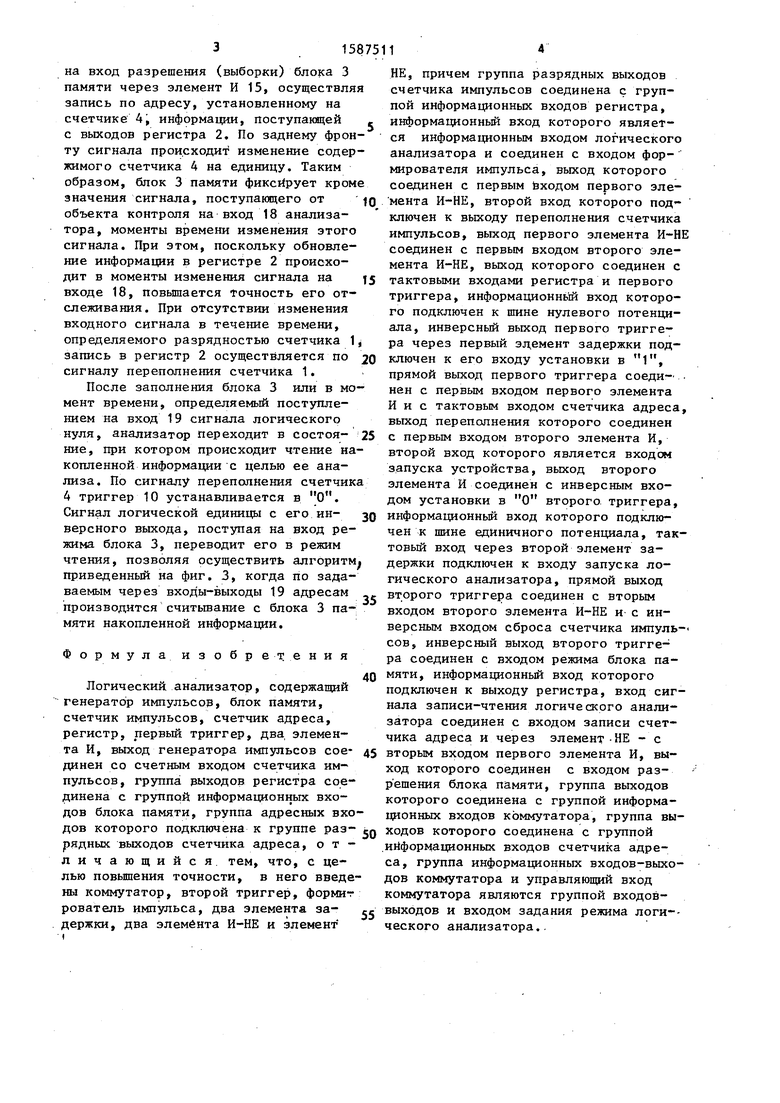

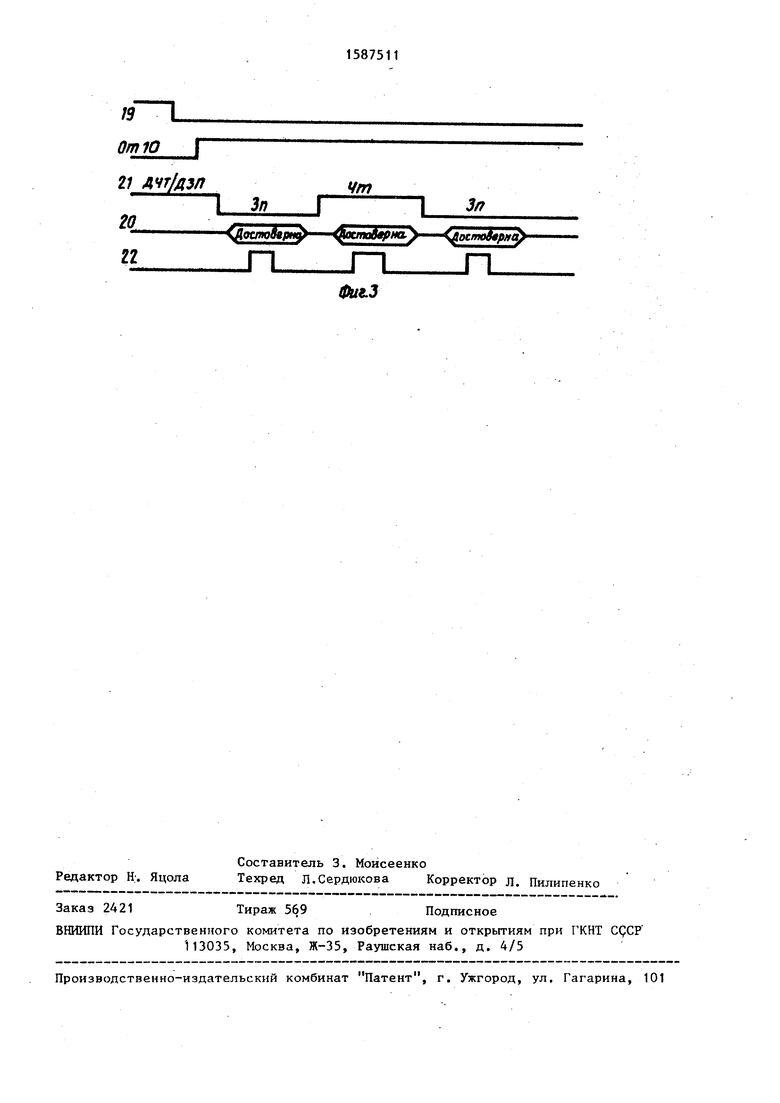

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 и 3 - временные диаграммы его работы в режимах записи и считьшания.

Анализатор содержит счетчик 1 импульсов, регистр 2, блок 3 памяти, счетчик 4 адреса, генератор 5 импульсов, коммутатор 6, формирователь 7 им- пульса, элементы И-НЕ 8 и 9, триггеры 10 и 11, элементы 1 и 13 задержки, элементы И 14 и 15, элемент НЕ 16, информационный вход 17, вход 18 запуска, группу информационных входов-выхо - дов 19, вход 20 задания режима и вход 21 сигнала записи-чтения.

Анализатор работает следзпощш образом.

Согласно временной диаграмме (фиг. 2) анализатор переходит в режим

записи информации при поступлении на вход 19 анализатора сигнала логической единицы.

Передний фронт этого сигнала устанавливает триггер 10 в состояние 1, разрешая работу счетчика 1. Изменяющаяся синхронно с работой генератора 5 информация с выходов счетчика 1 поступает на входы регистра 2. В момент, когда происходит изменение сигнала на входе 18, формирователь 7, от- слелСивая это изменение, формирует на своем выходе импульсный сигнал С2 логического нуля, который проходит через открытые элементы И-НЕ 8 и 9, передним фронтом записывая в регистр 2 информацию счетчика 1 и с входа 18 анализатора. Этот сигнал также поступает на тактовый вход триггера 11, устанавливая его в О. Триггер 11 i формирует сигнал разрешения -логический ноль длительностью, определяемой элементом 13 задержки. Сформированный триггером сигнал (фиг. 2) поступает

(Л

с

ел

00

| сд

315875

на вход разрешения (выборки) блока 3 памяти через элемент И 15, осуществляя запись по адресу, установленному на счетчике 4, информации, поступающей с выходов регистра 2, По заднему фронту сигнала происходит изменение содержимого счетчика 4 на единицу. Таким образом, блок 3 памяти фиксирует кроме значения сигнала, поступанщего от Q объекта контроля на вход 18 анализатора, моменты времени изменения этого сигнала. При этом, поскольку обновление информации в регистре 2 происходит в моменты изменения сигнала на 15 входе 18, повьшается точность его отслеживания. При отсутствии изменения входного сигнала в течение времени, определяемого разрядностью счетчика 1, запись в регистр 2 осуществляется по 20 сигналу переполнения счетчика 1.

После заполнения блока 3 или в мо- мент времени, определяемый поступлением на вход 19 сигнала логического нуля, анализатор переходит в состоя- 25 ние, при котором происходит чтение накопленной информации с целью ее анализа. По сигналу переполнения счетчика 4 триггер 10 устанавливается в О.

НЕ, причем группа разрядных выходов счетчика импульсов соединена с группой информационных входов регистра, информационньй вход которого является информационным входом логическог анализатора и соединен с входом формирователя импульса, выход которого соединен с первым йходом первого эле мента И-НЕ, второй вход которого под ключен к выходу переполнения счетчик импульсов, выход первого элемента Исоединен с первым входом второго эле мента И-НЕ, выход которого соединен тактовыми входами регистра и первого триггера, информационньй вход которо го подключен к шине нулевого потенци ала, инверсный выход первого триггера через первый эдемент задержки под ключен к его входу установки в 1, прямой выход первого триггера соеди- нен с первым входом первого элемента И и с тактовым входом счетчика адрес выход переполнения которого соединен с первьш входом второго элемента И, второй вход которого является входом запуска устройства, выход второго элемента И соединен с инверсным входом установки в О второго триггера

Сигнал логической единицы с его ин- зО информационньй вход которого подклюверсного выхода, поступая на вход режима блока 3, переводит его в режим чтения, позволяя осуществить алгоритм, приведенный на фиг. 3, когда по задаваемым через входы-выходы 19 адресам производится считьшание с блока 3 памяти накопленной информации.

Формула изобретения

чен к шине единичного потенциала, так товый вход через второй элемент задержки подключен к входу запуска логического анализатора, прямой выход 2J второго триггера соединен с вторым входом второго элемента И-НЕ и с инверсным входом сброса счетчика импуль сов, инверсный выход второго триггера соединен с входом режима блока па- до мяти, информационньй вход которого

Логический анализатор, содержащий генератор импульсов, блок памяти, счетчик импульсов, счетчик адреса, регистр, первый триггер, два, элемента И, выход генератора импульсов соединен со счетным входом счетчика импульсов, группа выходов регистра соединена с группой информационных входов блока памяти, группа адресных входов которого подключена к группе раз- рядных выходов счетчика адреса, отличающийся тем, что, с целью повьшения точности, в него введены коммутатор, второй триггер, формит рователь импульса, два элемента задержки, два элемента И-НЕ и элемент

НЕ, причем группа разрядных выходов счетчика импульсов соединена с группой информационных входов регистра, информационньй вход которого является информационным входом логического анализатора и соединен с входом формирователя импульса, выход которого соединен с первым йходом первого элемента И-НЕ, второй вход которого подключен к выходу переполнения счетчика импульсов, выход первого элемента ИН соединен с первым входом второго элемента И-НЕ, выход которого соединен с тактовыми входами регистра и первого триггера, информационньй вход которого подключен к шине нулевого потенциала, инверсный выход первого триггера через первый эдемент задержки подключен к его входу установки в 1, прямой выход первого триггера соеди- нен с первым входом первого элемента И и с тактовым входом счетчика адреса выход переполнения которого соединен с первьш входом второго элемента И, второй вход которого является входом запуска устройства, выход второго элемента И соединен с инверсным входом установки в О второго триггера.

информационньй вход которого подклю

чен к шине единичного потенциала, тактовый вход через второй элемент задержки подключен к входу запуска логического анализатора, прямой выход второго триггера соединен с вторым входом второго элемента И-НЕ и с инверсным входом сброса счетчика импуль- сов, инверсный выход второго триггера соединен с входом режима блока па- мяти, информационньй вход которого

eg

подключен к выходу регистра, вход сигнала записи-чтения логического анализатора соединен с входом записи счетчика адреса и через элемент-НЕ - с 45 вторым входом первого элемента И, выход которого соединен с входом разрешения блока памяти, группа выходов которого соединена с группой информационных входов коммутатора, группа выходов которого соединена с группой .ийформационных входов счетчика адреса, группа информационных входов-выхоeg

55

дов коммутатора и управляющий вход коммутатора являются группой входов- выходов и входом задания режима логического анализатора..

19

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1985 |

|

SU1283771A1 |

| Устройство для регистрации результатов контроля | 1985 |

|

SU1406596A1 |

| Устройство для регистрации состояний контролируемого блока | 1984 |

|

SU1236488A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1283769A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645959A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Логический анализатор | 1989 |

|

SU1734093A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых объектов. Цель изобретения - повышение точности анализатора. Изобретение позволяет формировать и накапливать для последующего анализа информацию о состоянии сигнала с выхода объекта контроля. При этом запись сформированной информации осуществляется в моменты изменения указанного сигнала, что повышает точность его отслеживания. 3 ил.

LTuifi ruinjmju

/8.

СЛ1.1

niJTJ JTriJnjTjrLr

фуг.Л

| Авторское свидетельство СССР № 1206787, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент CLIA - 4373193; кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Роговой, Карпуни11 | |||

Авторы

Даты

1990-08-23—Публикация

1988-09-26—Подача