Изобретение относится к системам передачи дискретной информации по каналам связи и может быть использовано при синхронной обработке сообщений для формирования последова- тельностей синхроимпульсов,

Цель изобретения - увеличение точности синхронизации при уменьшении отношения мощности сигнала к

мощности птума.

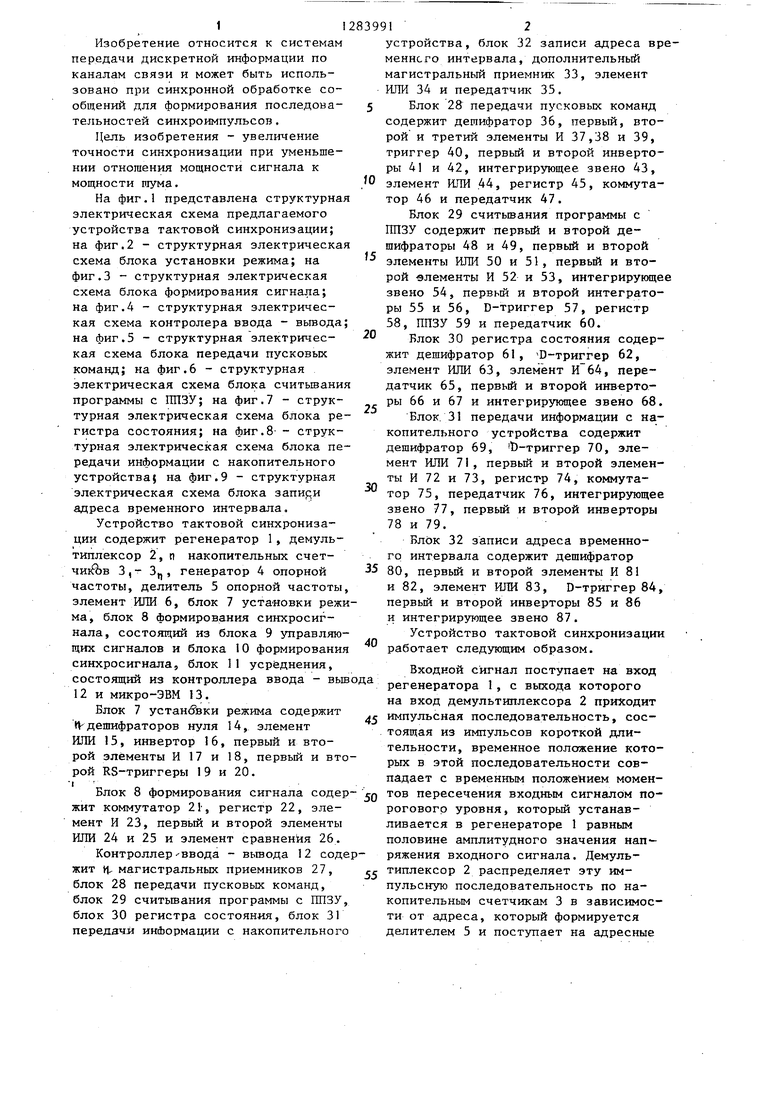

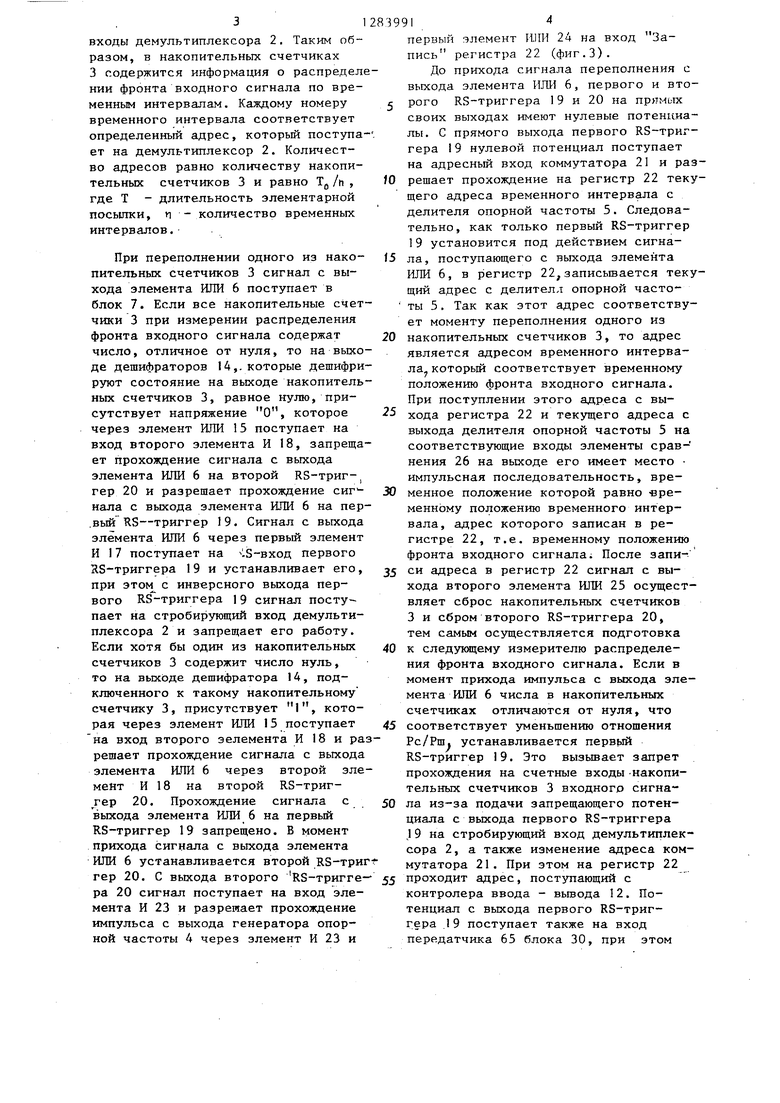

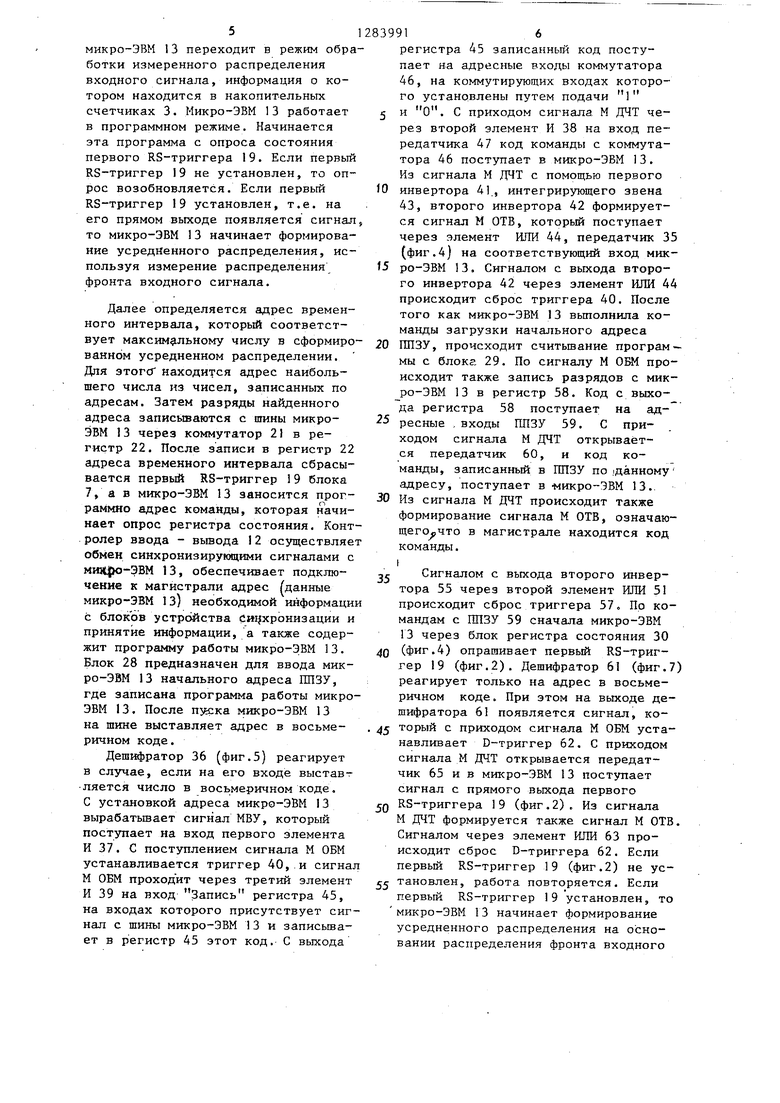

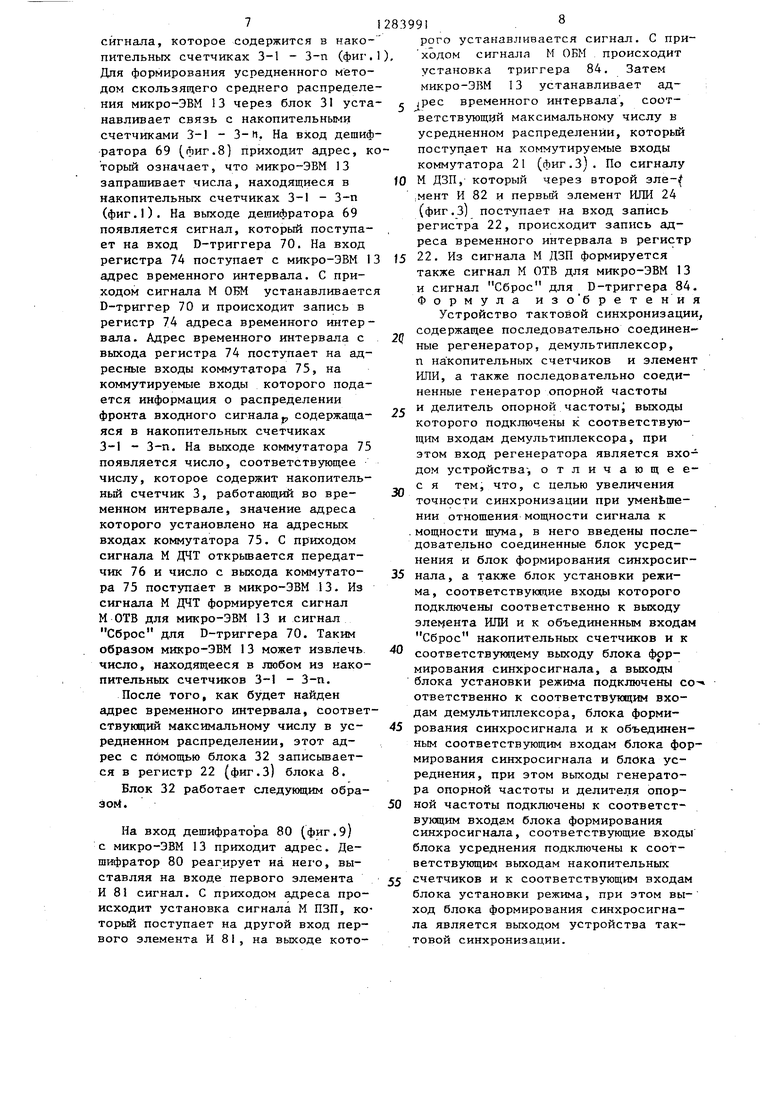

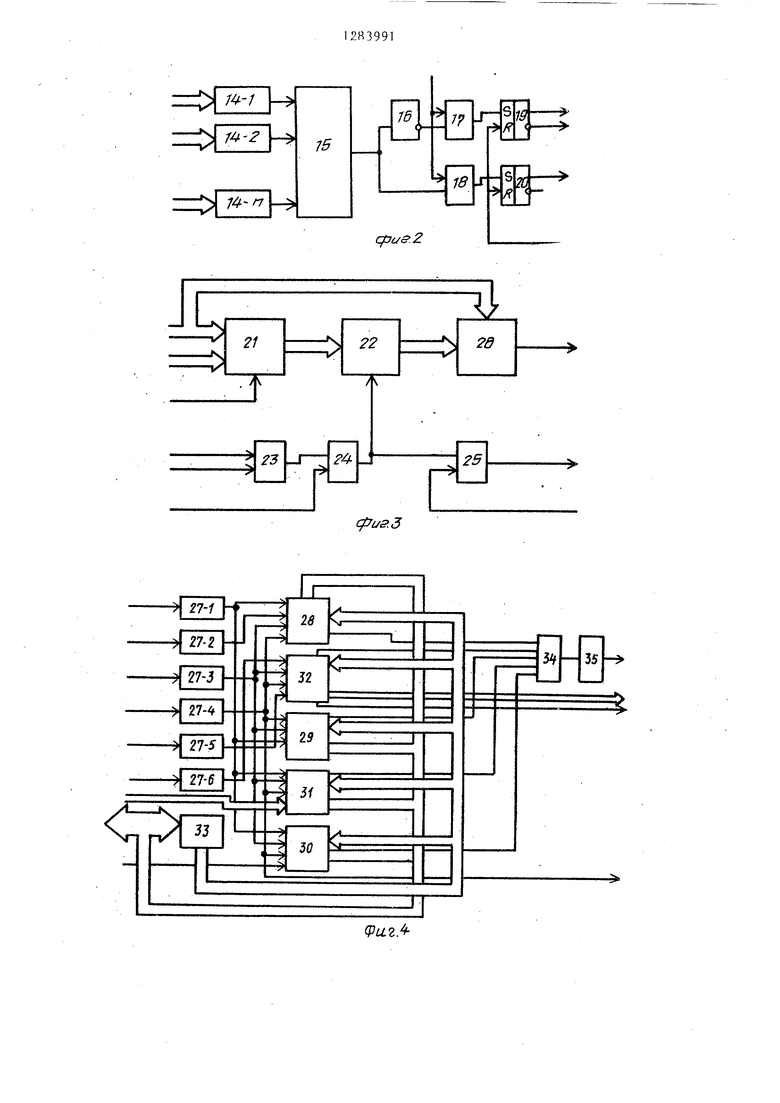

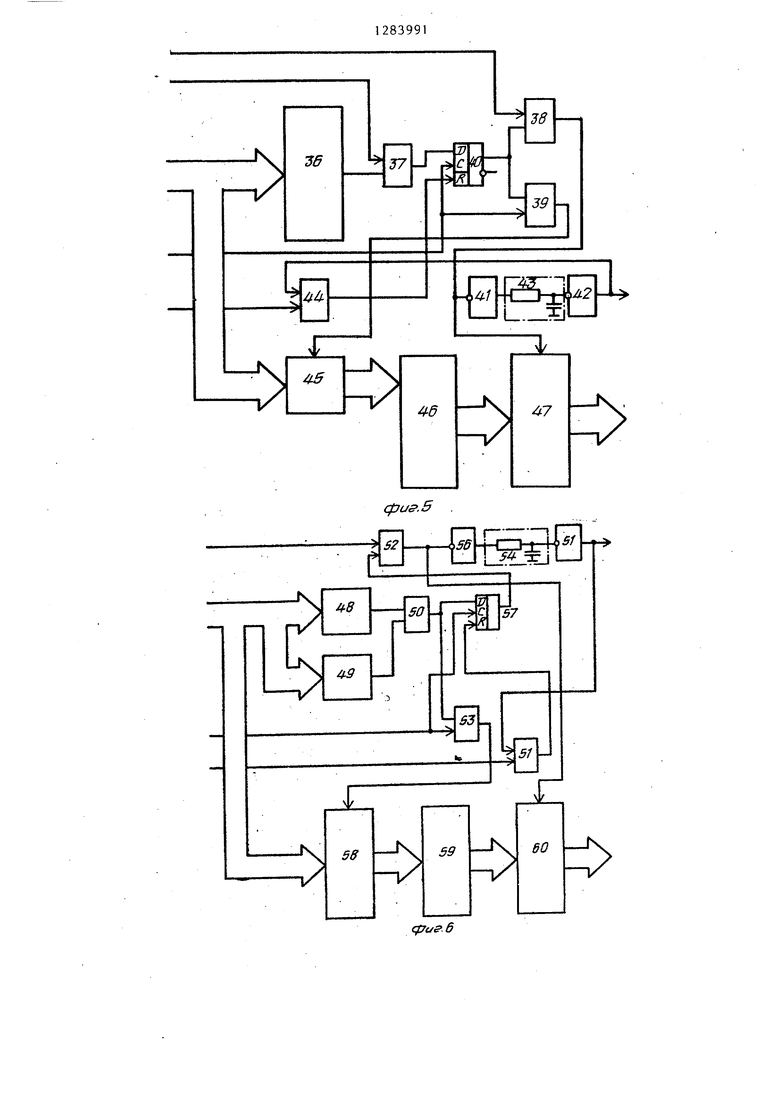

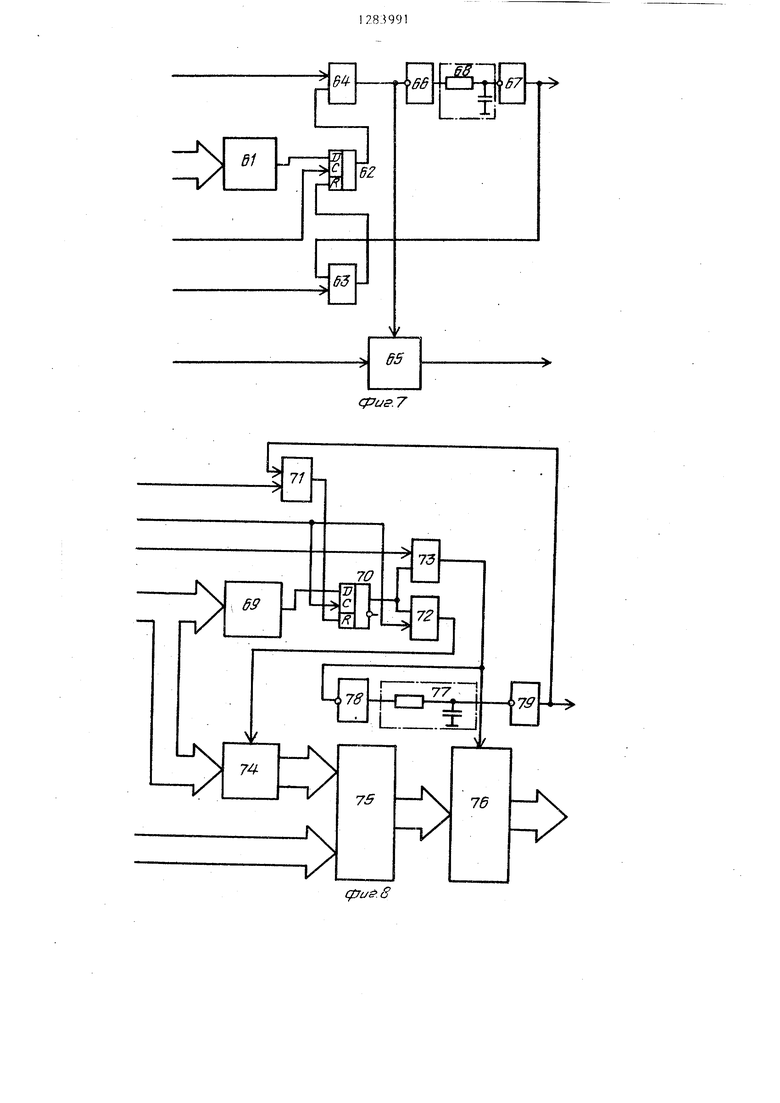

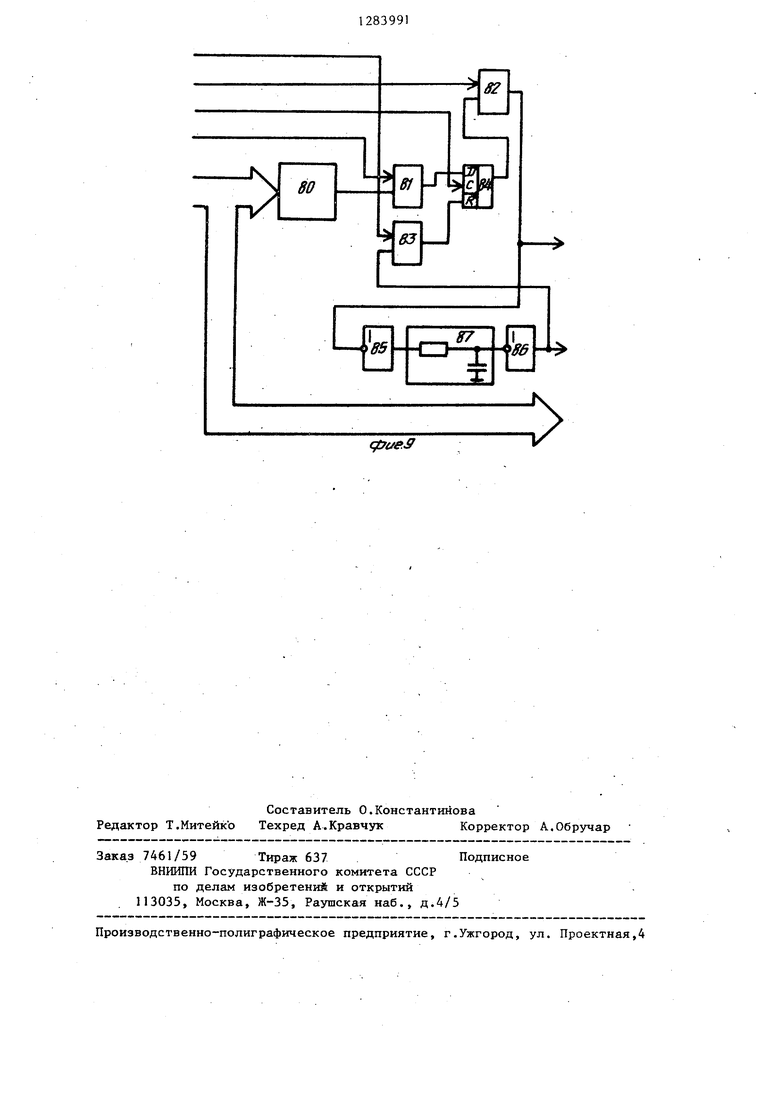

На фиг.1 представлена структурная электрическая схема предлагаемого устройства тактовой синхронизации; на фиг.2 - структурная электрическая схема блока установки режима; на фиг.З - структурная электрическая схема блока формирования сигнала; на фиг.4 - структурная электрическая схема контролера ввода - вьтода; на фиг.З - структурная электричес- кал схема блока передачи пусковых команд; на фиг.6 - структурная электрическая схема блока считьшания программы с ППЗУ; на фиг.7 - структурная электрическая схема блока регистра состояния; на фиг.8- - структурная электрическая схема блока передачи информации с накопительного устройства} на фиг.9 - структурная электрическая схема блока записи адреса временного интервала.

Устройство тактовой синхронизации содержит регенератор 1, демуль- типлексор 2, л накопительных счет- 3 , - 3„ , генератор 4 опорной частоты, делитель 5 опорной частоты, элемент ИЛИ 6, блок 7 установки режима, блок 8 формирования синхросигнала, состоящий из блока 9 управляющих сигналов и блока 10 формирования синхросигнала, блок 11 усреднения, состоящий из контроллера ввода - вьш 12 и микро-ЭВМ 13.

Блок 7 установки режима содержит tVдешифраторов нуля 14, элемент ШТИ 15, инвертор 16, первый и второй элементы И 17 и 18, первый и второй RS-триггеры 19 и 20.

Блок В формирования сигнала содер жит коммутатор 21, регистр 22, элемент И 23, первый и второй элементы ИЛИ 24 и 25 и элемент сравнения 26.

Контроллер--ввода - вьшода 12 содежит tv магистральных приемников 27, блок 28 передачи пусковых команд, блок 29 считьшания программы с ГШЗУ, блок 30 регистра состояния, блок 31 передачи информации с накопительного

5

0

f5

5

0

0

З а

Q

гг

0

45

устройства, блок 32 записи адреса временного интервала, дополнительный магистральньй приемник 33, элемент ИЛИ 34 и передатчик 35.

Блок 28 передачи пусковых команд содержит дешифратор 36, первый, второй и третий элементы И 37,38 и 39, триггер 40, первый и второй инверторы 41 и 42, интегрирующее звено 43, элемент ИЛИ 44, регистр 45, коммутатор 46 и передатчик 47.

Блок 29 считьшания программы с ППЗУ содержит первый и второй де- щифраторы 48 и 49, первый и второй элементы ИЛИ 50 и 51, первьй и второй -элементы И 52 и 53, интегрирующее звено 54, первый и второй интеграторы 55 и 56, D-триггер 57, регистр 58, ППЗУ 59 и передатчик 60.

Блок 30 регистра состояния содержит дешифратор 61, D-триггер 62, элемент ИЛИ 63, элемент И 64, передатчик 65, первый и второй инверторы 66 и 67 и интегрирующее звено 68.

Блок. 31 передачи информации с накопительного устройства содержит дешифратор 69, Ъ-триггер 70, элемент ИЖ 71, первый и второй элементы И 72 и 73, регистр 74, коммутатор 75, передатчик 76, интегрирующее звено 77, первый и второй инверторы 78 и 79.

Блок 32 записи адреса временного интервала содержит дещифратор 80, первый и второй элементы И 81 и 82, элемент ИЛИ 83, D-триггер 84, первый и второй инверторы 85 и 86 и интегрирующее звено 87.

Устройство тактовой синхронизации работает следующим образом.

Входной сигнал поступает на вход регенератора 1, с выхода которого на вход демультштлексора 2 приходит импульсная последовательность, состоящая из импульсов короткой длительности, временное положение которых в этой последовательности совпадает с временньм положением моментов пересечения входным сигналом порогового уровня, который устанавливается в регенераторе 1 равным половине амплитудного значения нап ряжения входного сигнала. Демуль- типлексор 2 распределяет эту импульсную последовательность по накопительным счетчикам 3 в зависимости от адреса, который формируется делителем 5 и поступает на адресные

входы демультиплексора 2, Таким образом, в накопительных счетчиках 3 содержится информация о распределении фронта входного сигнала по временным интервалам. Каждому номеру временного интервала соответствует определенный адрес, который поступает на демультиплексор 2. Количество адресов равно количеству накопительных счетчиков 3 и равно Т /п , где Т - длительность элементарной посыпки, п - количество временных интервалов.

При переполнении одного из накопительных счетчиков 3 сигнал с выхода элемента ИЛИ 6 поступает в блок 7. Если все накопительные счетчики 3 при измерении распределения фронта входного сигнала содержат число, отличное от нуля, то на выходе дешифраторов 14,.которые дешифрируют состояние на выходе накопительных счетчиков 3, равное нулю, присутствует напряжение О, которое через элемент ИЛИ 15 поступает на вход второго элемента И 18, запрещает прохождение сигнала с выхода элемента ИЛИ 6 на второй RS-триг-, гер 20 и разрешает прохождение сиг - напа с выхода элемента ИЛИ 6 на пер- .вый RS-триггер 19. Сигнал с выхода элемента ИЛИ 6 через первый элемент И I7 поступает на чЗ-вход первого RS-триггера 19 и устанавливает его, при этом с инверсного выхода первого RS-триггера 19 сигнал поступает на стробиругощий вход демультиплексора 2 и запрещает его работу. Если хотя бы один из накопительных счетчиков 3 содержит число нуль, то на выходе дешифратора 14, подключенного к такому накопительному счетчику 3, присутствует 1, которая через элемент ИЛИ 15 поступает на вход второго эелемента И 18 и раз рещает прохождение сигнала с выхода элемента ИЛИ 6 через второй элемент И 18 на второй RS-триг- ер 20. Прохождение сигнала с выхода элемента ИЛИ 6 на первый RS-триггер 19 запрещено. В момент прихода сигнала с выхода элемента ИЛИ 6 устанавливается второй RS-триг гер 20. С выхода второго RS-тригге- ра 20 сигнал поступает на вход элемента И 23 и разрешает прохождение импульса с выхода генератора опорной частоты 4 через элемент И 23 и

83991

первый элемент ПНИ 24 на вход Запись регистра 22 (фиг.З).

До прихода сигнала переполнения с выхода элемента ИЛИ 6, первого и вто- г рого RS-TpHrrepa 19 и 20 на своих выходах имеют нулевые потенциалы. С прямого выхода первого RS-триггера 19 нулевой потенциал поступает на адресный вход коммутатора 21 и раз10 решает прохождение на регистр 22 текущего адреса временного интервала с делителя опорной частоты 5. Следовательно, как только первый RS-триггер 19 установится под действием сигнаf5 ла, поступающего с выхода элемента

ИЛИ 6, в регистр 22,записьтается текущий адрес с делителя опорной часто- ты 5. Так как этот адрес соответствует моменту переполнения одного из

20 накопительных счетчиков 3, то адрес является адресом временного интервала который соответствует временному положению фронта входного сигнала. При поступлении этого адреса с хода регистра 22 и текущего адреса с выхода делителя опорной частоты 5 на соответствующие входы элементы срав- нения 26 на выходе его имеет место импульсная последовательность, вре30 менное положение которой равно «ременному положению временного интервала, адрес которого записан в регистре 22, т.е. временному положению фронта входного сигнала; После запи35 си адреса в регистр 22 сигнал с выхода второго элемента ИЛИ 25 осуществляет сброс накопительных счетчиков 3 и сбром второго RS-триггера 20, тем самым осуществляется подготовка

40 к следукнцему измерителю распределения фронта входного сигнала. Если в момент прихода импульса с выхода элемента ИЛИ 6 числа в накопительных счетчиках отличаются от нуля, что

45 соответствует уменьшению отнощения Рс/Рш. устанавливается первый RS-триггер 19. Это вызывает запрет прохождения на счетные входы -накопительных счетчиков 3 входного сигна50 ла из-за подачи запрещающего потенциала с выхода первого RS-триггера ,19 на стробирующий вход демультиплексора 2, а также изменение адреса коммутатора 21. При этом на регистр 22

55 проходит адрес, поступающий с

контролера ввода - вьшода 12. Потенциал с выхода первого RS-триггера .19 поступает также на вход передатчика 65 блока 30, при этом

микро-ЭВМ 13 переходит в режим обработки измеренного распределения входного сигнала, информация о котором находится в накопительных счетчиках 3. Микро-ЭВМ 13 работает в программном режиме, Начинается эта программа с опроса состояния первого RS-триггера 19. Если первый RS-триггер 19 не установлен, то опрос возобновляется. Если первый RS-триггер 19 установлен, т.е. на его прямом выходе появляется сигнал то микро-ЭВМ 3 начинает формирование усредненного распределения, используя измерение распределения фронта входного сигнала.

Далее определяется адрес временного интервала, который соответствует максимальному числу в сформированном усредненном распределении. Для этогсГ находится адрес наибольшего числа из чисел, записанных по адресам. Затем разряды найденного адреса записьшаются с шины микро- ЭВМ 13 через коммутатор 21 в регистр 22. После записи в регистр 22 адреса временного интервала сбрасывается первый RS-триггер 19 блока 7, а в микро-ЭВМ 13 заносится программно адрес команды, которая начинает опрос регистра состояния. Контролер ввода - вьшода 12 осуществляе обмен синхронизирующими сигналами с мияфо-ЭВМ 13, обеспечивает подключение к магистрали адрес (данные микро-ЭВМ 1З) необходимой информаци с блоков устройства Си1|хронизации и принятие информации, а также содержит программу работы микро-ЭВМ 13. Блок 28 предназначен для ввода микро-ЭВМ 13 начального адреса ППЗУ, где записана программа работы микро ЭВМ 13. После микро-ЭВМ 13 на шине выставляет адрес в восьмеричном коде.

Дешифратор 36 (фиг.5) реагирует в случае, если на его входе выстав- ляется число в вось.меричном коде. С установкой адреса микро-ЭВМ 13 вырабатьшает сигнал МВУ, который поступает на вход первого элемента И 37. С поступлением сигнала М ОБМ устанавливается триггер 40,.и сигна М ОБМ проходит через третий элемент И 39 на вход Запись регистра 45, на входах которого присутствует сигнал с шины микро-ЭВМ 13 и записьша- ет в регистр 45 этот код. С выхода

839916

регистра 45 записанный код поступает на адресные входы коммутатора 46, на коммутирующих входах которого установлены путем подачи 1

5 и О. С приходом сигнала М ДЧТ через второй элемент И 38 на вход передатчика 47 код команды с коммутатора 46 поступает в микро-ЭВМ 13. Из сигнала М ДЧТ с помощью первого

Ш инвертора 4., интегрирующего звена 43, второго инвертора 42 формируется сигнал М ОТВ, который поступает через элемент ИЛИ 44, передатчик 35 (фиг.4) на соответствующий вход микt5 ро-ЭВМ 13. Сигналом с выхода второго инвертора 42 через элемент ИЛИ 44 происходит сброс триггера 40. После того как микро-ЭВМ 13 вьшолнила команды загрузки начального адреса

20 ППЗУ, происходит считьтание программы с блока 29. По сигналу М ОБМ происходит также запись разрядов с микро-ЭВМ 13 в регистр 58. Код с выхода регистра 58 поступает на ад ресные , входы ППЗУ 59. С приходом сигнала М ДЧТ открывается передатчик 60, и код команды, записанный в ППЗУ поданному адресу, поступает в -микро-ЭВМ 13..

30 Из сигнала М ДЧТ происходит также формирование сигнала М ОТВ, означаю- в магистрале находится код команды.

jr Сигналом с выхода второго инвертора 55 через второй элемент ИЛИ 51 происходит сброс триггера 57. По командам с ППЗУ 59 сначала микро-ЭВМ 13 через блок регистра состояния 30

40 (фиг.4) опрашивает первый RS-триггер 19 (фиг.2). Дешифратор 61 (фиг.7) реагирует только на адрес в восьмеричном коде. При этом на выходе дешифратора 61 появляется сигнал, ко- . 45 торый с приходом сигнала М ОБМ устанавливает D-триггер 62. С приходом сигнала М ДЧТ открывается передатчик 65 и в микро-ЭВМ 13 поступает сигнал с прямого выхода первого

5Q RS-триггера 19 (фиг.2). Из сигнала М ДЧТ формируется также сигнал М ОТВ. Сигналом через элемент ИЛИ 63 происходит сброс D-триггера 62. Если первьй RS-триггер 19 (фиг.2) не ус55 тановлен, работа повторяется. Если

первый RS-триггер 19 установлен, то микро-ЭВМ 13 начинает формирование усредненного распределения на основании распределения фронта входного

сигнала, которое содержится в накопительных счетчиках 3-1 - 3-п (фиг Для формирования усредненного методом скользящего среднего распределения микро-ЭВМ 13 через блок 31 устанавливает связь с накопительными счетчиками 3-1 - 3-н. На вход дешифратора 69 (Лиг.8) приходит адрес, к торый означает, что микро-ЭВМ 13 запрашивает числа, находящиеся в накопительных счетчиках 3-1 - 3-п (фиг.1). На выходе дешифратора 69 появляется сигнал, который поступает на вход D-триггера 70. На вход регистра 74 поступает с микро-ЭВМ 1 адрес временного интервала. С приходом сигнала М ОБМ устанавливаетс D-триггер 70 и происходит запись в регистр 74 адреса временного интер - вала. Адрес временного интервала с выхода регистра 74 поступает на адресные входы коммутатора 75, на коммутируемые входы которого подается информация о распределении фронта входного сигнала j, содержащаяся в накопительных счетчиках 3-1 - 3-п. На выходе коммутатора 75 появляется число, соответствующее числу, которое содержит накопительный счетчик 3, работающий во временном интервале, значение адреса которого установлено на адресных входах коммутатора 75. С приходом сигнала М ДЧТ открывается передатчик 76 и число с выхода коммутатора 75 поступа:ет в микро-ЭВМ 13. Из сигнала М ДЧТ формируется сигнал М ОТВ для микро-ЭВМ 13 и сигнал Сброс для D-триггера 70. Таким образом микро-ЭВМ 13 может извлечь число, находящееся в любом из накопительных счетчиков 3-1 - 3-п.

После того, как будет найден адрес временного интервала, соответствующий максимальному числу в усредненном распределении, этот адрес с пбмощью блока 32 записьшает- ся в регистр 22 (фиг.З) блока 8.

Блок 32 работает следующим обра- 3ort.

На вход дешифратора 80 (фиг.9) с микро-ЭВМ 13 приходит адрес. Дешифратор 80 реагирует на него, выставляя на входе первого элемента И 81 сигнал. С приходом адреса происходит установка сигнала М ПЗП, который поступает на другой вход первого элемента И 8I, на выходе кото2

рого устанавливается сигнал. С при- , ходом сигнала Ы ОБМ происходит

установка триггера 84. Затем

микро-ЭВМ 13 устанавливает ад- с jpec временного интервала, соответствующий максимальному числу в усредненном распределении, который поступает на коммутируемые входы коммутатора 21 (фиг.З). По сигналу (О М ДЗП, который через второй эле-( .мент И 82 и первый элемент ИЛИ 24

(фиг.З) пост-упает на вход запись регистра 22, происходит запись адреса временного интервала в регистр (5 22. Из сигнала М ДЗП формируется также сигнал М ОТВ для микро-ЭВМ 13 и сигнал Сброс для D-триггера 84. Формула изо бретения Устройство тактовой синхронизации, содержащее последовательно соединенные регенератор, демультиплексор, п накопительных счетчиков и элемент ИЛИ, а также последовательно соединенные генератор опорной частоты 2г и делитель опорной частотыj выходы которого подключены к соответствующим входам демультиплексора, при этом вход регенератора является входом устройства, отличающе е- с я тем, что, с целью увеличения точности синхронизации при уменьшении отношения мощности сигнала к .мощности шума, в него введены последовательно соединенные блок усреднения и блок формирования синхросиг- 35 нала, а также блок установки режима, соответствующие входы которого подключены соответственно к выходу ИЛИ и к объединенным входам Сброс накопительных счетчиков и к соответствующему выходу блока формирования синхросигнала, а выходы блока установки режима подключены со ответственно к соответствующим входам демультиплексора, блока форми- 5 рования синхросигнала и к объединенным соответствующим входам блока формирования синхросигнала и блока усреднения, при этом выходы генератора опорной частоты и делителя опор- 0 ной частоты подключены к соответствующим входам блока формирования синхросигнала, соответствующие входы блока усреднения подключены к соответствующим выходам накопительных 5 счетчиков и к соответствующим входам блока установки режима, при этом выход блока формирования синхросигнала является выходом устройства тактовой синхронизации.

S

F

S

cf}uff.2

(и.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1536390A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Устройство для сопряжения двух вычислительных машин | 1979 |

|

SU885988A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1990 |

|

SU1784985A1 |

| Устройство для отладки программ | 1989 |

|

SU1674135A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

Изобретение относится к системам передачи дискретной информации по каналам связи. Цель изобретения увеличение точности синхронизации .. при уменьшении отношения мощности сигнала к мощности шума. Устр-во содержит регенератор 1, демульти- плексор 2,п накопительных,счетчиков 3,- 3f,, г-р 4 опорной частоты, делитель 5 опорной частоты, эл-т ШШ 6, блок 7 установки режима, блок 8 формирования синхросигнала состоящий из блока 9 управляющих сигналов и блока 10 формирована синхросигнала, блок II усреднения, состоящий из контроллера ввода-вывода 12 и микроэвм 13. 9 ил. % (Л

(Ри.г.

36

Л

c

tr

jr

И

;

ITjLb:

/

7

cpuff.5 .

ff7ue 6

Ч

cp(je.7

; 69

72

Lp

f

7

нм

-I/

.S

ixj

73

I-N

-iX

7

:

80

Составитель О.Константинова Редактор Т.Митейко Техред А.Кравчук Корректор А.Обручар

Заказ 7461/59 Тираж 637Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

81

с

%

83

Я1

iT

87

Т

с/&

| Устройство тактовой синхронизации | 1982 |

|

SU1137585A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-01-15—Публикация

1985-03-19—Подача