Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных комплексах.

Известно устройство для сопряжения центральной магистрали с периферийными магистралями, содержащее коммутатор информационных сигналов, узел усилителей управляющих сигналов, элемент НЕ и триггер управления 1.

Недостатком этого устройства являются ограниченные функциональные возможности, связанные с невозможностью обеспечения режима прямого доступа к памяти микроЭВМ и необходимостью подключения к центральной магистрали периферийного

устройства имеющепэмагистрзль. однотипную с центральной.

Наиболее близким к предлагаемому устройству является устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств, содержащее коммутатор информационных сигналов, элемент НЕ, узел усилителей управляющих сигналов, триггер управления, коммутатор управляющих сигналов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер захвата магистрали, причем первая и вторая группы информационный входов - выходов коммутатора информационных сигналов являются соответствующими группами входов-выходов устройства для подключения к информационным шинам магистралей микроЭВМ и периферийных устройств, вход и

х|

00

выход элемента НЕ соединены первым и вторым входами выбора направления коммутатора информационных сигналов, первые и вторые группы входов и выходов узла усилителей управляющих сигналов являют- ся соответствующими группами входов и выходов устройства для подключения к группам входных и выходных шин магистрали микроЭВМ и группам выходных и входных шин магистрали периферийных устройств, выход триггера управления соединен с разрешающими входами коммутатора информационных сигналов и узла усилителей управляющих сигналов, а вход установки, синхровход и информацион- ный вход являются соответствующими входами устройства для подключения к шинам установки и синхронизации обмена магистрали микроЭВМ и входу пуска устройства, первая и вторая группы входов-выходов коммутатора управляющих сигналов являются соответствующими группами входов- выходов устройства для подключения к управляющим шинам магистрали микро- ЭВМ и магистрали периферийных уст- ройств, а первый и второй входы выбора направления подключены соответственно к инверсному и прямому выходам триггера захвата магистрали, информационный вход и синхровыход которого являются со- ответственно входами устройства для под- лючения к шине разрешения запроса магистрали микроЭВМ и шине подтверждения запроса магистрали периферийных устройств, первый вход элемента И СКЛ Ю- ЧАЮЩЕЕ ИЛИ является входом устройства для подключения к шине чтения данных магистрали микроЭВМ, инверсный выход триггера захвата магистрали соединен с вторым входом элемента ИСКЛЮЧАЮ- ЩЕЕ ИЛИ, выходом соединенного с вхо-; дом элемента НЕ 2

Недостатком данного устройства являются ограниченные функциональные возможности из-за того, что k центральной магистрали могут быть подключены только периферийные устройства, имеющие магистраль, однотипную с центральной.

Цель изобретения - расширение функ- циональных возможностей устройства за счет обеспечения возможности подключения к устройству магистрали периферийных устройств, не совпадающей по типу с магистралью микроЭВМ.

Поставленая цель достигается тек что в устройство для сопряжений магистрали микроЭВМ с магистралью периферийных устройств, содержащее коммутатор информационно-адресных сигналов и первый коммутатор управляющих сигналов, первые и вторые группы информационных входов- выходов которых являются соответствующими группами входов-выходов устройства для подключения к магистралям микро- ЭВМ и периферийных устройств, узел усилителей управляющих сигналов, первые группы информационных входов и выходов которого являются соответствующими группами входов и выходов устройства для подключения к магистрали микроЭВМ, а вторые группы его информационных входов и выходов являются соответствующими группами входов и выходов устройства для подключения к магистрали периферийных устройств, триггер управления, информационный вход которого является входом пуска устройства, элемент НЕ, причем прямом выход триггера соединен с входами разрешения первого коммутатора управляющих сигналов, узла усилителей управляющих сигналов и сумматора информационно-адресных сигналов, первый вход выбора направления которого подключен к выходу элемента НЕ, введены второй и третий коммутаторы управляющих сигналов, блок преобразования управ- ляющих сигналов, блок обработки прерывания, элемент И, элемент И-НЕ, элемент ИЛИ, два приемника управляющих сигналов, четыре передатчика управляющих сигналов, причем выходы элементов И- НЕ и ИЛИ соединены соответственно С первым и вторым входами элемента И, выходом подключеного ко второму входу выбора направления коммутатора информационно-адресных сигналов и входу элемента НЕ, группы информационных вхо- дов-выходов второго и третьего коммутаторов управляющих сигналов являются соответствующими группами входов-выходов для подключения к магистрали микро- ЭВМ и периферийных устройств, а группы информационных входов и группы выходов - соответственно с первой и второй группами выходов, второй и первой группами информационных входов блока преобразования управляющих сигналов, первый и второй выходы которого соединены соответственно с информационными входами первого и второго передатчика управляющих сигналов, а входы блокировки и ответа - соответственно с первым и вторым выходами блока обработки прерывания, третий, четвертый выходы которого соединены соответственно с информационными входг- ми третьего и четвертого передатчиков управляющих сигналов, а входы выборки л запроса прерывания блока обработки пре- г)ьшания подключены к выходам первого л

второго приемников управляющих сигналов, входы которых являются соответствующими входами устройства для подключения к магистрали микроЗВМ и магистрали периферийных устройств, выходы первого, второго и третьего передатчиков являются соответствующими выходами устройства для подключения к магистрали микроЭВМ, инверсный выход триггера управления соединен с разрешающими входами третьего и четвертого передатчиков управляющих сигналов, выход последнего является выходом устройства для подключения к магистрали периферийных устройств, разрешающие входы первого и второго передатчиков управляющих сигналов соединены с первой группой выходов узла усилителей управляющих сигналов, первым входом выбора направления первого и входом выбора направления третьего коммутатора управляющих сигналов, разрешающие входы второго и третьего коммутаторов управляющих сигналов соединены с прямым выходом триггера управления, синхровход которого подключен к синхровходу блока обработки прерывания и третьему выходу блока преобразования управляющих сигналов, вход нулевого разряда адреса которого и адресный вход блока обработки прерывания подключены к первой группе информационных входов-выходов коммутатора информационно-адресных сигналов, вход чтения данных блока обработки прерывания соединен с первой группой информационных входов-выходов первого коммутатора управляющих сигналов и первым входом элемента И-НЕ, вторым входрм подключенного к четвертому выходу блока преобразования управляющих сигналов, вход чтения данных которого соединен с первым входом элемента ИЛИ и со второй группой информационных входов-выходов первого коммутатора управляющих сигналов, второй вход выбора направления которого соединен со второй группой выходов узла усилителей управляющих сигналов, входом выбора направления второго коммутатора управляющих сигналов, третьим входом элемента И- НЕ и вторым входом элемента ИЛИ, установочный вход триггера управления соединен со второй группой выходов узла усилителей управляющих сигналов, вход адреса вектора блока обработки прерывания является входом задания адреса вектора прерывания устройства, при этом блок преобразования управляющих сигналов содержит три элемента ИЛИ, три элемента И-НЕ, четыре элемента И, пять

элементов задержки, два элемента НЕ. двз триггера и два элемента ИЛИ-НЕ, первую и вторую группы информационных входов блока, первую и вторую группы выходов 5 блока, вход блокировки блока, входы нулевого разряда адреса, ответа и чтения блока, с первого по четвертый выходы блока, причем выходы первых Элементов ИЛИ и И-НЕ, первый вход .первого элемента

0 ИЛИ соединены соответственно с входом первого элемента задержки и первым входом первого элемента Ииеыход первого элемента НЕ соединен с первым входом второго элемента И-НЕ, выходом подключенного че5 рез второй элемент задержки к первому входу третьего элемента И-НЕ, второй вход которого соединен с инверсным выходом первого триггера, синхровходом подключенного к выходу третьего элемента задержки, пря0 мой и инверсный выходы второго триггера соединены с первыми входами второго и третьего элементов И соответственно, выходы которых подключены к первым входам первого и второго элементов ИЛИ-НЕ

5 соответственно, вторые входы которых подключены к выходу второго элемента НЕ, выход четвертого элемента задержки соединен с первым входом второго элемента ИЛИ, выход которого является пер0 вым выходом блока, выход пятого элемента задержки соединен с первым входом четвертого элемента И, второй вход которого является входом блокировки блока, первый вход и выход третьего

5 элемента ИЛИ и являются соответственно входом ответа и четвертым выходом блока, вход чтения блока соединен со вторым входом второго элемента ИЛИ и является вторым выходом блока, выходы первого

0. элемента И, первого элемента задержки, четвертого элемента И и соответствующий разряд второй группы информационных входов блока образуют вторую группу выходов блока, первый и второй входы пер5 вого элемента И-НЕ, соединенные соответственно с первым и вторым входами первого элемента ИЛИ, второй вход первого элемента И и вход пятого элемента задержки, соединенный с третьим выхо0 дом блока, образуют вторую группу информационных входов блока, вход сброса первого триггера, соединенный с синхровходом второго триггера, входами первого элемента НЕ и третьего элемента

5 задержки, второй вход второго элемента И-НЕ, соединенный с информационным входом первого триггера, с вторыми входами второго и третьего элементов И, выход второго элемента НЕ, соединенный с входом четвертого элемента задержки и второй вход третьего элемента ИЛИ образуют первую группу информационных входов блока, выходы первого элемента ИЛИ-НЕ и второго элемента ИЛИ-ИЕ, выходы третьих элементов И-НЕ и ИЛИ и вход первого элемента НЕ, соединенный с первой группой информационных входов блока, образуют первую группу выходов блока, а блок обработки прерываний содержит вход задания адреса для считывания вектора, дешифратор адреса, триггер, первый и второй элементы И, с первой по третью линии задержки, элемент НЕ, адресный вход, вход выборки, синхровход блока, входы чтения блока и запроса прерывания, с первого по четвертый выходы блока, причем синхровход триггера соединен через первый элемент задерж ки с смнхровходом блока и входом сброса триггера, информационным входом и прямым выходом подключенного соответственно к выходу дешифратора адреса и первому входу первого элемента И, выход которого через второй и третий элементы задержки соединен с четвертым и вторым выходами блока, первый вход второго элемента И соединен через элемент НЕ с выходом первого элемента И, а выход - является третьим выходом блока, вторые входы первого и второго элементов И и инверсный выход триггера являются соответственно входами чтения и запроса прерывания и первым выходом блока.

Сопоставимый анализе прототипом показывает, что заявляемое устройство отличается наличием новых элементов, а именно, двух коммутаторов управляющих сигналов, элемента ИЛИ, элемента И-НЕ, элемента И, элемента НЕ, блока преобразования управляющих сигналов, блока обработки прерываний, четырех магистральных передатчиков управляющих сигналов, двух приемников управляющих сигналов и их связей с другими элементами. Таким образом, заявляемое устройство соответствует критерию изобретения новизна,

Сравнение заявляемого решения с другими техническими решениями показывает, что все указанные элементы широко известны. Однако, при их введении, в указанной связи с другими элементами схемы, в устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств они приводят к расширению функциональных возможностей предлагаемого устройства сопряжения.

Расширение эксплуатационных возможностей получается за счет того, что периферийные устройства, подключаемые к

шине МПИ по ГОСТ26765.51-86 можно подключить к системной магистрали микро- ЭВМ Электроника МС0585.

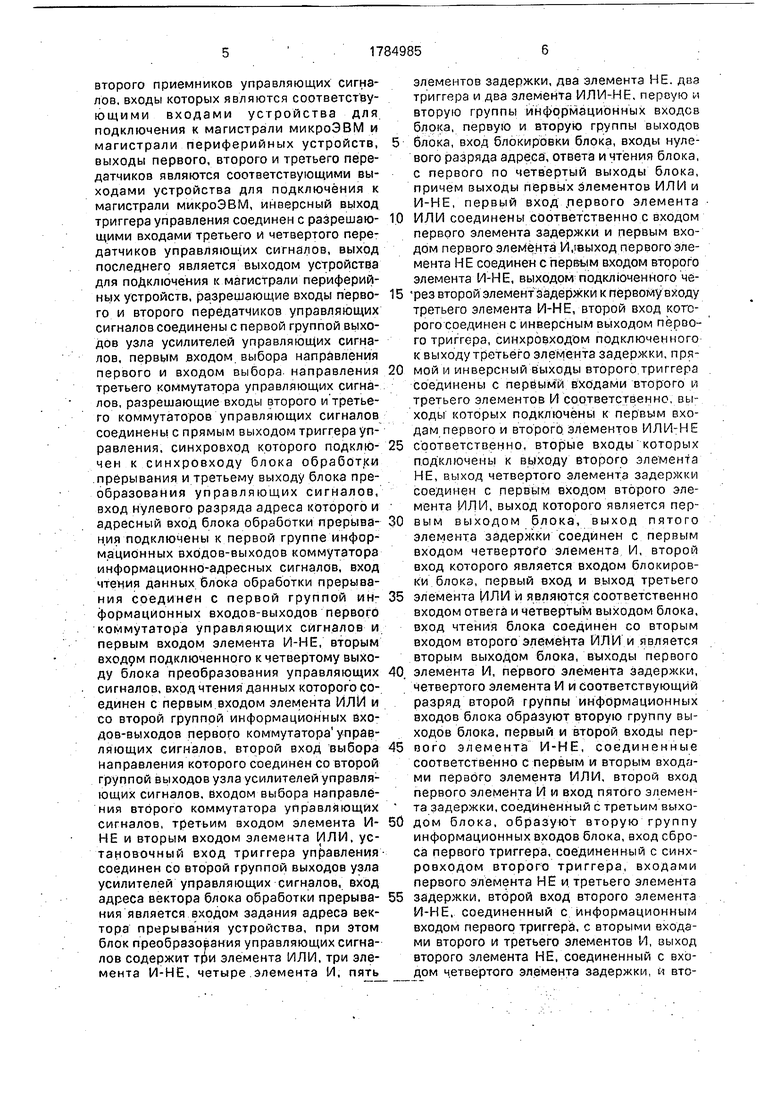

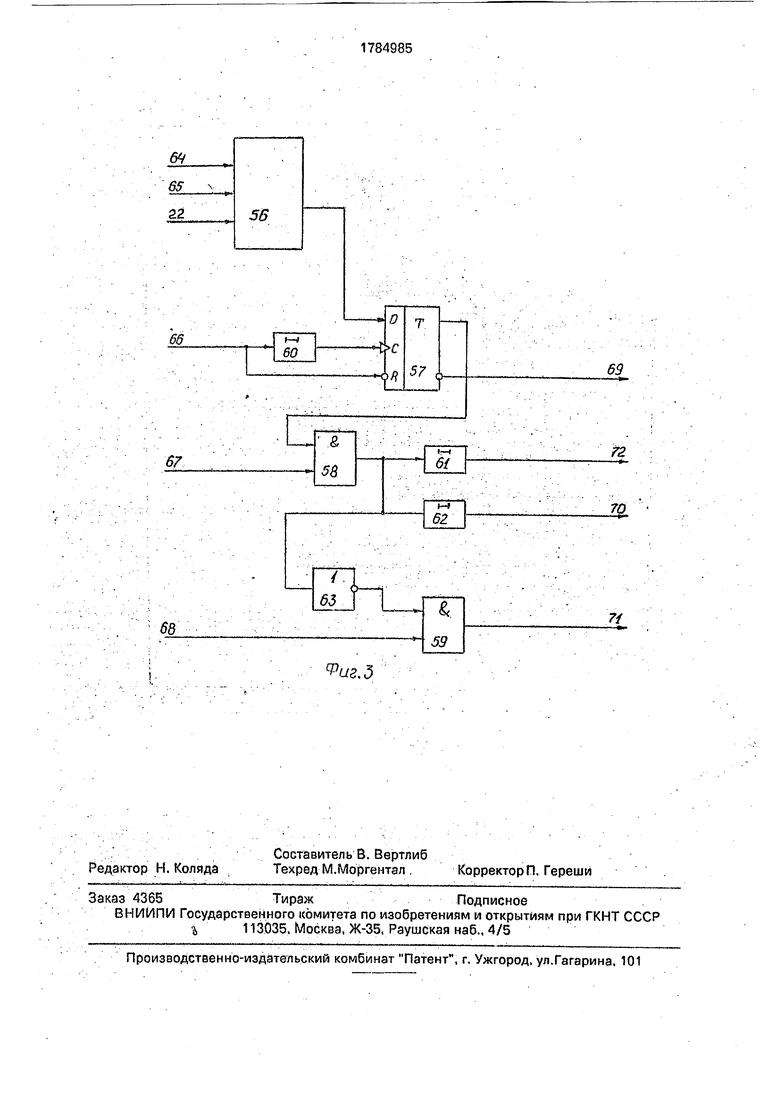

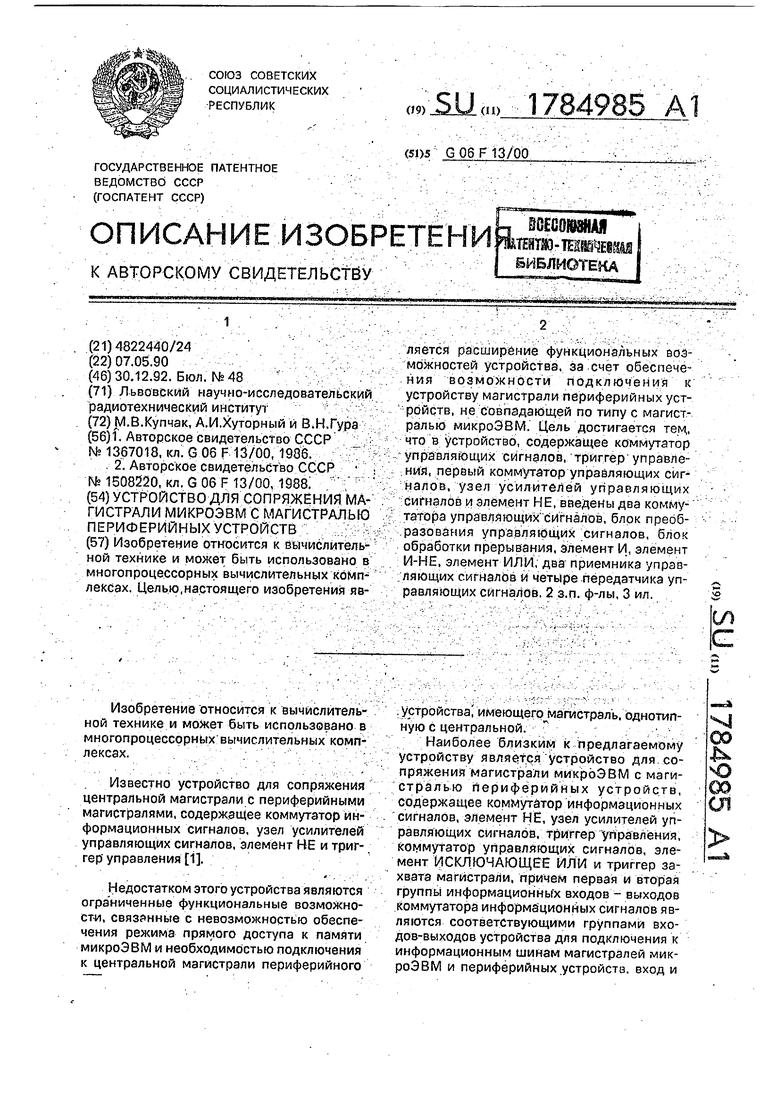

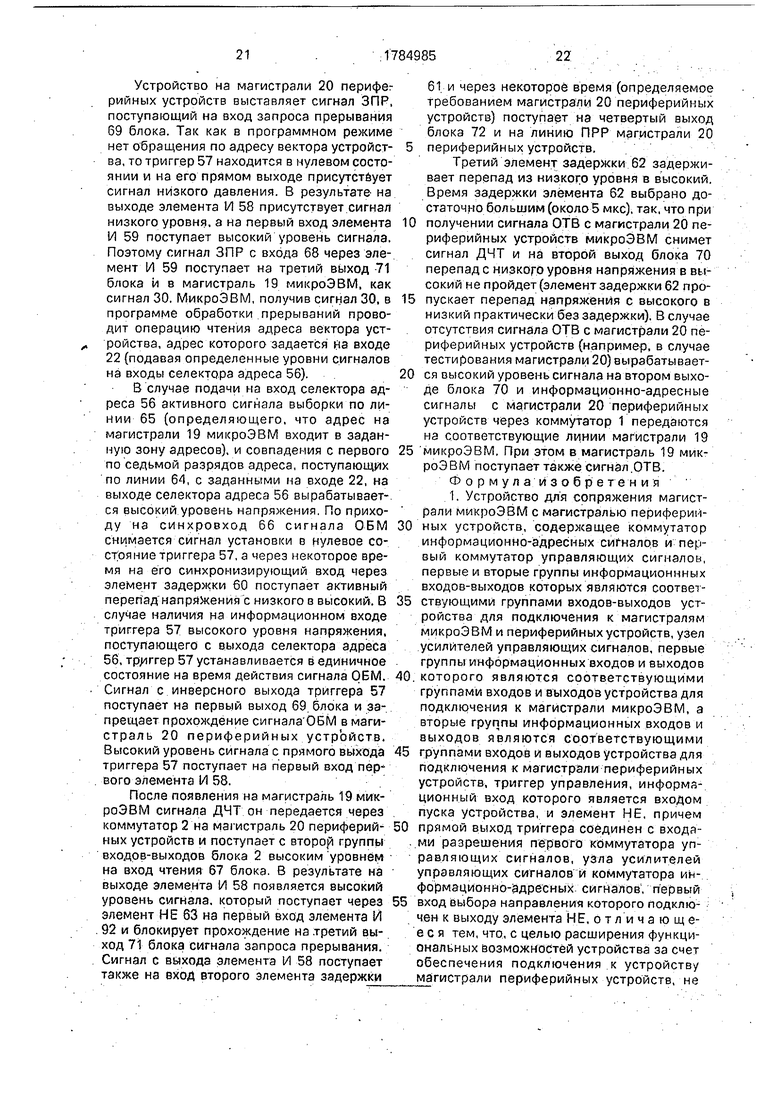

На фиг.1 представлена функциональная схема устройства для сопряжения магистрали микроЭВМ с магистралью периферийных устройств; на фиг.2 - функциональная схема блока преобразования управляющих сигналов; на фиг.З функциональная схема блока обработки прерываний.

Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств содержит (фиг.1) коммутатор 1 информационно-адресных сигналов, первый коммутатор 2 управляющих сигналов, узел 3 усилителей управляющих сигналов, триггер 4 управления, элемент НЕ

5, второй 6 и третий 7 коммутаторы управляющих сигналов, блок преобразования управляющих сигналов 8, блок обработки прерывания 9, элемент И 10, элемент И- НЕ 11, элемент ИЛИ 12, первый 13 и второй 14 приемники управляющих сигналов, первый 15. второй 16, третий 17 и четвертый 18 передатчики управляющих сигналов, магистраль микроЭВМ 19, магистраль периферийных устройств

20, вход пуска устройства 21, вход зада- ния адреса вектора прерывания 22. первые и вторые группы информационных входов-выходов коммутатора 1 информационно-адресных сигналов

являются соответствующими группами входов-выходов устройства для подключения к магистрали 19 микроЭВМ и 20 периферийных устройств, первые и вторые группы информационных входов-аыходов коммутатора 2 управляющих сигналов являются соответствующими группами входов-выходов устройства для подключения, к магистралям 19 микроЭВМ и 20 периферийных устройств и

подсоединяются на магистралях 10 и 20 к линиям Чтение данных (в терминологии интерфейсов микроЭВМ и периферийных устройств - сигнал ДЧТ), и Выбор устройства (ВУ), первые группы информационных входов и выходов узла усилителей управляющих сигналов 3 являются соответствующими группами входов и выходов устройства для подключения к магистрали 19 микроЭВМ и предназначены для передачи в устройство сигналов Разрешение захвата магистрали (РЗМ), Установка (УСТ) и для передачи в магистраль 19 сигналов Запрос магистрали (ЗМ), Подтвежде- ние запроса (ПЗ), Авария источника питания (АИП), вторые группы информационных входов и выходов узла усилителей управляющих сигналов 3 являются соответствующими группами входов и выходов устройства для подключения к магистрали 20 периферийных устройств и предназначены для передачи в устройство сигналов ЗМ, ПЗ, АИП и для передачи в магистраль 20 сигналов РЗМ и УСТ, информационный вход триггера 4 является входом пуска устройства, прямой выход триггера 4 соединен с входами разрешения первого коммутатора 2 управляющих сигналов, узла 3 усилителей управляющих сигналов и коммутатора 1 информационно- адресных сигналов, первый вход выбора направления первого коммутатора 1 информационно-адресных сигналов подключен к выходу элемента НЕ 5, выходы элементов И-НЕ 11 и ИЛИ 12 соединены соответственно с первым и вторым входами элемента И 10, выходом подключенного ко второму входу выбора направления коммутатора 1 информационно-адресных сигналов и входу элемента НЕ 5, группы информационных входов-выходов второго 6 и третьего 7 коммутаторов управляющих сигналов явля ются соответствующими группами входов-выходов для исключения к магистралям 19 мик- роЭВМ и 20 периферийных устройств и подсоединяются на магистрали 19 микро- ЭВМ к линиям Синхронизация обмена (ОБМ), Ответ (ОТВ), Запись младшего байта (ДЗП-МБ), Запись старшего байта (ДЗП-СБ), Адресный цикл вывода или вывод (ВАД), а на магистрали 20 периферийных устройств - к линиям ОБМ, ОТВ, Запись данных (ДЗП), Признак записи (ПЗП), а группы информационых входов и группы выходов - соответственно с первой и второй группами выходов, второй и первой группами информационных входов блока преобразований управляющих сигналов, первый и второй ёыходы которого соединены соответственно с информационными входами первого 15 и второго 16 передатчиков управляющих сигналов, а входы блокировки и ответа - соответственно с первым и вторым выходами блока 9 обработки прерывания, третий, четвертый выходы которого соединены соответственно с информационными входами третьего 17 и четвертого 18 передатчиков управляющих сигналов, а входы выборки и запроса прерывания блока 18 обработки прерывания подключены к выходам первого 13 и второго 14 приемников управляющих сигналов, входы которых являются соответствующими входами устройства для подключения к магистрали 19

микроЭВМ и магистрапи 20 периферийных устройств, выходы первого 15, второго 16 и третьего 17 передатчиков являются соответствующими выходами устройства для 5 подключения к магистрали 19 микроЭВМ, инверсный выход триггера управления 4 соединен с разрешающими входами третьего 17 и четвертого 18 передатчиков управляющих сигналов, последнего

0 является выходом устройства для подключения к магистрали периферийных устройств, разрешающие входы первого 15 и второго 16 передатчиков управляющих сигналов соединены с первой груп5 пой узла усилителей управляющих сигналов 3 и управляющими входами первого 2 и третьего 7 коммутаторов управляющих сигналов, разрещающие входы второго 6 и третьего 7 коммутаторов

0 управляющих сигналов соединены с прямым выходом триггера управления 4, синхровход которого подключен к синх- ровходу блока обработки прерывания 9 и третьему выходу блока преобразования

5 управляющих сигналов 8, вход нулевого разряда адреса которого и адресный вход блока обработки прерывания подключены к первой группе информационных входов-выходов коммутатора 1 информа0 ционно-адресных сигналов, вход чтения данных блока обработки прерывания 9 соединен с первой группой информационных входов-выходов4 первого коммутатора 2 управляющих сигналов и первым входом

5 элемента И-НЕ 11, вторым входом подключенного к четвертому выходу блока преобразования управляющих сигналов 8, вход чтения данных которого соединен с первым входом элемента ИЛИ 12 и со

0. второй группой информационных входов-выходов первого коммутатора 2 управляющих сигналов, вход выбора направления которого соединен со второй группой выходов узла усилителей уп5 равляющих сигналов 3, третьим входом элемента И-ИЕ 11 и вторым входом элемента ИЛИ 12, установочный вход триггера управления 4 соединен со второй группой выходов узла усилителей управля0 ющих сигналов 3, вход адреса вектора блока обработки прерывания 9 является входом задания адреса вектора прерывания устройства.

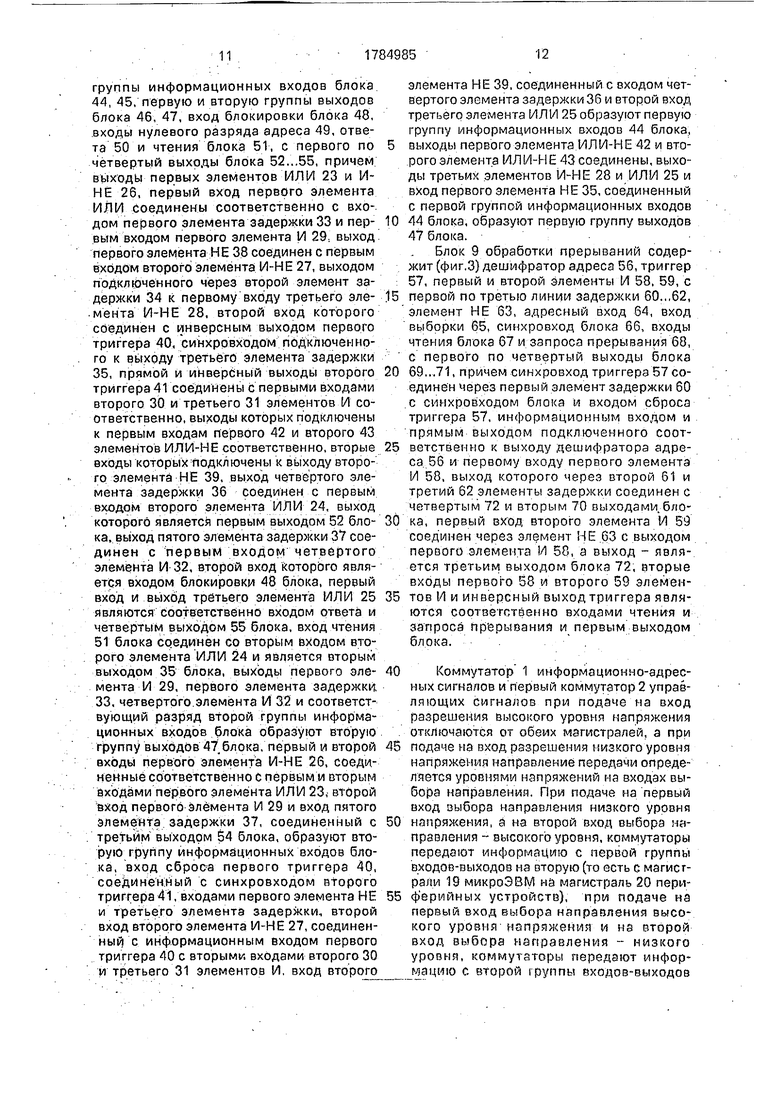

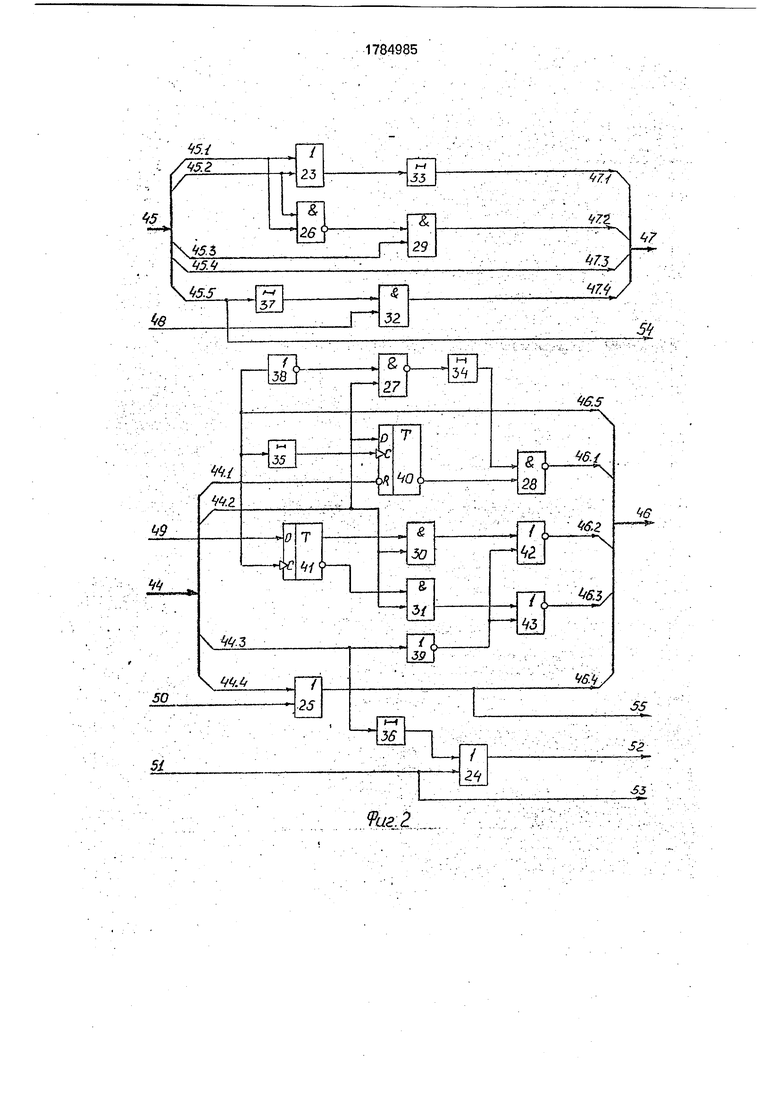

Блок преобразования управляющих

5 сигналов содержит (фиг.2) три элемента ИЛИ 23, 24, 25, три элемента И-НЕ 26...28, четыре элемента И 29, 30, 31, 32, пять элементов задержки 33.,.35, 36,37, два элемента НЕ 38, 39, два триггера 40, 41 и два цемента ИЛ И-НЕ 42 и 43, первую и вторую

группы информационных входов блока 44, 45, первую и вторую группы выходов блока 46, 47, вход блокировки блока 48, входы нулевого разряда адреса 49, ответа 50 и чтения блока 51, с первого по четвертый выходы блока 52...55, причем выходы первых элементов ИЛИ 23 и И- НЕ 26, первый вход первого элемента ИЛИ соединены соответственно с входом первого элемента задержки 33 и первым входом первого элемента И 29 выход первого элемента НЕ 38 соединен с первым входом второго элемента И-НЕ 27, выходом подключенного через второй элемент задержки 34 к первому входу третьего элемента И-НЕ 28, второй вход которого соединен с инверсным выходом первого триггера 40, синхровходом подключенного к выходу третьего элемента задержки 35, прямой и инверсный выходы второго триггера 41 соединены с первыми входами второго 30 и третьего 31 элементов И соответственно, выходы которых подключены к первым входам первого 42 и второго 43 элементов 1ЛЛИ-НЕ соответственно, вторые входы которых подключены к выходу второго элемента НЕ 39, выход четвертого элемента задержки 36 соединен с первым входом второго элемента ИЛИ 24, выход которого является первым выходом 52 блока, выход пятого элемента задержки 37 соединен с первым входом четвертого элемента И 32, второй вход которого является входом блокировки 48 блока, первый вход и выход третьего элемента ИЛИ 25 являются соответственно входом ответа и четвертым выходом 55 блока, вход чтения 51 блока соединен со вторым входом второго элемента ИЛИ 24 и является вторым выходом 35 блока, выходы первого элемента И 29, первого элемента задержки, 33. четвертого элемента И 32 и соответствующий разряд второй группы информационных входов блока образуют вторую группу выходов 47. блока, первый и второй входы первого элемента И-НЕ 26, соединенные соответственно с первым и вторим входами первого элемента ИЛИ 23, второй вход первого элемента И 29 и вход пятого элемента задержки 37, соединенный с третьим выходом 54 блока, образуют вторую группу информационных входов блока, вход сброса первого триггера 40, соединенный с синхровходом второго триггера 41, входами первого элемента HF и третьего элемента задержки., второй вход второго элемента И-НЕ 27, соединенный с информационным входом первого триггера 40 с вторыми входами второго 30 и третьего 31 элементов И, вход второго

элемента НЕ 39, соединенный с входом четвертого элемента задержки 36 и второй вход третьего элемен га ИЛИ 25 образуют первую группу информационных входов 44 блока,

выходы первого элемента И Л И-НЕ 42 и второго элемента ИЛ И-НЕ 43 соединены, выходы третьих элементов И-НЕ 28 и ИЛИ 25 и вход первого элемента НЕ 35, соединенный с первой группой информационных входов

44 блока, образуют первую группу выходов 47 блока.

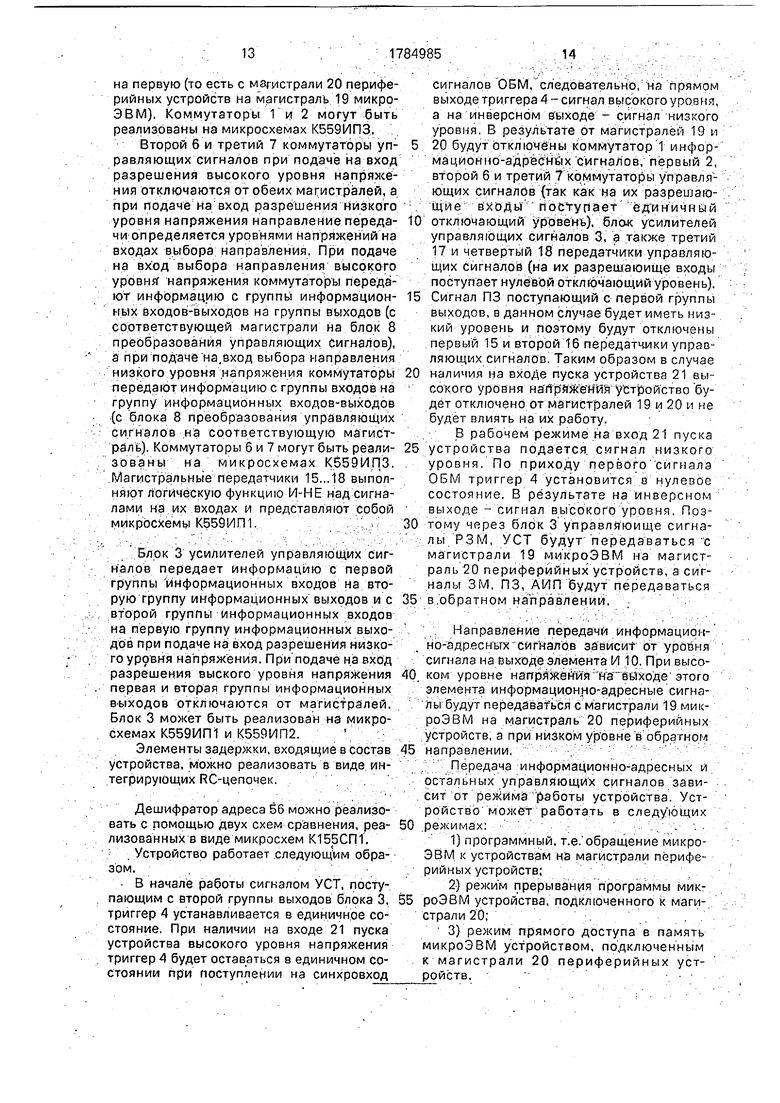

Блок 9 обработки прерываний содержит (фиг.З) дешифратор адреса 56, триггер 57, первый и второй элементы И 58, 59, с

первой по третью линии задержки 60.,,62, элемент НЕ 63, адресный вход 64, вход выборки 65, синхровход блока 66, входы чтения блока 67 и запроса прерывания 68, с первого по четвертый выходы блока

69...71, причем синхровход триггера 57 соединен через первый элемент задержки 60 с синхровходом блока и входом сброса триггера 57, информационным входом и прямым выходом подключенного соотвстственно к выходу дешифратора адреса 56 и первому входу первого элемента И 58, выход которого через второй 61 и третий 62 элементы задержки соединен с четвертым 72 и вторым 70 выходами, блока, первый вход второго элемента И 59 соединен через элемент НЕ 63 с выходом первого элемента И 58, а выход - является третьим выходом блока 72, вторые входы первого 58 и второго 59 элемеитов И и инверсный выход триггера являются соответственно входами чтения и запроса прерывания и первым выходом блока.

Коммутатор 1 информационно-адресных сигналов и первый коммутатор 2 управ- ляющих сигналов при подаче на вход разрешения высокого уровня напряжения отключаются от обеих магистралей, а при

подаче на вход разрешения низкого уровня напряжения направление передачи определяется уровнями напряжений на входах выбора направления. При подаче на первый вход выбора направления низкого уровня

напряжения, а на второй вход выбора направления - высокого уровня, коммутаторы передают информацию с первой группы входав-выходоо нз вторую (то ость с магистрали 19 микроЭВМ на магистраль 20 периферийных устройств), при подаче на первый вход выбора направления высокого уровня напряжения м на пторой вход выбора направления - низкого уровня, коммутаторы передают инфорвдацмю с второй (руппы входов-выходов

на первую (то есть с магистрали 20 периферийных устройств на магистраль 19 микро- ЭВМ). Коммутаторы 1 и 2 могут быть реализованы на микросхемах К559ЙПЗ.

Второй 6 и третий 7 коммутаторы управляющих сигналов при подаче на вход разрешения высокого уровня напряжения отключаются от обеих магистралей, а при подаче на вход разрешения низкого уровня напряжения направление передачи определяется уровнями напряжений на входах выбора направления. При подаче на вход выбора направления высокого уровня напряжения коммутаторы передают информацию с группы информационных входов-выходов на группы выходов (с соответствующей магистрали на блок 8 преобразования управляющих сигналов), а при подаче на.вход выбора направления низкого уровня напряжения коммутаторы передают информацию с группы входов на группу информационных входов-выходов (с блока 8 преобразования управляющих сигналов на соответствующую магистраль). Коммутаторы 6 и 7 могут быть реали- зованы на микросхемах К559ИЛЗ. Магистральные передатчики 15...18 выполняют логическую функцию И-НЕ над сигналами на их входах и представляют собой микросхемы К559ИП1.

Блок 3 усилителей управляющих сигналов передает информацию с первой группы информационных входов на вторую группу информационных выходов и с второй группы информационных входов на первую группу информационных выходов при подаче на вход разрешения низкого уррвня напряжения. При подаче на вход разрешения выского уровня напряжения первая и вторая группы информационных в-ыходов отключаются от магистралей. Блок 3 может быть реализован на микросхемах К559ИП1 и К559ИП2.

Элементы задержки, входящие в состав устройства, можно реализовать в виде интегрирующих RC-цепочек.

Дешифратор адреса 56 можно реализовать с помощью двух схем сравнения, реализованных в виде микросхем К155СП1,

Устройство работает следующим образом.

В начале работы сигналом УСТ, поступающим с второй группы выходов блока 3, триггер 4 устанавливается в единичное состояние. При наличии на входе 21 пуска устройства высокого уровня напряжения триггер 4 будет оставаться в единичном состоянии при поступлении на синхровход

сигналов ОБМ, следовательно, на прямом выходе триггера 4 - сигнал высокого уровня, а на инверсном выходе - сигнал низкого уровня, В результате от магистралей 19 и 5 20 будут отключены коммутатор 1 информационно-адресных сигналов, первый 2, второй 6 и третий 7 коммутаторы управляющих сигналов (так как на их разрешающие входы поступает единичный

10 отключающий уровень), блох усилителей управляющих сигналов 3, а также третий 17 и четвертый 18 передатчики управляющих сигналов (на их разрешаюище входы поступает нулевой отключающий уровень).

5 Сигнал ПЗ поступающий с первой группы выходов, в данном случае будет иметь низкий уровень и поэтому будут отключены первый 15 и второй 16 передатчики управляющих сигналов. Таким образом в случае

0 наличия на входе пуска устройства 21 высокого уровня на Пр йж е Нй я устройство будет отключено от магистралей 19 и 20 и не будет влиять на их работу.

В рабочем режиме на вход 2 i пуска

5 устройства подается сигнал низкого уровня. По приходу первого сигнала ОБМ триггер 4 установится в нулевое состояние. В результате на инверсном выходе - сигнал высокого уровня. Поэ0 тому через блок 3 управляюище сигналы РЗМ, УСТ будут передаваться с магистрали 19 микроЭВМ на магистраль 20 периферийных устройств, а сигналы ЗМ, ПЗ, АИП будут передаваться

5 в обратном направлении.

Направление передачи информационно-адресных сигналов зависит от уровня сигнала на выходе элемента И 10. При вьгсо0. ком уровне напряжения на §ь1ходе этого элемента информационно-адресные сигналы будут передаваться с магистрали 19 микроЭВМ на магистраль 20 периферийных устройств, а при низком уровне в обратном

5 направлении,

Передача информационно-адресных и остальных управляющих сигналов зависит от режима работы устройства. Устройство может работать в следующих

0 режимах:

1)программный, т.е. обращение микро- ЭВМ к устройствам на магистрали периферийных устройств;

2)режим прерывания программы мик- 5 роЭВМ устройства, подключенного к магистрали 20;

3)режим прямого доступа в память микроЭВМ устройством, подключенным к магистрали 20 периферийных устройств.

Рассмотрим передачу сигналов устройством сопряжения в каждом из этих режимов.

В программном режиме работы и режиме прерывания сигнал ПЗ находится в пассивном состоянии, поэтому на первый вход выбора направления первого коммутатора управляющих сигналов 2, на вход выбора направления второго коммутатора управляющих сигналов 7 и на разрешающие входы первого 15 и второго 16 передатчиков поступает низкий уровень напряжения с первой группы выходов блока усилителей и управляющих сигналов 3, а на второй вход выбора направления первого коммутатора управляющих сигналов 2, на вход выбора направления первого коммутатора управляющих сигналов 6 поступает высокий уровень напряжения с второй группы выходов блока усилителей управляющих сигналов 3. При этом первый 2 коммутатор управляющих сигналов передает сигналы АЧТ и ВУ с магистрали 19 микроЭВМ на магистраль 20 периферийных устройств, второй 6 коммутатор управляющих сигналов передает сигналы ОБМ, ДЗП, МБ, ДЗП СБ, ВАД с магистрали 19 микроЭВМ в блок 8 преобразования управляющих сигналов, а сигнал ОТВ в обратном направлении, третий коммутатор 7 управляющих сигналов передает сигналы ОБМ, ДЗП, ПЗП с блока 8 преобразования управляющих сигналов на магистраль 20 периферийных устройств, а сигнал ОТВ в обратном направлении. В указанных двух режимах работы сигналы Адресный цикл вывода или вывод (АЦВ), Данные (Д) с выходов первого 15 и второго 16 передатчиков управляющих сигналов в магистраль 19 микроЭВМ не поступают.

В программном режиме и режиме прерывания блок 8 преобразования управляющих сигналов передает сигнал ОБМ с второго коммутатора 6 управляющих сигналов на третий коммутатор 7 управляющих сигналов, а сигнал ОТВ с обратном направ-- лении. а также преобразует сигналы ДЗП МБ, ДЗП СБ, ВАД, поступающие из второго коммутатора 6 управляющих сигналов, в сигналы ДЗП, ПЗП и передает их на третий коммутатор 7 управляющих сигналов.

Направление передачи информационно-адресных сигналов зависит от уровня на- пряжения на выходе элемента И 10. В вышеуказанных двух режимах на втором входе элемента И 10 будет присутствовать высокий уровень напряжения с выхода элемента ИЛИ 12, так как на второй вход последнего поступает высокий уровень напряжения с второй группы выходов блока усилителей управляющих сигналов 3. При

этом уровень сигнала на выходе элемента И 16 будет повторять уровень сигнала на выходе элемента И-НЕ 11, который, в свою очередь,будет зависеть от уровней сигналов

ДЧТ на первой магистрали 19 микроЭВМ и сигнала ОТВ, поступающего из устройства сопряжения в магистраль 19 микроЭВМ, т.е. блок 1 в программном режиме и режиме прерывания будет передавать иифор0 мационно-адресные сигналы с магистрали 20 периферийных устройств в магистраль 19 микроЭВМ в цикле чтения со стороны микроЭВМ регистров устройств на магистрали 20 или чтения адреса вектора устройства. В

5 остальных случаях (адресные циклы или циклы записи) информационно-адресные сигналы будут передаваться из магистрали 19 микроЭВМ в магистраль 20 периферийных устройств,

0 В режиме прерывания устройство работает следующим образом.

Сигнал Запрос прерывания (ЗПР) на магистрали 20 периферийных устройств передается в магистраль 6 микроЭВМ на ли5 нию Запрос обмена (30). В результате микроЭВМ выходит на обработку прерывания. Блок 9 обработки прерывания преобразует цикл чтения регистра устройства сопряжения на магистрали 19 микроЭВМ в

0 цикл считывания вектора прерывания на магистрали 20 периферийных устройств. При этом блокируется прохождение в магистраль 20 периферийных устройств сигнала ОБМ, пропускается в магистраль 20 перифе5 рийных устройств сигнал ДСТ и через определенное время блок 9 вырабатывает сигнал Разрешение прерывания (ПРР), поступающий в магистраль 20 периферийных устройств, Устройство, выставившее запрос и

0 получившее сигналы ДЧТ и ПРР, выставляет свой прерывания и сигнал ОТВ, который передается в магистраль 19 микроЭВМ. Таким образом, при обращении по адресу вектора устройства микроЭВМ считывает

5 вектор прерывания.

В устройстве сопряжения при чтении вектора устройства предусмотрена выработка сигнала ОТВ в случае отсутствия сигнала ОТВ с магистрали 20 периферийных

0 устройств (при этом микроЭВМ считывает состояние информационно-адресных линий магистрали 20 периферийных устройств). Этот режим можно использовать в целях отладки устройств на магистрали 20 пери5 ферийных устройств.

В режиме прямого доступа устройство - инициатор обмена в данном режиме выставляет сигнал ЭМ, который передается в магистраль 19 микроЭВМ. МикроЭВМ вырабатывает ответный сигнал РЗМ, а устройство выставляет сигнал ПЗ и снимает сигнал ЭМ, в результате чего микроЭВМ снимает сигнал РЗМ и передает управление магистралью 19 устройству. Устройство начинает операции обмена на магистрали.

Рассмотрим работу устройства в этом режиме. Сигнал ПЗ находится в активном состоянии, поэтому на первый вход выбора направления первого коммутатора управляющих сигналов 2, на вход выбора направления второго коммутатора управляющих сигналов 7 и на разрешающие входы первого 15 и второго 16 передатчиков поступает высокий уровень напряжения с первой группы выходов блока усилителей управляющих сигналов, 3 а на второй вход выбора направления первого коммутатора управляющих сигналов 2, на вход выбора направления первого коммутатора управляющих сигналов 6 передатчика поступает уровень напряжения с второй группы выходов блока усилителей 3. При этом первый коммутатор 2 управляющих сигналов передает сигналы ДЧТ и ВУ с магистрали 20 периферийных устройств на магистраль 19 микроЭВМ. Третий коммутатор 7 управляющих сигналов передает сигналы ОБМ, ДЗП, ПЗП с магистрали 20 периферийных устройств в блок 8 преобразования управляющих сигналов, а сигнал ОТВ в обратном направлении. Второй коммутатор 6 управляющих сигналов передает сигналы ОБМ, ДЗП МБ, ДЗП СБ, ВАД с блока 8 преобразования управляющих сигналов в магистраль 19 микроЭВМ. а сигнал ОТВ в обратном направлении. Первый 15 и второй 16 передатчики передают сигналы Д и АЦВ, выработанные блоком 8 в магистраль 19 микроЭВМ.

Направление передачи информационно-адресных сигналов зависит от уровня напряжения на выходе элемента И 10. В рассматриваемом режиме, так как сигнал ПЗ - активный, то на второй вход элемента I/I 10 поступает сигнал высокого уровня с второй группы выходов узла усилителей управляющих сигналов 3 и уровень сигнала на выходе элемента И 10 будет повторять уровень сигнала ДЧТ со стороны магистрали 20 периферийных устройств. Таким образом, в циклах чтения первый коммутатор 1 передает информационно-адресные сигналы с магистрали 19 микроЭВМ в магистраль 20 периферийных устройств, а в остальных случаях (адресных циклах, циклах записи) -информационно-адресные сигналы будут передаваться с магистрали 20 периферийных устройств в магистраль 19 микроЭВМ.

Блок 8 преобразования управляющих сигналов работает следующим образом.

В программном режиме работы и режиме прерывания используются все сигналы с второй группы информационных входов блока 45 кроме сигнала ОТВ, поступающего 5 по линии 45.4, а также используется сигнал ОТВ со входа 45.4. Остальные сигналы хоть и обрабатываются блоком, не передаются коммутаторами 6 и 7 управляющих сигналов на магистрали. Рассмотрим преобразова0 ние используемых сигналов.

Сигнал ОБМ поступает с второй группы информационных входов блока 45 по линии 45.1 на пятый элемент задержки 37, задерживается им и проходит на первый вход

5 четвертого элемента И 32, на второй вход которого поступает сигнал с входа блокировки блока 48. Этот сигнал вырабатывается в блоке 9 обработки прерываний и имеет высокий уровень все время, кроме случая

0 обраи ния к адресу вектора прерывания устройства для организации процедуры считывания вектора прерывания. Время задержки пятого элемента задержки 37 выбрано большим времени срабатывания схемы вы5 борки адреса вектора. Таким образом, сигнал ОБМ передается с второй группы информационных входов блока 45 на вторую группу информационных выходов блока 47 по линии 47.4 во всех случаях, кроме

0 операции считывания вектора прерывания с магистрали 20 периферийных устройств.

Кроме того, блок преобразования управляющих сигналов вырабатывает сигналы ДЗП и ПЗП. Сигнал ДЗП вырабатывается на

5 выходе первого элемента задержки 33 и устанавливается в активное состояние (высокий уровень) через время, определяемое временем задержки элемента задержки 33 после появления на входах первого элемен0 та ИЛИ 23 одного из сигналов ДЗП МБ по линии 45.1 или ДЗП СБ по линии 45., Элемент задержки 33 предназначен для того, чтобы сигнал ПЗП в случае записи слова отсутствовал перед появлением сигнала

5 ДЗП и чтобы устройство ошибочно не приняло операцию записи слова за операцию записи байта.

Сигнал ПЗП вырабатывается при наличии на линии 45.3 высокого (активного)урое0 ня сигнала ВАД и пассивном (низком) уровне хотя бы одного из сигналов ДЗП МБ или ДЗП СБ на входах первого элемента И-НЕ 26.

Сигнал ОТВ появляется на выходе

5 третьего элемента И-НЕ 25, если по линии 44.4 поступает сигнал ответа высокого уровня с магистрали 20 периферийных устройств или сигнала ответа с блока 9, поступающий со входа ответа 50 на первый вход третьего элемента ИЛИ 25.

В режиме прямого доступа в память используются все сигналы с первой группы информационных входов 44, кроме сигнала ОТВ, поступающего по линии 44.4, а такмсе используется сигнал ОТВ, поступающий по пинии 45 4. Остальные сигналы хоть и обрабатываются блоком, но не передаются коммутаторами б и 7 управляющих сигналов на магистрали 19 и 20. Поэтому рассмотрим передачу используемых сигналов.

Сигнал ОТВ поступает со второй группы информационных входов блока 45 по линии 45 4 на вторую группу выходов блока 47 по линии 47.3, а сигнал ОБМ передается с первой группы информационных входов блока 45 по линии 45.4 на вторую группу выходов блока 47 по линии 47.3, а сигнал ОБМ передается с первой группы информационных входов 44 по линии 44.1 на первую группу выходов 46 по линии 46.5.

Сигнал ВАД вырабатывается в результате обработки сигналов ОБМ и ПЗП, поступающих с первой группы информационных входов блока 44 по линиям 44.1 и 44.2 соответственно При низких уровнях этих сигналов на выходе третьего элемента И-НЕ 28 присутствует сигнал высокого уровня, т.к. на его обоих входах высокий уровень (триггер 40 находится в нулевом состоянии, а на выходах второго элемента И-НЁ 27 и второго элемента задержки 34 - высокий уровень).

Рассмотрим формирование сигнала ВАД во время операции записи.

При появлении на линии 44.2 высокого уровня сигнала, на выходе элемента И-НЕ 27 появляется низкий уровень сигнала, который через элемент задержки 34 (перепад напряжения из высокого уровня в низкий проходит через элемент 34 практически без задержки) поступает на первый бход эле мента И-НЕ 28. На линии 46.1 появляется высокий уровень напряжения. Таким образом, в адресном цикле операции записи сигнал ВАД на линии 46.1 имеет высокий уровень.

При появлении на линии 44.1 высокого уровня сигнала ОБМ снимается низкий уровень на установочном входе триггера 72, а на его синхровходе через некоторое время, определяемое элементом задержки 70, появляется перепад напряжения и при высоком уровне на линии 44,2 триггер 41 устанавливается в единичное состояние на время действия сигнала ОБМ и таким образом поддерживается высокий уровень на выходе элемента И-НЁ 28 независимо от уровня сигнала ПЗП на линии 44.2.

Одновременно сигнал ОБМ инвертируется элементом НЕ 38 и вызывает появление на выходе элемента И-НЕ 27 высокого уровня, который задерживается элементом задержки 34 (его время задержки превышает вр-емя задержки элемента 35 и установки

триггера 40) и не влияет на состояние уровня сигнала ПЗП на линии 46.1.

В адресном цикле операции чтения на линии 44.2 присутствует низкий уровень напряжения, триггер 40 при этом под действи0 ем сигнала на линии 44.1 в единичное состоянии не устанавливается и сигнал ВАД на линии 46.1 имеет низкий уровень (пассивное состояние) независимо от изменения уровня сигнала ПЗП на линии 44.2 во время

5 действия сигнала ОБМ на линии 44.1 (для магистрали 20 периферийных устройств уровень сигнала ПЗП в цикле передачи данных операции чтения может иметь любое Значение).

0 Сигналы ДЗП МБ и ДЗП СБ вырабатываются на линиях 46.2 и 46.3 следующим образом.

В адресном цикле каждой операции обмена триггер 41 устанавливается в единич5 ное или нулевое состояние в зависимости or уровня напряжения на линии 49 нулевого разряда адреса. Если в цикле передачи данных сигнал на линии 44.2 ПЗП будет иметь низкий уровень (т е. происходит запись сло0 ва информации), то на выходах элементов И 30 и 31 будет низкий уровень сигнала, независимо от состояния триггера 41.

При наличии в цикле передачи данных на линии 44.2 сигнала ПЗП высокого уровня

5 напряжения на одном из элементов И 30 или 31 (в зависимости от состояния триггера 41) будет присутствовать высокий, а на другом - низкий уровень напряжения. Выходные сигналы элементов И 30 и 31

0 стробируются сигналом ДЗП, поступающим по линии 44,3, и инвертируются элементами ИЛИ-НЕ 42 и 43, выходные сигналы которых поступают иа линии 46.2 и 46.3 соответственно.

5

Блок 8 преобразования управляющих сигналов в режиме прямого доступа в память вырабатывает сигналы Д и АЦВ, поступающие на первый 52 и второй 53 выходы

0 блока 17 Сигнал АЦВ повторяет сигнал ДЧТ, поступающий с входа чтения 51 блока. Активный (высокий) уровень сигнала Д вырабатывается при активном (высоком) уровне одного из сигналов ДЧТ или ДЗП, причем

5 выходной сигнал повторяет сигнал ДЧТ и задержан на определенное время (определяемое интерфейсом микроЭВМ) относительно сигнала ДЗП

Блок 9 обработки прерывания работает следующим образом

Устройство на магистрали 20 периферийных устройств выставляет сигнал ЗПР, поступающий на вход запроса прерывания 69 блока. Так как в программном режиме нет обращения по адресу вектора устройства, то триггер 57 находится в нулевом состоянии и на его прямом выходе присутствует сигнал низкого давления. В результате на выходе элемента 1/1 58 присутствует сигнал низкого уровня, а на первый вход элемента И 59 поступает высокий уровень сигнала. Поэтому сигнал ЗПР с входа 68 через элемент И 59 поступает на третий выход 71 блока и в магистраль 19 микроЭВМ, как сигнал 30. МикроЭВМ, получив сигнал 30, в программе обработки прерываний проводит операцию чтения адреса вектора уст- ройства, адрес которого задается на входе 22 {подавая определенные уровни сигналов на входы селектора адреса 56).

В случае подачи на вход селектора адреса 56 активного сигнала выборки по линии 65 (определяющего, что адрес на магистрали 19 микроЭВМ входит в заданную зону адресов), и совпадения с первого по седьмой разрядов адреса, поступающих по линии 64, с заданными на входе 22, на выходе селектора адреса 56 вырабатывается высокий уровень напряжения По приходу на синхровход 66 сигнала ОБМ снимается сигнал установки в нулевое состояние триггера 57, а через некоторое время на его синхронизирующий вход через элемент задержки 60 поступает активный перепад напряжения с низкого в высокий. В случае наличия на информационном входе триггера 57 высокого уровня напряжения, поступающего с выхода селектора адреса 56, триггер 57 устанавливается в единичное состояние на время действия сигнала ОБМ. Сигнал с инверсного выхода триггера 57 поступает на первый выход 69 блока и запрещает прохождение сигнала ОБМ в маги- страль 20 периферийных устройств. Высокий уровень сигнала с прямого выхода триггера 57 поступает на первый вход первого элемента И 58.

После появления на магистраль 19 микроЭВМ сигнала ДЧТ он передается через коммутатор 2 на мажстраль 20 периферийных устройств и поступает с второй группы входов-выходов блока 2 высоким уровнем на вход чтения 67 блока В результате на выходе элемента И 58 появляется высокий уровень сигнала, который поступает через элемент НЕ 63 на первый вход элемента И 92 и блокирует прохождение на третий выход 71 блока сигнала запроса прерывания. Сигнал с выхода элемента И 58 поступает также на вход второго элемента задержки

61 и через некоторое время (определяемое требованием магистрали 20 периферийных устройств) поступает на четвертый выход блока 72 и на линию ПРР магистрали 20 5 периферийных устройств.

Третий элемент задержки 62 задерживает перепад из низкого уровня в высокий. Время задержки элемента 62 выбрано достаточно большим (около 5 мкс), так, что при

0 получении сигнала ОТВ с магистрали 20 периферийных устройств микроЭВМ снимет сигнал ДЧТ и на второй выход блока 70 перепад с низкого уровня напряжения в высокий не пройдет (элемент задержки 62 про5 пускает перепад напряжения с высокого в низкий практически без задержки), В случае отсутствия сигнала ОТВ с магистрали 20 периферийных устройств (например, в случае тестирования магистрали 20) вырзбатывает0 ся высокий уровень сигнала на втором выходе блока 70 и информационно-адресные сигналы с магистрали 20 периферийных устройств через коммутатор 1 передаются на соответствующие линии магистрали 19

5 микроЭВМ, При этом в магистраль 19 микроЭВМ поступает также сигнал ОТВ. Формула изобретения 1. Устройство для сопряжения магистрали микроЭВМ с магистралью периферии0 ных устройств, содержащее коммутатор информационно-адресных сигналов и первый коммутатор управляющих сигналов, первые и вторые группы информационнных входов-выходов которых являются соответ

5 ствующими группами входов-выходов устройства для подключения к магистралям микроЭВМ и периферийных устройств, узел усилителей управляющих сигналов, первые группы информационных входов и выходов

0 которого являются соответствующими группами входов и выходов устройства для подключения к магистрали микроЭВМ, а вторые группы информационных входов и выходов являются соответствующими

5 группами входов и выходов устройства для подключения к магистрали периферийных устройств, триггер управления, информационный вход которого является входом пуска устройства, и элемент НЕ, причем

0 прямой выход триггера соединен с входами разрешения первого коммутатора управляющих сигналов, узла усилителей управляющих сигналов и коммутатора информационно-адресных сигналов, первый

5 вход выбора направления которого подключен к выходу элемента НЕ, о т л и ч а ю щ е- е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения подключения к устройству магистрали периферийных устройств, не

совпадающей по типу с магистралью микро- ЭВМ, в него введены второй и третий коммутаторы управляющих сигналов, блок преобразования управляющих сигналов, блок обработки прерывания, элемент И, элемент И-НЕ, элемент ИЛИ, два приемника управляющих сигналов, четыре передатчика управляющих ,сигналов, причем выходы элементов И-НЕ и ИЛИ соединены соответственно с первым и вторым входами элемента И, выходом подключенного к второму входу выбора направления коммутатора информационно-адресных сигналов м входу элемента НЕ, группы информационных входов-выходов второго и третьего коммутаторов управляющих сигналов являются соответственно группами вхоДо вШйдов устройства для подключения к магистралям микроЭВМ и периферийных устройств, а группы информационных входов и группы выходов соединены соответственно с первой и второй группами выходов, второй и первой группами информационных входов блока преобразования управляющих сигналов, первый и второй выходы которого соединены соответственно с информационными входами первого и второго передатчи- ков управляющих сигналов, а входы блокировки и ответа - соответственно с первым и вторым выходами блока обработки прерывания, третий и четвертый выходы блока обработки прерывания соединены соответственно с информационными входами третьего и четвертого-передатчиков управляющих сигналов, входы выборки и запроса прерывания блока обработки прерывания подключены к выходам первого и второго приемников управляющих сигналов, входы которых являются Соответствующими входами устройства для подключения к магистралям микроЭВМ и магистрали периферийных устройств, выходы первого, второго и третьего передатчиков являются соответствующими выходами устройства для подключения к магистрали микроЭВМ, инверсный выход триггера управления соединен с разрешающими входами третьего и четвертого передатчиков управляющих сигналов, выход которого является выходом устройства для подключения к магистрали периферийных устройств, разрешающие входы первого и второго передатчиков управляющих сигналов соединены с первой группой выходов узла усилителей управляющих сигналов, первым входом выбора направления первого и входом, выбора направления третьего коммутаторов управляющих сигналов, разрешающие входы второго и третьего коммутаторов управляющих сигналов соединены с прямым выходом

триггера управления, синхровход которого подключен к синхровходу блока обработки прерывания и третьему выходу блока преобразования управляющих сигналов, вход

нулевого разряда адреса которого и адресный вход блока обработки прерывания подключены к первой группе информационных входов-выходов коммутатора информационно-адресных сигналов, вход чтения данных

0 блока обработки прерывания соединен с первой группой информационных входов- выходов первого коммутатора управляющих сигналов и первым входом элемента И-НЕ, вторым входом подключенного к четверто5 му выходу блока преобразования управляющих сигналов, вход чтения данных которого соединен с первым входом элемента ИЛИ и с второй группой информационных входов-выходов первого коммутатора

0 управляющих сигналов, второй вход выбора направления которого соединен с второй группой выходов узла усилителей управляющих сигналов, входом выбора направления второго коммутатора управляющих

5 сигналов, третьим входом элемента И-НЕ и вторым входом элемента ИЛИ, установочный вход триггера управления соединен с второй группой выходов узла усилителей управляющих сигналов, вход адреса вектора

0 блока обработки прерывания является входом задания адреса вектора прерывания устройства.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок преобразования управля5 ющих сигналов содержит три элемента ИЛИ, три элемента И-НЕ. четыре элемента И, пять элементов задержки, два элемента НЕ, два триггера и два элемента ИЛИ-НЕ, первую и вторую группы информационных

0 входов блока, первую и вторую группы выходов блока, вход блокировки блока, входы нулевого разряда адреса, ответа и чтения блока, с первого по четвертый выходы блока, причем выходы первых элементов ИЛИ

5 и 1/1-НЕ, первый вход первого элемента ИЛИ соединены соответственно с входом первого элемента задержки и первым входом первого элемента И, выход первого элемента НЕ соединен с первым входом второго эле0 мента И-НЕ, выходом подключенного через второй элемент задержки к первому входу третьего элемента И-НЕ, второй вход которого соединен с инверсным выходом первого триггера, синхровходом подключенного к

5 выходу третьего элемента задержки, прямой и инверсный выходы второго триггера соединены с первыми входами второго и третьего элементов И соответственно, выходы которых подключены к первым входам первого и второго элементов ИЛ И-НЕ соответственно, вторые входы которых подключены к выходу второго элемента НЕ, выход четвертого элемента задержки соединен с первым входом второго элемента И/11/1, выход которого является первым выходом бло- ка, выход пятого элемента задержки соединен с первым входом четвертого элемента И, второй вход которого является входом блокировки блока, первый вход и выход третьего элемента ИЛИ являются соответственно входом ответа и четвертым выходом блока, вход чтения блока соединен с вторым входом второго элемента ИЛИ и является вторым выходом блока, выходы первого элемента И. первого элемента задержки, четвертого элемента И и соответствующий разряд второй группы информационных входов блока образуют вторую группу выходов блока, первый и второй входы первого элемента И-НЕ, соединенные соответственно с первым и вторым входами первого элемента ИЛИ, второй вход первого элемента И и вход пятого элемента задержки, соединенный с третьим выходом блока, образуют вторую группу информационных входов блока, вход сброса первого триггера, соединенный с синхровходом второго триггера, входами первого элемента НЕ и третьего элемента задержки, второй вход второго элемента И-НЕ, соединенный с информационным входом первого триггера, с вторыми входами второго и третьего элементов И, вход второго элемента НЕ, соединенный с входом четвертого элемента задержки, и

второй вход третьего элемента ИЛИ образуют первую группу информационных входов блока, выходы первого и второго элементов ИЛИ-НЕ, третьих элементов И-НЁ и ИЛИ и

вход первого элемента НЕ, соединенный с первой группой информационных входов блока, образуют первую группу выходов блока.

3. Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок обработки прерываний содержит вход задания адреса для считывания вектора, дешифратор адреса, триггер, первый и второй элементы И, с первой по третью линии задержки, элемент НЕ, адресный вход, вход выборки, синхровход блока, входы чтения блока и запроса прерывания, с первого по четвертый выходы блока, причем синхровход триггера соединен через первый элемент задержки с синхровходом

блока и входом сброса триггера, информационным входом и прямым выходом подключенного соответственно к выходу дешифратора адреса и первому входу первого элемента И, выход которого через

второй и третий элементы задержки соединен с четвертым и вторым выходами блока, первый вход второго элемента И соединен через элемент НЕ с выходом первого элемента И, а выход является третьим выхадом блока, вторые входы первого и второго элементов И и инверсный выход триггера являются соответственно входами чтения и запроса прерывания и первым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обмена информацией | 1985 |

|

SU1278872A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

Изобретение откосится к вычислительной технике и может быть использовано в многопроцессорных вычислительных комплексах, Целью,настоящего изобретения является расширение функциональных возможностей устройства, за счет обеспечения возможности подключения к устройству магистрали периферийных устройств, не совпадающей по типу с магистралью микроЭВМ. Цель достигается тем,, что в устройство, содержащее коммутатор управляющих сигналов, триггер управления, первый коммутатор управляющих сигналов, узел усилителей управляющих сигналов и элемент НЕ, введены два коммутатора управляющих сигналов, блок преобразования управляющих сигналов, блок обработки прерывания, элемент И, элемент И-НЕ, элемент ИЛИ, два приемника управляющих сигналов и четыре передатчика управляющих сигналов. 2 з.п. ф-лы, 3 ил.

Фиг /

fr53

29

Ь7.3

47

Фиг. 2

85 N.

22

56

67

Фиг.З

69

гг.

70

71

| f | |||

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1986 |

|

SU1367018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1988 |

|

SU1508220A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1990-05-07—Подача