Изобретение относится к вычислительной технике и может быть использовано при построении устройств обработки частотных сигналов.

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности формирования выходного сигнала с частотой, определяемой комбинацией частот двух входных сигналов.

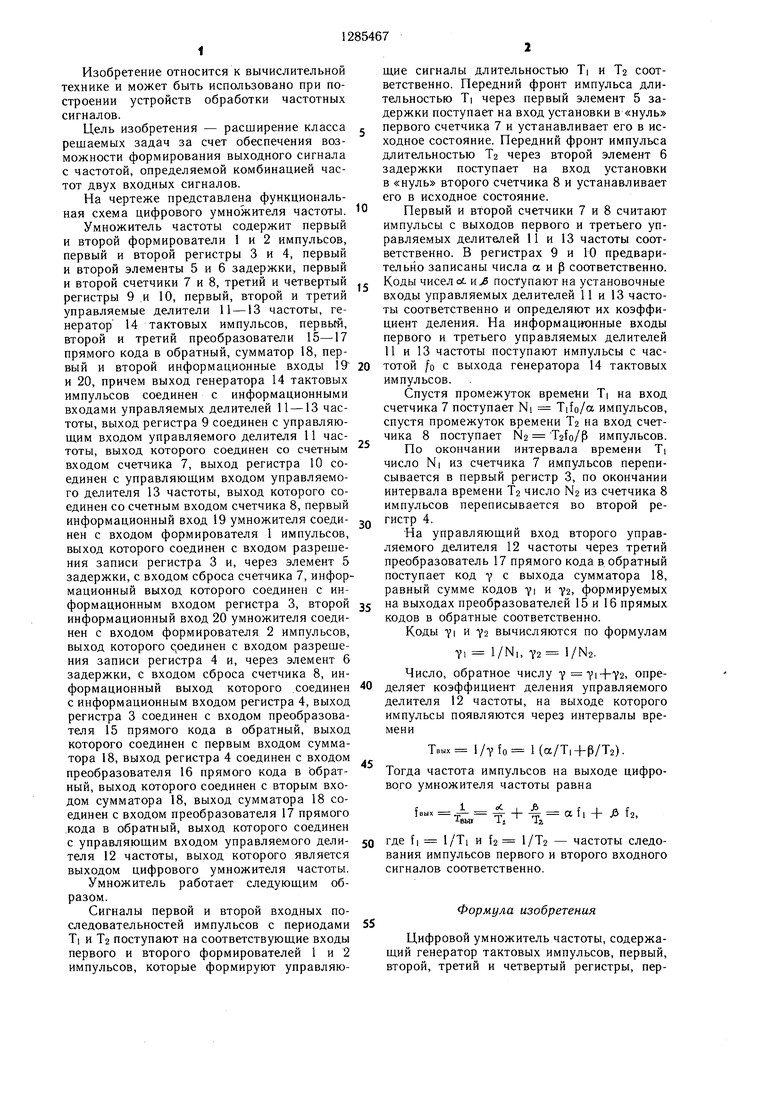

На чертеже представлена функциональная схема цифрового умножителя частоты.

Умножитель частоты содержит первый и второй формирователи 1 и 2 импульсов, первый и второй регистры 3 и 4, первый и второй элементы 5 и 6 задержки, первый и второй счетчики 7 и 8, третий и четвертый регистры 9 .и 10, первый, второй и третий управляемые делители 11 -13 частоты, генератор 14 тактовых импульсов, первый, второй и третий преобразователи 15-17 прямого кода в обратный, сумматор 18, первый и второй информационные входы 19 и 20, причем выход генератора 14 тактовых импульсов соединен с информационными входами управляемых делителей 11 -13 частоты, выход регистра 9 соединен с управляющим входом управляемого делителя 11 частоты, выход которого соединен со счетным входом счетчика 7, выход регистра 10 соединен с управляющим входом управляемого делителя 13 частоты, выход которого соединен со счетным входом счетчика 8, первый информационный вход 19 умножителя соеди- нен с входом формирователя 1 импульсов, выход которого соединен с входом разрешения записи регистра 3 и, через элемент 5 задержки, с входом сброса счетчика 7, информационный выход которого соединен с информационным входом регистра 3, второй информационный вход 20 умножителя соединен с входом формирователя 2 импульсов, выход которого цоединен с входом разрешения записи регистра 4 и, через элемент 6 задержки, с входом сброса счетчика 8, информационный выход которого соединен с информационным входом регистра 4, выход регистра 3 соединен с входом преобразователя 15 прямого кода в обратный, выход которого соединен с первым входом сумматора 18, выход регистра 4 соединен с входом преобразователя 16 прямого кода в обратный, выход которого соединен с вторым входом сумматора 18, выход сумматора 18 соединен с входом преобразователя 17 прямого кода в обратный, выход которого соединен с управляющим входом управляемого дели- теля 12 частоты, выход которого является выходом цифрового умножителя частоты.

Умножитель работает следующим образом.

Сигналы первой и второй входных последовательностей импульсов с периодами TI и Т2 поступают на соответствующие входы первого и второго формирователей 1 и 2 импульсов, которые формируют управляю5

с

О

0 д 5 0 .. 50

щие сигналы длительностью T| и Тг соответственно. Передний фронт импульса длительностью Т| через первый элемент 5 задержки поступает на вход установки в «нуль первого счетчика 7 и устанавливает его в исходное состояние. Передний фронт импульса длительностью Т2 через второй элемент 6 задержки поступает на вход установки в «нуль второго счетчика 8 и устанавливает его в исходное состояние.

Первый и второй счетчики 7 и 8 считают импульсы с выходов первого и третьего управляемых делителей 11 и 13 частоты соответственно. В регистрах 9 и 10 предварительно записаны числа аир соответственно. Коды чисел of. поступают на установочные входы управляемых делителей 11 и 13 частоты соответственно и определяют их коэффициент деления. На информацит)нные входы первого и третьего управляемых делителей 11 и 13 частоты поступают импульсы с частотой fo с выхода генератора 14 тактовых импульсов.

Спустя промежуток времени Т| на вход счетчика 7 поступает NI Tifo/a импульсов, спустя промежуток времени Т2 на вход счетчика 8 поступает N2 T2fo/P импульсов.

По окончании интервала времени TI число NI из счетчика 7 импульсов переписывается в первый регистр 3, по окончании интервала времени Т2 число N2 из счетчика 8 импульсов переписывается во второй регистр 4.

На управляющий вход второго управляемого делителя 12 частоты через третий преобразователь 17 прямого кода в. обратный поступает код у с выхода сумматора 18, равный сумме кодов 71 и 72, формируемых на выходах преобразователей 15 и 16 прямых кодов в обратные соответственно.

Коды 71 и 72 вычисляются по формулам

71 1/N,, 72 1/N2.

Число, обратное числу 7 i+Y2. определяет коэффициент деления управляемого делителя 12 частоты, на выходе которого импульсы появляются через интервалы времени

Твых 1/7 fo 1(а/Т|+Р/Т2).

Тогда частота импульсов на выходе цифрового умножителя частоты равна

+ +

где f| 1/Ti и (2 1/Т2 - частоты следования импульсов первого и второго входного сигналов соответственно.

Формула изобретения

Цифровой умножитель частоты, содержащий генератор тактовых импульсов, первый, второй, третий и четвертый регистры, первый и второй управляемые делители частоты, первый счетчик, сумматор и первый формирователь импульсов, вход которого соединен с первым информационным входом умножителя, информационный выход первого счетчика соединен с информационным входом первого регистра, выход третьего регистра соединен с управля1Ь1цим входом первого управляемого делителя частоты, выход которого соединен со счетным входом первого счетчика, выход второго управляемого делителя частоты соединен с выходом умножителя, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности формирования выходного сигнала с частотой, определяемой комбинацией частот двух входных сигналов, в него введены первый, второй и третий преобразователи прямого кода в обратный, первый и второй элементы задержки, второй счетчик, третий управляемый делитель частоты и второй формирователь импульсов, вход которого соединен с вторым информационным входом умножителя, выход первого формирователя импульсов соединен с входом разрешения записи первого регистра и с входом первого элемента задержки, выход которого соединен с входом сброса первого счетчика, выход второго формирователя импульсов соединен с входом разрешения записи второго регистра и с входом второго элемента задержки, выход которого соединен с входом сброса второго счетчика, информационный выход второго счетчика соединен с информационным входом второго регистра, выход которого соединен с входом второго преобразователя прямого кода в обратный,

выход первого регистра соединен с входом первого преобразователя прямого хода в обратный, выход которого соединен с первым входом сумматора, выход второго преобразователя прямого кода в обратный соединен с вторым входом сумматора, выход которого соединен с входом третьего преобразователя прямого кода в обратный, выход которого соединен с управляющим входом второго управляемого делителя частоты, выход четвертого регистра соединен с управляющим

0 входом третьего управляемого делителя частоты, выход которого соединен со счетным входом второго счетчика, выход генератора тактовых импульсов соединен с информационными входами первого, второго и третьего управляемых делителей частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

| Устройство для моделирования сигнала короткого замыкания | 1986 |

|

SU1309055A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств обработки частотных сигналов. Цель изобретения - расширение класса решаемых задач за счет возможности формирования выходного сигнала с частотой, определяемой комбинацией частот двух входных сигналов. Умножитель содержит два формирователя 1, 2 импульсов, четыре регистра 3, 4, 9, 10, два элемента 5, 6 задержки, два счетчика 7, 8, три управляемых делителя 11, 12, 13 частоты, генератор 14 тактовых импульсов, три преобразователя 15, 16, 17 прямого кода в обратный, сумматор 18 и два информационных входа 19, 20 с соответствующими связями. Выходной сигнал умножителя содержит в себе две входные частоты, пропорциональные соответственно двум постоянным числам, предварительно записанным в соответствующие регистры умножителя. 1 ил. (Л ю 00 сд 4;ib ot Выход

| Следящий умножитель частоты | 1979 |

|

SU851406A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой умножитель частоты | 1980 |

|

SU957206A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-06-25—Подача