Изобретение относится к вычислиельной технике и может быть использовано в универсальных и специализиованных щтфровых вычислительных маинах,

Цель изобретения - повышение бысродействия устройства.

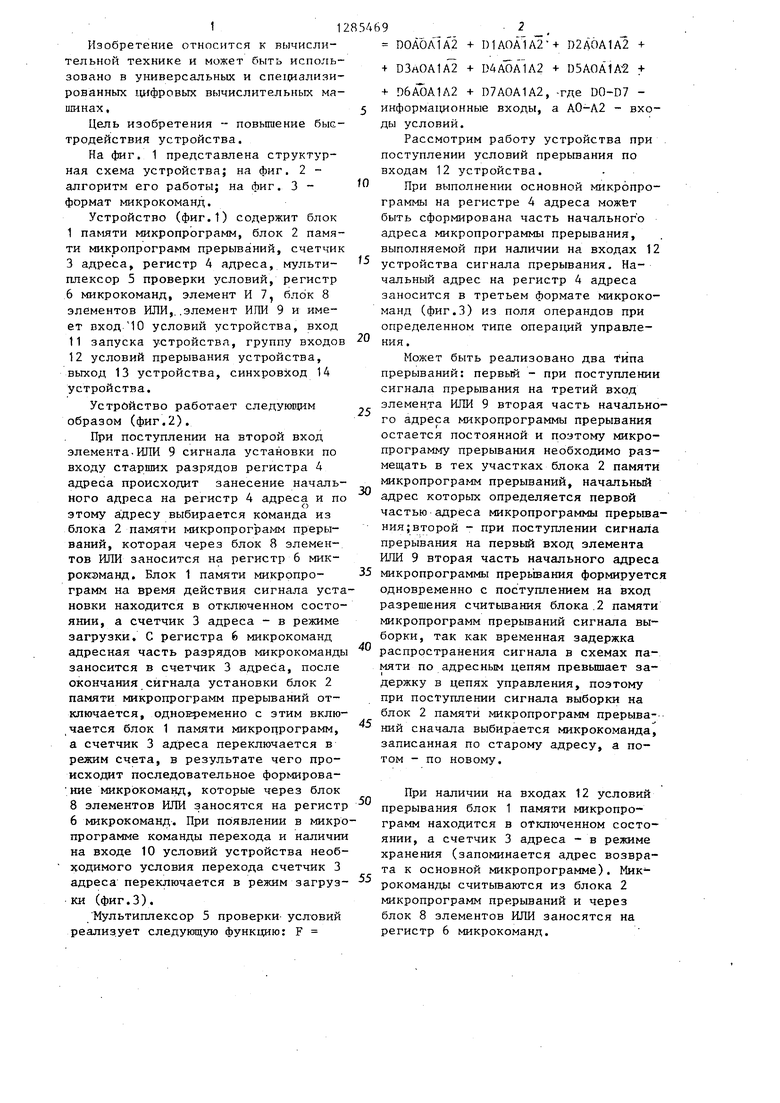

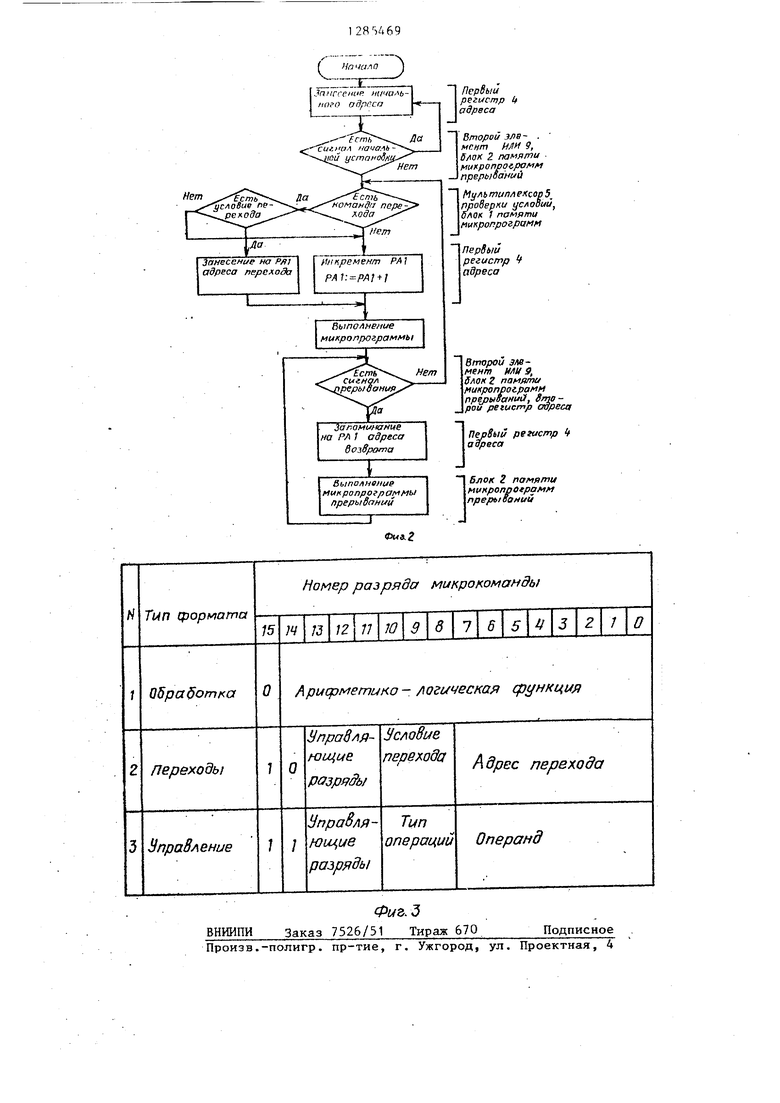

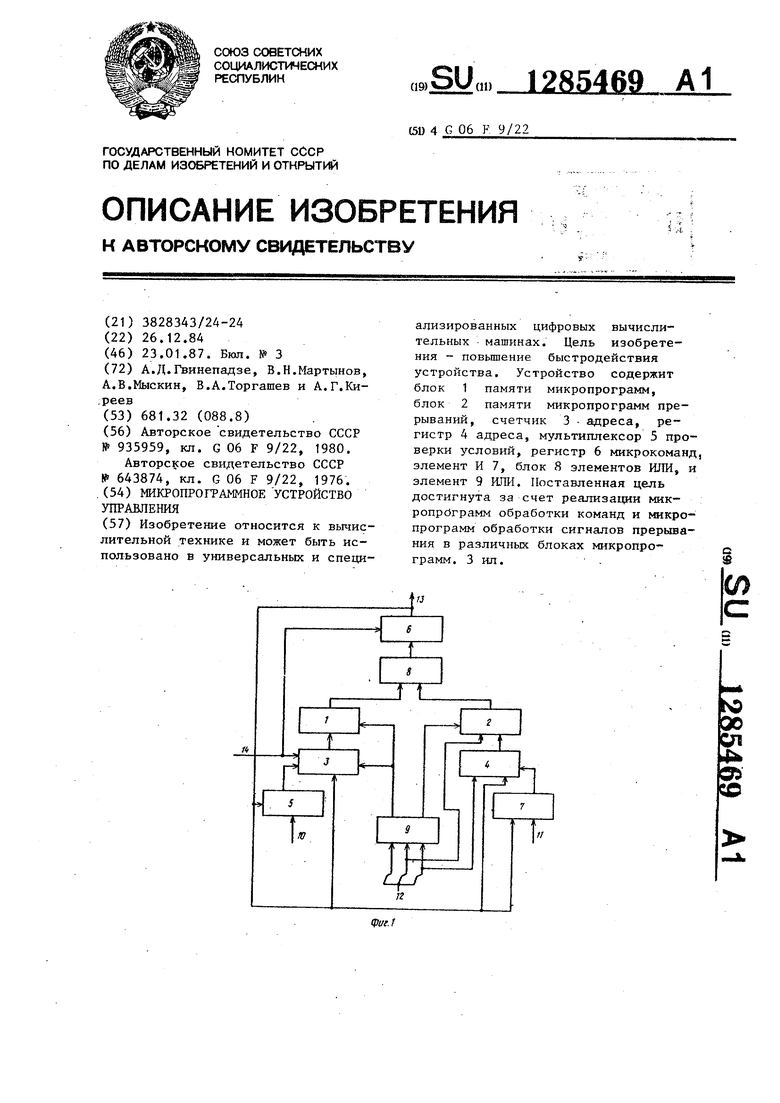

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - алгоритм его работы; на фиг. 3 - ормат микрокоманд.

Устройство (фиг.1) содержит блок

Iпамяти микропрограмм, блок 2 памяти микропрограмм прерываний, счетчик 3 адреса, регистр Д адреса, мультиплексор 5 проверки условий, регистр 6 микрокоманд, элемент И 7, блок 8 элементов ИЛИ,, .элемент ИЛИ 9 и имеет Бход МО условий устройства, вход

IIзапуска устройства, группу входов 12 условий прерывания устройства, выход 13 устройства, синхровход 14 устройства.

Устройство работает следуюпщм образом (фиг.2).

При поступлении на второй вход элемента.ИЛИ 9 сигнала установки по входу старших разрядов регистра 4 адреса происходит занесение начального адреса на регистр 4 адреса и по этому адресу выбирается команда из блока 2 памяти микропрограмм прерываний, которая через блок 8 элементов ИЛИ заносится на регистр 6 мик- рокэманд. Блок 1 памяти микропрограмм на время действия сигнала установки находится в отключенном состоянии, а счетчик 3 адреса - в режиме загрузки. С регистра 6 микрокоманд адресная часть разрядов микрокоманды заносится в счетчик 3 адреса, после окончания сигнала установки блок 2 памяти микропрограмм прерываний отключается, одновременно с этим включается блок 1 памяти микропрограмм, а счетчик 3 адреса переключается в режим счета, в результате чего происходит последовательное формирова- ние микрокоманд, которые через блок 8 элементов ИЛИ заносятся на регистр 6 микрокоманд. При появлении в микропрограмме команды перехода и наличии на входе 10 условий устройства необ- водимого условия перехода счетчик 3 адреса переключается в режим загрузки (фиг.З).

Мультиплексор 5 проверки- условий реализует следующую функцию: F

5

0

5

0

5

0

5

0

5

DOAOA1A2 + 1)1АОА1Л2ч- D2A6A1A2 + + D3rtOA1A2 + D4AOA1A2 + D5AOA1A-2 +

+ D6AOA1A2 + D7AOA1A2, -где DO-D7 - информадаонные входы, а АО-А2 - входы условий.

Рассмотрим работу устройства при поступлении условий прерывания по входам 12 устройства.

При выполнении основной микропрограммы на регистре 4 адреса может быть сформирована часть начального адреса микропрограммы прерывания, выполняемой при наличии на входах 12 устройства сигнала прерывания. Начальный адрес на регистр 4 адреса заносится в третьем формате микрокоманд (фиг.З) из поля операндов при определенном типе операгщй управления .

Может быть реализовано два tипa прерываний: первый - при поступлении сигнала прерьтания на третий вход элемента ИЛИ 9 вторая часть начального адреса микропрограммы прерывания остается постоянной и поэтому микропрограмму прерывания необходимо размещать в тех участках блока 2 памяти микропрограмм прерываний, начальный адрес которых определяется первой частью адреса микропрограммы прерьта- ния;второй - при поступлении сигнала прерывания на первый вход элемента ИЛИ 9 вторая часть начального адреса микропрограммы прерьЬания формируется одновременно с поступлением на вход разрешения считьшания блока .2 памяти микропрограмм прерываний сигнала выборки, так как временная задержка распространения сигнала в схемах памяти по адресным цепям превьппает задержку в цепях управления, поэтому при поступлении сигнала выборки на блок 2 памяти микропрограмм прерываний сначала выбирается микрокоманда, записанная по старому адресу, а потом - по новому.

При наличии на входах 12 условий прерывания блок 1 памяти микропрограмм находится в отключенном состоянии, а счетчик 3 адреса - в режиме хранения (запоминается адрес возврата к основной микропрограмме). Мик- рокоманды считьшаются из блока 2 микропрограмм прерываний и через блок 8 элементов ИЛИ заносятся на регистр 6 микрокоманд.

.3

Формула изобретени

Микропрограммное устройство управления, содержащее блок памяти микропрограмм, регистр адреса, элемент И и мультиплексор проверки ус- ловий, информационный вход которого соединен с входом условий устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены счетчик адреса, элемент ИЛИ, блок памяти микропрограмм прерываний, регистр микрокоманд, блок элементов ИЛИ, причем выход поля анализа условий регистра микропрограмм соединен с управляющим входом мультиплексора проверки условий, выход поля адреса перехода регистра микрокоманд соединен с информационным входом счетчика адреса, выход поля адреса прерываний регист- ра микрокоманд соединен с информационным входом старших разрядов регистров адреса, информационный вход регистра микрокоманд соединен с выходом блока элементов ИЛИ, первый и второй входы блока элементов ИЛИ соединены соответственно с выходом блока памяти микропрограмм и с выходом блока памяти микропрограмм прерываний, вход разрешения считывания которого соединен с инверсным выходом элемента ИЛИ, адресные входы

69 . мпад1иего и старших разрядов блока памяти микропрограмм прерываний соединены соответственг{о с первым входом условия прерывания устройства и с выходом регистра адреса, вход записи которого подключен к выходу элемента И, информационный вход млаших разрядов регистра адреса соединен с вторым входом условия прерывания устройства, прямой выход элемента ИЛИ соединен с входом разрешения считывания блока памяти югкрспро- грамм и с входом разрешения счета счетчика адреса, первьй вход элемента И подключен к входу запуска уст- ройства, а первый, второй и третий входы элемента ИЛИ соединены соответственно с первым вторым и третьим входами условия прерывания устройства, выход разрешения загрузки регистра микрокоманд соединен с вторым входом элемента И, выход поля микроопераций регистра микроко-. манд подключен к выходу устройства, выход мультиплексора проверки условий соединен с входом разрешения загрузки счетчика адреса, выход которого подключен к адресному входу блока памяти микропрограмм, синхро- вход устройства соединен со счетным входом счетчика адреса и входом записи регистра микрокоманд.

Нет

Занесение на Рл; адреса перехоЗЬ

Инкремент РА / РАГ.рА1 + 1

П Первый

регистр if I адреса

Второй для- . мент ИЛИ 9, блик 2 памяти Mufponpof:paMM прерываний

Мультиплексор 5 проверки условий блок I памяти микропрограмм

Первый регистр t адреса

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955060A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных цифровых вычислительных машинах. Цель изобретения - повьппение быстродействия устройства. Устройство содержит блок 1 памяти микропрограмм, блок 2 памяти микропрограмм прерываний, счетчик 3 адреса, регистр 4 адреса, мультиплексор 5 проверки условий, регистр 6 микрокоманд, элемент И 7, блок 8 элементов Ш1И, и элемент 9 ИЛИ. Поставленная цель достигнута за счет реализации мик- ропрбграмм обработки команд и микропрограмм обработки сигналов прерывания в различных блоках микропрограмм, 3 ил. . с ю эо ел

Выполнение MUK-punpozpai Mbi

Заг амииан е на РА J адреса

возврата

Sfrmpou зле- мент или 9, Улик Z понято fiUKponpoifjai M преоыВаниС, Второй регистр aapecti

Первый регистр аЭрвса

L

выполнение микрапрог/гаммы прерывании

Блок 2 памяепи Muxponpotpaf M npepoieoMuu

| Микропрограммное устройство управления | 1980 |

|

SU935959A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1976 |

|

SU643874A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | |||

Авторы

Даты

1987-01-23—Публикация

1984-12-26—Подача