(З) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1976 |

|

SU643874A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1019450A1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807288A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

.

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных цифровых вычислительных машинах.

Известно микропрограммное устрюйство управления, содержащее память микрокоманд, регистр микрокоманд, дешифратор адреса оперативной памяти, оперативную память, блок реверсивных формирователей тога, дешифратор адреса микрокоманды, регистр адреса микрЬкоманды, блок усилителей чтения, коммутатор, шийратор и регистр регенерации l .

Недостатком устройства является большой объем оборудования и незначительное быстродействие.

Наиболее близким к изобретению по технической сущности является микропрограммное устройство управления, содержащее блок памяти микропрограмм, блок проверки условий и регистры адреса .

Однако известйому устройству присущи низкое быстродействие и сложность;

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержаи ее блок памяти микропрограмм, блок проверки условий и два регистра адреса, причем группа информацирнных выходов блока проверки условий соединена с группой информационных входов первого регистра адtoреса, выходы первого и второго регистров адреса соединены соответственно с первым и вторым адресными входами памяти микропрограмм, первая группа выходов которого соединена с

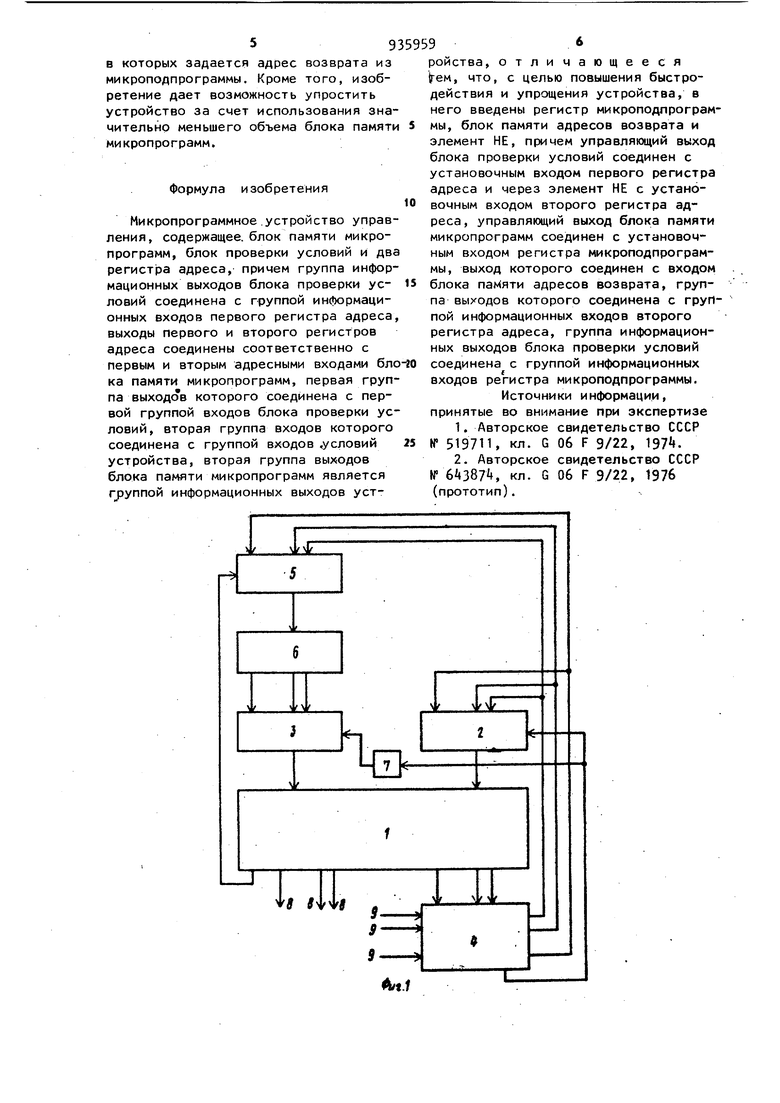

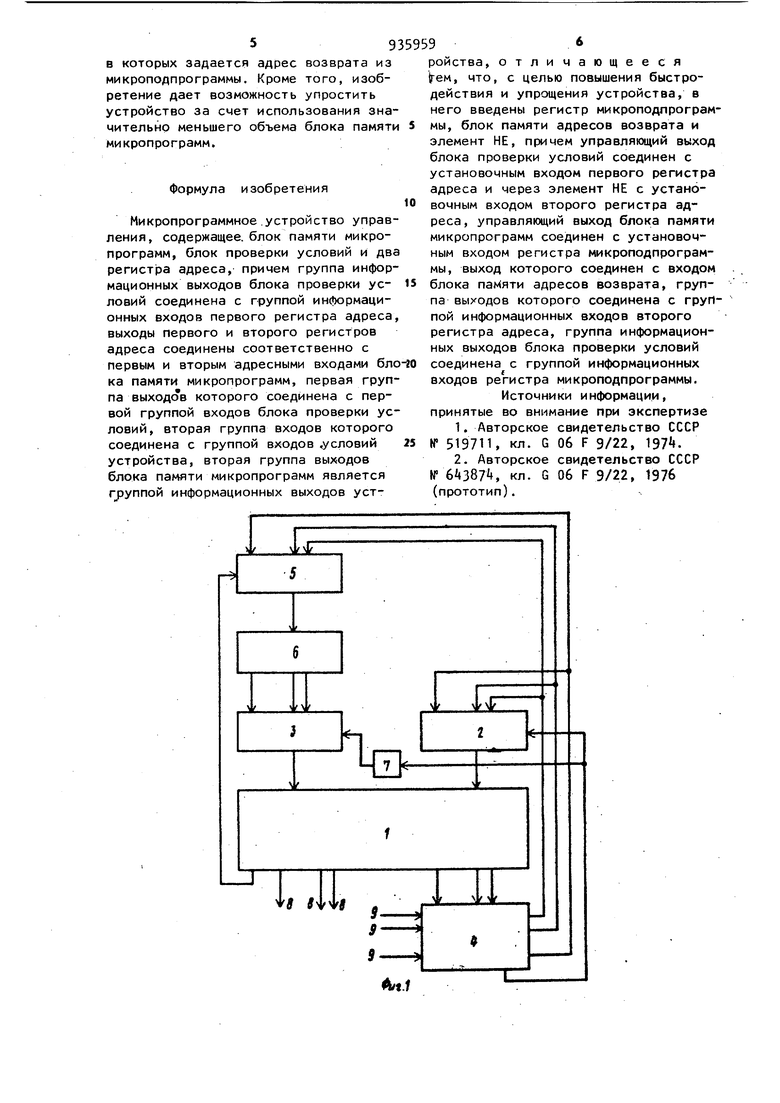

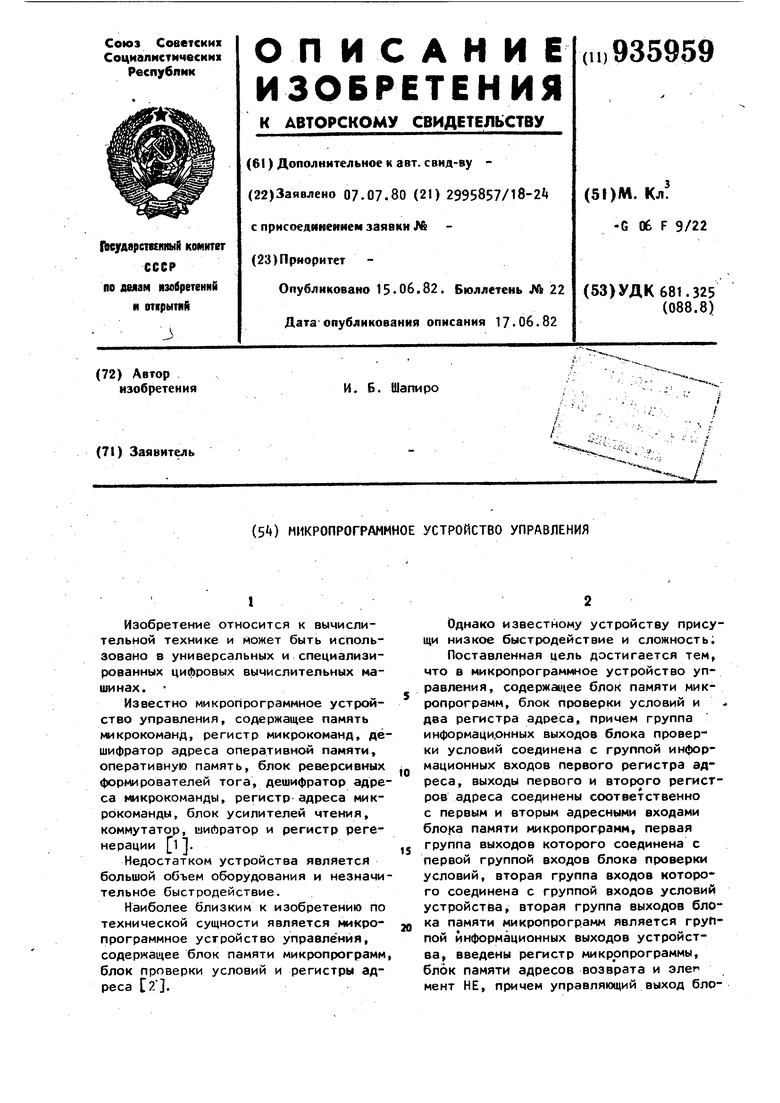

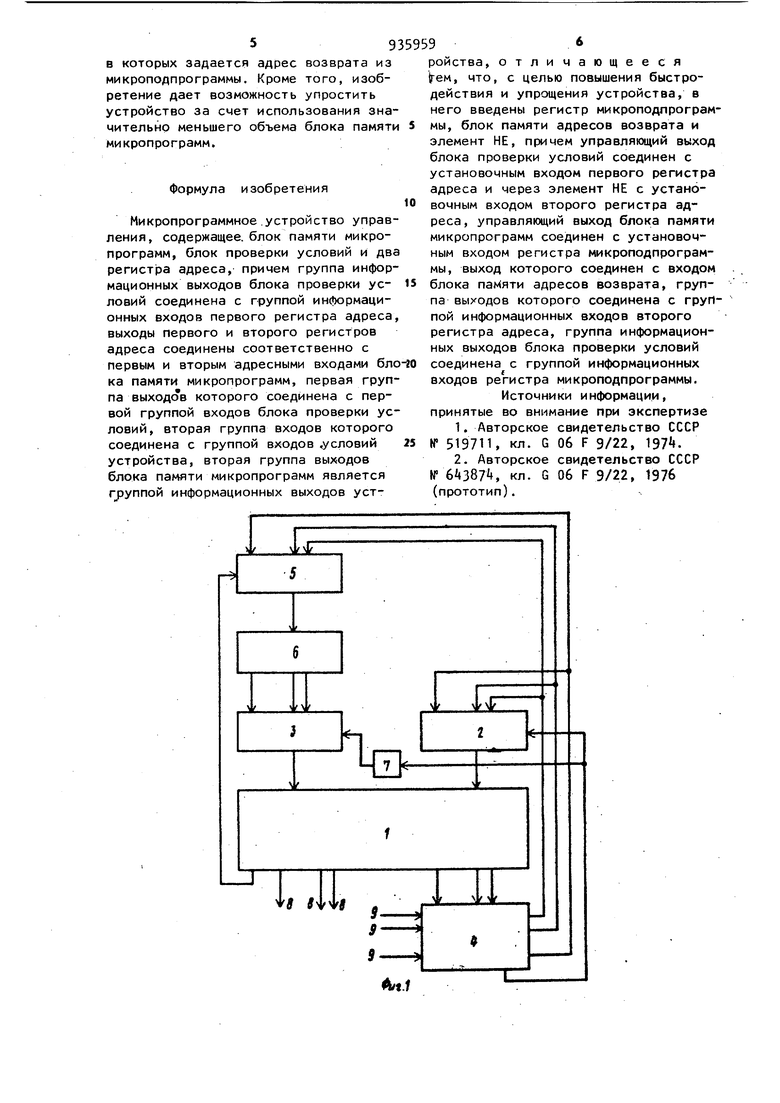

IS первой группой входов блока проверки условий, вторая группа входов которого соединена с группой входов условий устройства, вторая группа выходов блока памяти микропрограмм является rpyh20пой информационных выходов устройства, введены регистр микропрограммы, блок памяти адресов возврата и элеп мент НЕ, причем управляющий выход блока проверки условии соединен с установочным входом первого регистра адреса и через элемент НЕ соединен с установочным входом второго регистра адреса, управляющий выход блока памяти микропрограмм соединен с установочным входом регистра микроподпрограммы, выход которого соединен со входом блока памяти адресов возвр та, группа выходов которого соединена с группой информационных входов второго регистра адреса, группа информационных выходов блока проверки условий соединена с .группой инфор(ационных входов регистра микроподпрограммы. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - блоксхема -блока проверки условий. Устройство содержит блок 1 памяти микропрограмм, регистры 2 и 3 адреса блок Ц проверки условий, регистр Б микроподпрограммы, блок 6 памяти адресов возврата, элемент НЕ 7, группу информационных выходов 8 устройства и группу входов 9 условий устройства. Блок проверки условий содержит де шифраторы 10 и 11, группы элементов И 12 и 13 и элементы ИЛИ 14 и 15 Устройство работает следующим образом. Когда не происходит обращение к микроподпрограмме на выходах блока 1 с помощью синхронизирующих сигналов (не показаны производится последова тельное формирование микрокоманд. Причем операционная часть каждой мик рокоманды поступает по выходам 8 в операционные узлы, а адресная часть на блок k проверки условий, на который по входам 9 поступают также осве домительные cигнaJГIЫ. По результатам сравнения адресной части и осведомительных сигналов формируется адрес следующей микрокоманды, который запи сывается в регистр 2 адреса. При это сигнал с управляющего выхода блока k проверки условий разрешает чтение ин формации из регистра 2 адреса, а сиг нал с выхода элемента НЕ 7 запрещает чтение информации из регистра 8 адреса. Рассмотрим работу устройства при выходе на микроподпрограмму. Пусть на информационных выходах блока 4 сформирован последний адрес прерываемой программы. Этот адрес с помощью синхронизирующих сигналов записывается в регистр 2, при этом из блока 1 считывается последняя микрокоманда прерываемой микропрограммы, в управляющем разряде которой записана 1. По фронту сигнала, поступающего с управляющего выхода блока 1 происходит запись в регистр 5 информации, находящейся на его информационных входах, т.е. последнего адреса прерываемой микропрограммы. В следующем такте в регистр 2 адреса записывается адрес первой микрокоманды микроподпрограммы и начинается выполнение микроподпрограммы. Второй и последующие адреса микрокоманд микроподпрограммы формируются так же как и в основной микроподпрограмме по информационным входам с помощью блока k. При этом сигнал с управляющего выхода блока k разрешает чтение информации из регистра 2, а сигнал с выхода элемента НЕ 7 запрещает чтение информации из регистра 3. По последнему адресу прерванной микропрограммы, записанному в регистре 5 с помощью синхронизирующих сигналов, происходит считывание из блока 6 и запись в регистр 3 из соответствующей микроподпрограммы. Таким образом при выполнении определенной микроподпрограммы в регистре 3 хранится адрес микрокоманды, с которой необходимо продолжать основную микропрограмму при выходе из микроподпрограммы. В последней микрокоманде микроподпрограммы в адресной части содержится признак выхода из микроподпрограммы.При этом сигнал с управляющего выхода блока запрещает чтение информации из регистра 2, а сигнал с выхода элемента НЕ 7 разрешает чтение информации из регистра 3. Следующая микрокоманда считывается по адресу, хранящемуся в регистре 3 и таким образом продолжается выполнение прерванной микропрограммы. Изобретение позволяет получить выигрыш по быстродействию для алгоритмов, в которых из каждой микрокоманды возможен переход на одну микроподпрограмму и переход на микроподпрограмму осуществляется по адресу, записанному в микропрограмме, за счет исключения из блока памяти микропрограмм микрокоманд входа в микроподпрограмму. в которых задается адрес возврата из микроподпрограммы. Кроме того, изобретение дает возможность упростить устройство за счет использования значительно меньшего объема блока памяти микропрограмм. Формула изобретения Микропрограммное.устройство управления, содержащее, блок памяти микропрограмм, блок проверки условий и два регист|эа адреса, причем группа информационных выходов блока проверки условий соединена с группой информационных входов первого регистра адреса выходы первого и второго регистров адреса соединены соответственно с первым и вторым адресными входами бло ка памяти микропрограмм, первая группа выходс в которого соединена с первой группой входов блока проверки условий, вторая группа входов которого соединена с группой входов «условий устройства, вторая группа выходов блока памяти микропрограмм является группой информационных выходов

f г

1лл

8 tilt g

у ф у ройства, отличающееся 1гем, что, с целью повышения быстродействия и упрощения устройства, в него введены регистр микроподпрограммы, блок памяти адресов возврата и элемент НЕ, причем управляющий выход блока проверки условий соединен с установочным входом первого регистра адреса и через элемент НЕ с установочным входом второго регистра адреса, управляющий выход блока памяти микропрограмм соединен с установочным входом регистра микроподпрограммы, выход которого соединен с входом блока памяти адресов возврата, группа выходов которого соединена с группой информационных входов второго регистра адреса, группа информационных выходов блока проверки условий соединена с группой информационных входов регистра микроподпрограммы. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 519711, кл. G 06 F 9/22, IS. 2.Авторское свидетельство СССР 6i43Q7k, кл. G 06 F 9/22, 1976 (прототип).

fi il« tf J.

fO

11

. j

9

31

т

m

Авторы

Даты

1982-06-15—Публикация

1980-07-07—Подача