1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных устройствах.

Целью изобретения является повышение достоверности контроля.

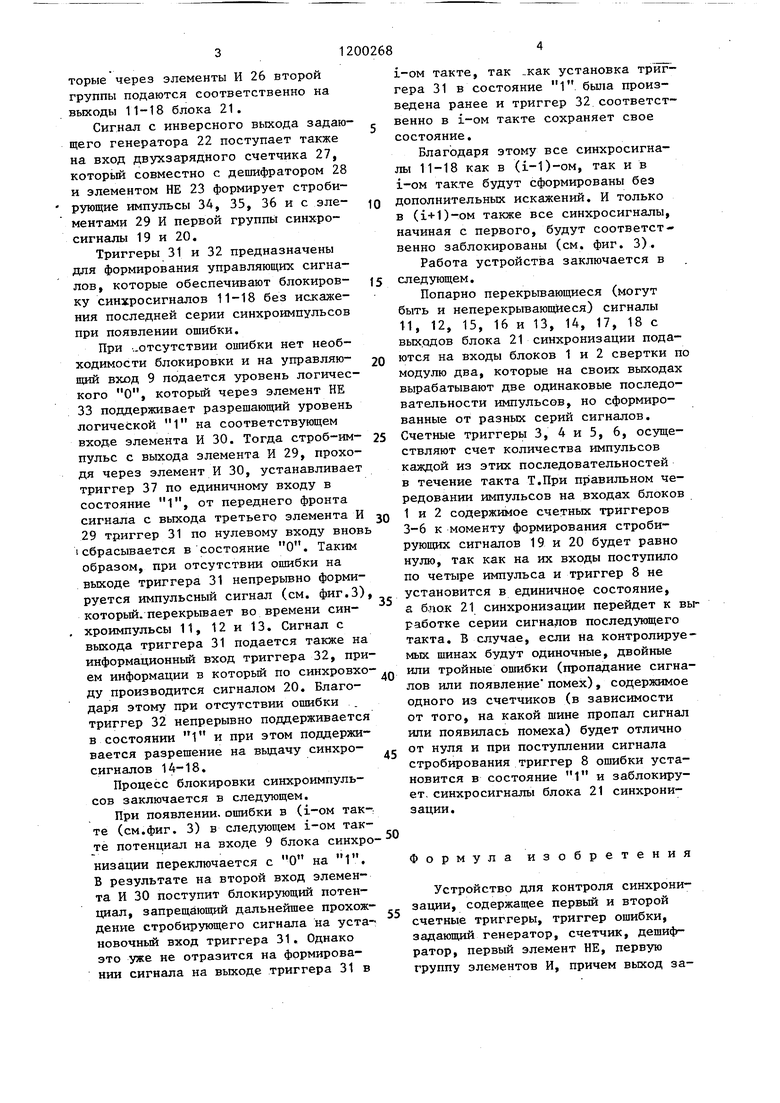

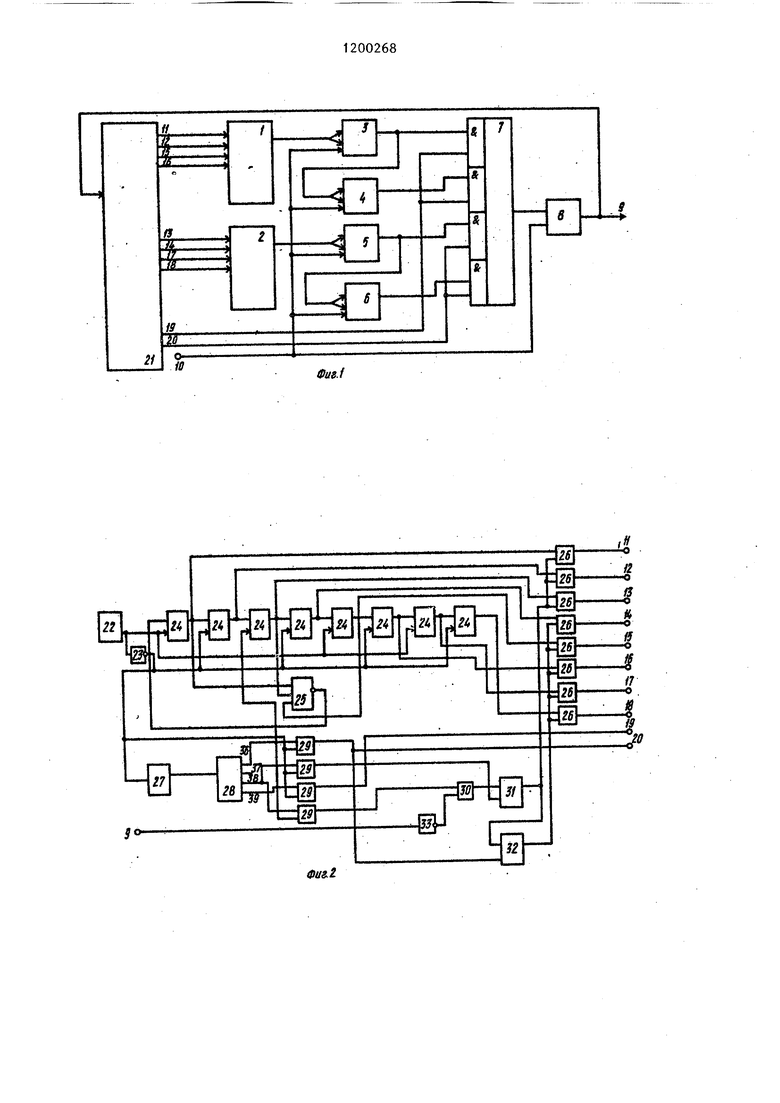

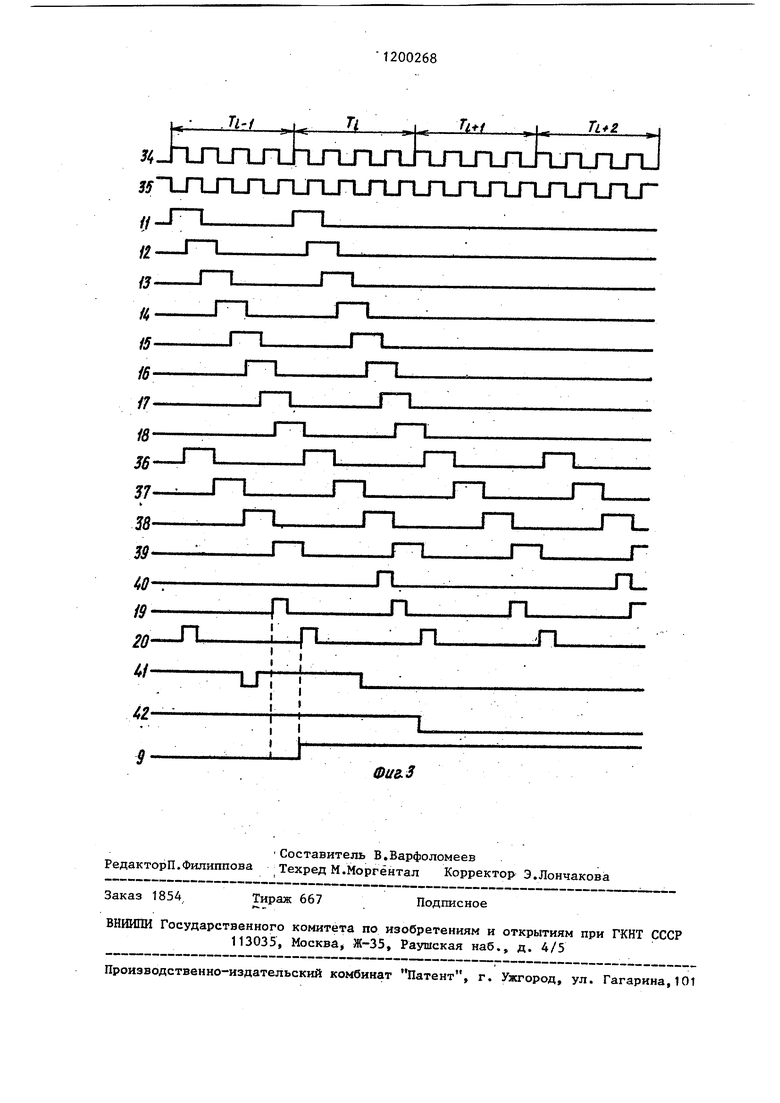

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока синхронизации; на фиг. 3 - временная диаграмма работы устройства.

Устройство содержит блоки 1 и 2 свертки по М0ДУЛЮ два, счетные триггеры 3-6, селектор 7, триггер 8 ошибки, выход 9 устройства, вход 10 начальной установки устройства, выходы 11-20 блока 21 синхронизации.

Блок 21 синхронизации включает задающий генератор 22, элемент НЕ 23, триггеры 24, элемент ИШ-НЕ 25, элементы И 26 первой группы, счетчик 27, дешифратор 28, элементы 29 И второй группы, элемент И 30, триггеры 31 и 32, элемент НЕ 33, выходы дешифратора 28-34, 35, 36.

W

На фиг. 3 номера сигналов соответствуют элементу, на выходе которого формируется данный сигнал.

Работа блока синхронизации заключается в следующем.

Задающий генератор 22 генерирует импульсы, которые инвертируют элемент 23 НЕ и эти импульсы синхронизируют триггеры 24. Причем на синхровходы всех нечетных триггеров 24 подается прямая серия импульсов, а на синхровходы четных триггеров - инт версная серия импульсов. Триггеры 24 образзпот сдвигающий регистр.

Элемент ИЛИ-НЕ 25 позволяет осуществить непрерывный контроль работы регистра сдвига, исключая появление ложных состояний триггеров 2 и 4, а также приводит его в исходное состояние при включении питающего напряжения. В результате функционирования сдвигающего регистра формируются восемь сдвинутых относительно друг друтга серий импульсов (см. фиг. 3), которые через элементы И 26 второй группы подаются соответственно на выходы 11-18 блока 21. Сигнал с инверсного выхода задающего генератора 22 поступает также на вход двухзарядного счетчика 27, который совместно с дешифратором 28 и элементом НЕ 23 формирует стробирующие импульсы 34, 35, 36 и с элементами 29 И первой группы синхросигналы 19 и 20. Триггеры 31 и 32 предназначены для формирования управляющих сигналов, которые обеспечивают блокировку синхросигналов 11-18 без искажения последней серии синхроимпульсов при появлении ощибки. При -..отсутствии оитбки нет необходимости блокировки и на управляющий вход 9 подается уровень логического О, который через элемент НЕ 33 поддерживает разрешающий уровень логической 1 на соответствующем входе элемента И 30. Тогда строб-импульс с выхода элемента И 29, проходя через элемент И 30, устанавливает триггер 37 по единичному входу в состояние 1, от переднего фронта сигнала с выхода третьего элемента И 29 триггер 31 по нулевому входу внов 1 сбрасывается в состояние О. Таким образом, при отсутствии ошибки на выходе триггера 31 непрерьгоно формируется импульсный сигнал (см. фиг.З который, перекрьгеает во времени синхроимпульсы 11, 12 и 13. Сигнал с выхода триггера 31 подается также н информационный вход триггера 32, пр ем информации в который по синхровх ду производится сигналом 20. Благодаря этому при отсутствии ошибки триггер 32 непрерывно поддерживаетс в состоянии 1 и при этом поддержи вается разрешение на вьщачу синхросигналов 14-18. Процесс блокировки синхроимпульсов заключается в следующем. При появлении, ошибки в (i-ом так те (см.фиг. 3) в следующем i-ом так те потенциал на входе 9 блока синхр низации переключается с О на 1. В результате на второй вход элемента И 30 поступит блокирующий потенциал, запрещаюпщй дальнейшее прохож дение стробирующего сигнала на уста новочньй вход триггера 31. Однако это уже не отразится на формировании сигнала на выходе триггера 31 в 1-ом такте, так ..как установка триггера 31 в состояние 1 бьша произведена ранее и триггер 32 соответственно в i-OM такте сохраняет свое состояние. Благодаря этому все синхросигналы 11-18 как в (i-l)-oM, так и в i-OM такте будут сформированы без дополнительных искажений. И только в (i+1)-OM также все синхросигналы, начиная с первого, будут соответственно заблокированы (см. фиг. 3). Работа устройства заключается в следующем. Попарно перекрывающиеся (могут быть и неперекрываюпщеся) сигналы 11, 12, 15, 16 и 13, 14, 17, 18 с вьк.одов блока 21 синхронизации подаются на входы блоков 1 и 2 свертки по модулю два, которые на своих выходах вырабатывают две одинаковые последовательности импульсов, но сформированные от разных серий сигналов. Счетные триггеры 3, 4 и 5, 6, осуществляют счет количества импульсов каждой из этих последовательностей в течение такта Т.При правильном чередовании импульсов на входах блоков 1 и 2 содержимое счетных триггеров 3-6 к моменту формирования стробирующих сигналов 19 и 20 будет равно нулю, так как на их входы поступило по четыре импульса и триггер 8 не установится в единично состояние, а б.лок 21 синхронизации перейдет к выработке серии сигнадов последующего такта. В случае, если на контролируемых шинах будут одиночные, двойные или тройные ошибки (пропадание сигналов или появление помех), содержимое одного из счетчиков (в зависимости от того, на какой шине пропал сигнал или появилась помеха) будет отлично от нуля и при поступлении сигнала стробирования триггер 8 ошибки установится в состояние 1 и заблокирует, синхросигналы блока 21 синхронизации. Формула изобретения Устройство для контроля синхронизации, содержащее первый и второй счетные триггеры, триггер ошибки, задающий генератор, счетчик, дешифратор, первый элемент НЕ, первую группу элементов И, причем выход задающего генератора соединен с входом рпервого элемента НЕ, выход которого соединен со счетным входом счетчика, группа выходов которого соединена с группой входов дешифратора, отличающееся тем, что, с целью повьпиения достоверности контроля в устройство введены два блока сверт ки по модулю два, третий и четвертый счетные триггеры, селектор, десять триггеров, вторая группа элементов И элемент 1ШИ-НЕ, второй элемент НЕ, причем выход первого блока свертки по модулю два соединен со счетным входом Первого счетного триггера, выход которого соединен с первым информационньм входом селектора и счет ным входом второго счетного триггера, выход которого соединен с вторым информационным входом селектора, третий информационный вход которого соединен с выходом третьего счетного триггера и со счетным входом четвертого счетного триггера, выход которо го соединен с четвертьм информационным входом селектора, первый и второй управляющие входы селектора соединены с выходом четвертого элемента И первой группы, выход второго элемента И первой группы соединен с третьим и четвертым упрвляющими входами селектора, выход которого соединен с единичным входом триггера ошибки, нулевой вход которого соединен с входами сброса первого, второго, третьего и четвертого счетных триггеров и является входом начальной установки устройства, выход элемента И соединен с входом второго элемента НЕ и является выходом устройства, выход второго блока свертки по модулю два соединен со счетным входом третьего счетного триггера, выход задающего генератора соединен с синхровходами первого, второго, третьего и четвертого триггеров и с |первьм входом первого элемента И первой группы, выход первого элемента НЕ соединен с синхровходами пятого, шестого, седьмого и восьмого триггеров и с первымигвходами второго, третьего и четвертого элементов И первой группы, первьй выход дешифратора соединен с вторым входом второго элемента И первой группы, второй выход дешифратора соединен с вторыми входами первого и третьего элементов И первой группы, третий выход дешифратора соединен с вторым входом четвертого элемента И первой группы, выход первого триггера соединен с информационным входом пятого триггера, с первым входом элемента |И1Ш-НЕ и с первым входом первого элемента И второй группы, первый вход второго элемента И которой соединен с выходом пятого триггера и с информационным входом второго триггера, выход второго триггера соединен с информационным входом шестого триггера, с вторым входом элемента ИЛИНЕ и с первым входом третьего элемента И второй группы, первый вход четвертого элемента И второй группы соединен с выходом шестого триггера и с информационным входом третьего триггера, выход которого соединен с информационным входом седьмого триггера, с третьим входом элемента ИЛИНЕ и с первым входом пятого элемента И второй группы, первый вход шестого элемента И которой соединен с выходом седьмого триггера и с информационным входом четвертого триггера,, выход которого соединен с информационным входом восьмого триггера и с первым входом седьмого элемента И второй группы, первый вход восьмого элемента И которой соединен с выходом восьмого триггера, выход первого элемента И первой группы соединен с первым входом элемента И, второй вход которого соединен с выходом второго элемента НЕ, выход элемента И соединен с единичным входом девятого триггера, нулевой вход которого соединен с выходом третьего элемента И первой группы, выход второго элемента И первой группы соединен с синхровходом десятого триггера, информационный вход которого соединен с выходом девятого триггера и с вторыми входами первого, второго и третьего элементов И второй группы, выходы первого, второго, пятого и шестого элементов -И второй группы соединены с соответствующими входами первого блока свертки по модулю два, выходы второго, третьего, седьмого и восьмого элементов И второй группы соединены с соответствующими входами вто-, рого блока свертки по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для контроля передачи информации | 1984 |

|

SU1251083A1 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство цифрового интегрирования | 1988 |

|

SU1532922A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Сигнатурный анализатор | 1984 |

|

SU1171797A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для синхронизации цифровой системы | 1981 |

|

SU981980A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных устройствах. Цель изобретения повьпнение достоверности контроля. Устройство содержит блоки 1 и 2 свертки по модулю два, счетные триггеры 3, 4, 5, 6, селектор 7, триггер 8 ошибки. Использование устройства обеспечивает регистрацию ошибки при пропадании сигналов или появлении помех при любом количестве импульсов, кроме кратных четырем. 3 ил.

| Устройство для формирования серий импульсов | 1979 |

|

SU920688A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Распределитель импульсов | 1981 |

|

SU976436A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1983-11-29—Подача