(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Устройство для синхронизации цифровой системы | 1981 |

|

SU981980A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для синхронизации вычислительной системы | 1978 |

|

SU752314A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля синхронизации | 1983 |

|

SU1200268A1 |

| Устройство для синхронизации внешних блоков памяти | 1985 |

|

SU1254457A1 |

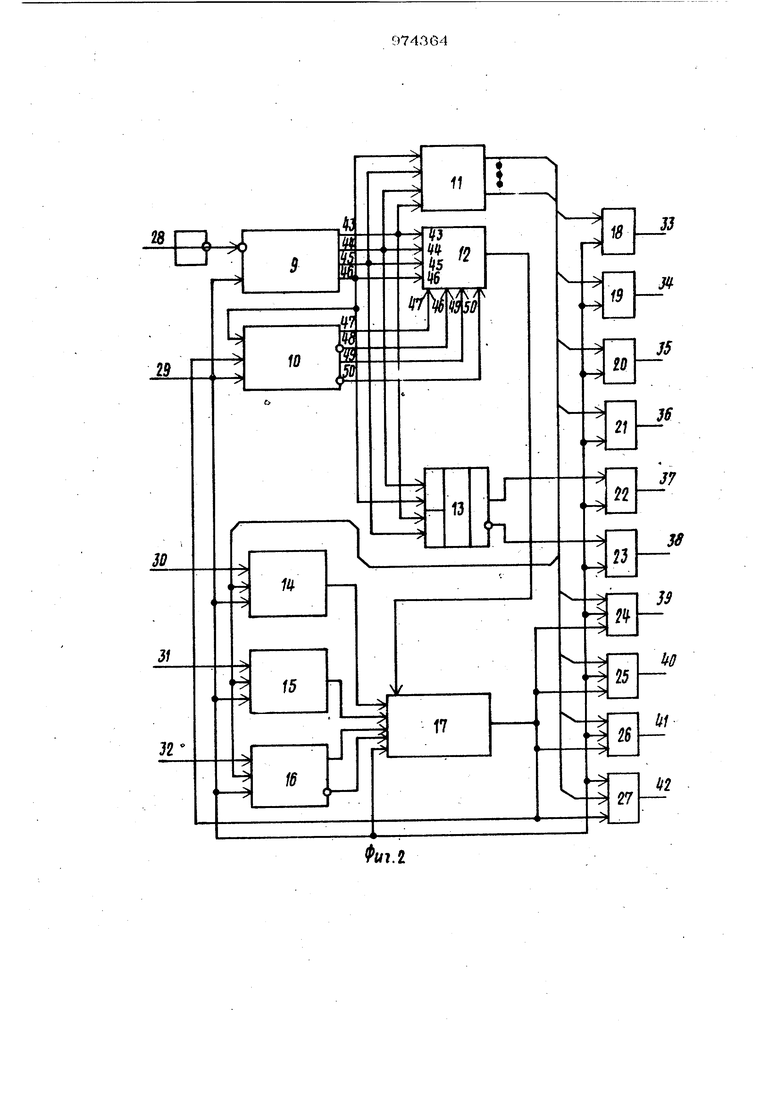

Изобрета1ие относится к вычислительной технике, а именно к синхронизируемы вычислительным системам. Известно устройство для синхронизапии вычислительной системы, содержащее задающий генератор, выходы которого соединены с входами гругаты линий задерж ки, эыходы линий задержки соединены соотве гственно с входами блоков вьфаботки синхросигналов, а выходы блоков выработки синхросигналов соединены с синхровходами триггеров вычислительной сис темы. Это устройство позволяет выработать две фазы синхронизации, сдвинутые на полутакт друг относительно друга Cl3 Недостатком указанного устройства является то, что синхросигналы вырабатываются непрерьшно, т.е. отсутствует возможность управлять временной {щаграммой работы устройства по этапам выполнения команды, которая выполняется в данном устройстве, что затрудняет поиск неисправностей и увеличивает время восстановления вычислительной системы при ее отказе. Наиболее близким к предлагаемому по технической сущности является устройство, содержащее задающий генератор, группа выходов которого соответственно подключена ко входам элементов задержки первой группы, группу блоков выработки синхросигналов, каждый из которых содержит дешифратор, счетчик, селектор, шесть элементов И, при этом в каждсвл блоке выработки синхросигналов выход счетчика соединен со входом селектора и входсж дешифратс а, первый, второй, третий и четвертый выходы ксхторого подключены к первым входам соответственно первого, второго, третьего и четвертого элемента И, первый и вто- ; рой выходы селектора соединены с первыми входеи О соответственно пятого и шестого элемента И, а вторые входы элементов И и вход счетчика каждого из блоков выработки синхросигналов подключены к выходу соответствующего элемента задержки первой группы, причем йыходы элементов И каждого из блоков выработки синхросигналов соединены со входами срответствуюшего элемента задержки второй группы, выходы которых являются выходами устройства ,2 , Это устройство характеризуется невозможностью управления сюосросигналами. Управление синхросигналами необходимо для ускорения процесса нйладки вы числительной системы. При наладке необходимо, чтобы синхр сигналы вырабатьгеались в . различных режимах: автоматическом, тактовом, импульсном. При автоматическом режиме синхросигналы вырабатываются непрерыв но, при тактовом режиме синхросигналы вырабатываются поочередно такт за пактом. При импульс ом режимв синхросигналы вырабатываются поочередно в пределах машинного такта, так как при выпопнетга команды в вычислительной системе задействовано большое количество аппаратуры в виде последовательно вклю ченных регистров с комбинационной схемой на входе. Команды в выгислительной системе выполняются за один или несколько маimjifflbix тактов, последовательно или параллельно. Выполнение одной команды может быт последовательное или параллельное. Опре делить место неисправности аппаратуры при вьшопнении команды становится слож ным, так как нарушение информации при выполнении команды может быть в любо из параллельных цепей или на любом эта пе выполнения. Индикация регистров на инженерном пульте при автоматическом режиме работы вычислительной системы отображает результат выполнения команды. Диагностический режим работы вычислительной системы для вьпЮпнения процедуры Диагноз, т.е. поиск неиспра ной аппаратуры требует обязательно час исправной аппаратуры, без которой невоз можно выполнить данную процедуру (например, ввод диагностических данных в канале, управление этим вьтодом и т.д наладка которых осуществляется с помощью режимов ШАГ и ТАКТ. Целью изобретения является увеличение функциональных возможностей устрой ства путем обеспечения управления синх импульсами в различных режимах. Поставленная цель достигается тем, что в устройстве для синхронизайии вычиспительной: системы, содержащем зада щий 1енератор, первую и вторую группы элементов задержки, группу блоков выработки синхросигналов, каждый из которых содержит счетчик, дешифратор, селектор, первую группу из Шести элементов И, причем группа выходов задающего генератора соединена соответственно со входами элементов задержки первой группы с первого по п -и (где п - число каналов),. и при этом в каждом блоке выработки синхросигналов выходы счетчика соединены соответственно со входами селектора и входами дешифратора, первый, второй, третий, четвертый выходы которого соединень с первыми входами соответственно первого, второго, третьего и четвертого элементов И первой группы, прямой и инверсный выходы селектора соединены с первыми входами соответственно пятого и шестого элементов И, а вторые входы элементов И первой группы и синхровход счетчика каждого из блоков выработки синхросигналов соединены с выходом соответствующего элемента задержки первой группы, причем выходы элементов И первой группы каждого из блоков выработки синхросигналов соединены со входами соответствующих элементов задержки второй группы, выходы которых являются первой группой выходов устройства, введен блок переключателей, блок формирования сигналов управления режимами, с п + 1 по 2 п , элементы задержки первой И второй группы, блок выработки сигналов начальной установки и в каждый блок выработки синхросигналов введены два регистра сдвига, два триггера, узел управления, узел дешифрации и сиавления логического состояния, элолент НЕ, вторая f группа из четьфех элементов И, первые входы которых соединены с синхровходами первого и второго регистров сдвига, с синхровходами первого и второго триггеров, с синхровходом узла управления, с синхровходом счетчика, вход начальной установки которого соединен с выходом элемента НЕ, вход которого соединен с соответствующим выходом элемента с п по 2 п задержки первой группы, инверсный выход второго разряда счетчика соединен с информационным входом первого регистра сдвига, управляюишй вход которого соединен со вторыми входами элементов И второй группы и с выходом узла управления, первый правляющий вход ко- . торого соединен с выходом первого триггера, выход второго триггера соединен со вторым управляющим входом узла управления, третий управляюишй вход которого соединен с прямым выходом первого разряда второго регистра сдвига, инверсный выход второго разряда которого соединен с четвертым управляющим входом узла управления, третьи входы первого, второго, третьего и четвертого элементов И второй группы каждого блока выработки синхросигналов соединены соответственно с первыми входами первого, второго, третьего и четвертого элементов И первой группы, выходы элементов И второй группы соединены со входами соответствующих элементов задержки второй группы, выходы которых $геляются соответствующими выходами второй группы выходов устройства, группа выходов счетчика каждого блока выработки синхросигналов соединена соответственно с первой группой входов узла дешифрашш и сравнения логического состояния, вторая группа входов которого соедини а соответственно с выходами первого регистра сдвига, выход узла дешифрации и сравнения логического состояния соединен с пятым управляющим входом узла управления, управляющие вхо ды первого и второго триггеров и второг регистра сдвига каждого блока выработки синхросигналов соединены с четвертым выходом детиифратора, информационные входь первых триггеров блоков вьфаботки синхросигналов соединены соответственно с первой группой выходов блока формирования сигналов управления, вторая группа выходов которого соединена соответственно с информационныкга входами вторых триггеров блоков выработки синхр сигналов, информационные входы вторых регистров сдвига блоков выработки синхр сигналов соединены соответственно с третьей группой выходов блока формирования сигналов управления, дополнительный выход задающего генератора соедине со входом блока выработки сигналов начальной установки, группа выходов которо го соединена соответственно со входами элементов задержки первой группы с (п + 1) по 2 п -и соответственно, группа , выходов блока переключателей соединена соответственно с группой информационных входов блока формирования сигналов управления, синхровход которого соединен с выходом четвертого элемента И первой групхпз первого блока выработки синхросигналов. Поставленная цель достигается также тем, что узел управления содержит три элемента И-НЕ, элемент И, два селектора, причем первый управляющий вход уэпа управле1шя соединен с управляющими вхо 9 646 дами первого и второго селектора, второй управляющий вход узла управления сое дин ер с первыми входами первого и второго элементов И-НЕ, вторые входы ЙЬторых соединены соответственно с третьим и четвертым управляющими входами узла управления, первые информационные входы первого и второго селекторов соединены с третьим управляющим входом узла управления, выход которого соединен с вьсходом элемента И и с первым входом третьего элемента И-НЕ, второй вход которого соединен с синхровходом узла управления, выход третьего элемента И-НЕ соединен с тактовыми входами первого и второго селектора, прямой выход второго селектора соединен со вторым информационным входом второго селектора, инверсный выход которого соединен со вто.. - рым информационным входом первого селектора, инверсный выход которого соединен с первым входом элемента И, второй и третий входы которого соединены соответственно с вькодами первого к второго элементов И-НЕ, четвертый вход элемента И является пятым управляющим входом узла управления. Поставленная цель достигается также тем, что узел дешифрашш и сравнения логического состояния содержит пять элементов И-НЕ, и при этом первый вход первой группы входов узла соединен с первым входом первого элемента И-НЕ и с первым входом второго элем «ста ИНЕ, выход которого соединен с первым входом третьего элемента И-НЕ, второй вход которсго соединен с выходом первого элемента И-НЕ, второй вход первой группы входов узла соединен с первым входом четвертого элемента И-НЕ и с первым входом пятого элемента И-НЕ, выход которого соединен с третьим входом третьего элемента И-НЕ, четвертый вход которого соединен с выходом четвертого элемента И-НЕ, третий вход первой группы входов узла соединен со вторыми входами второго и пятого элементов И-НЕ, четвертый вход первой группы входов узла соединен со вторыми входами первого и четвертого элементов И-НЕ, первый вход второй групзты входов узла соединен с третьими входами первого и второго элементов И-НЕ, второй вход второй группы входов узла соединен с третьими входами четвертого и пятого элементов И-НЕ, третий вход второй группы входов узла соединен с четвертыми входами второго и пятого элементов ИНЕ, четвертый вход второй группы вхо- дов узла соединен с четвертыми входами первого и четвертого элементов И-НЕ, выход третьего элемента И-НЕ является вьЬсодом узда. Поставленная цепь достигается также тем, что блок формирования сигналов управления режимами содержит два триггер регистр сдвига, три гругаты элементов И, элемент И, причем первый ин(|юрмационный вход блока соединен с -кнформаиаанным входом первого триггера, синхровход которого соединен, с синхровходом второго триггера, синхровход которого соединен с синхровходом третьего триггера, синхровход которого соединен с синхровходом блока, первая грутша выходов которого соединена соответственно с выходами элементов И первой группы, входы которых соединены с выходом первого триггера, второй информационный вход блока соединен с информационным входом второго триггера, выход которого соединен со входами элементов И второй группы, выходы которых являются второй группой выходов блока, третья грутша выходов которого соединена с выходами элементов И третьей группы, входы которых соединены с выходом элемента И, первый вход которого соединен с выходом первого разряйа регистра сдввга и с информационным входом второго разряда ре гистра сдвига, инверсный выход второго разряда регистра сдвига соединен со вторым входом элемента И, информационный вход первого разряда регистра сдвига я& ляется третьим информационным входом блока. Поставленная цель достига«гтся также тем, .что блок выработки сигналов началь ной установки содержит два счетчика и группу элементов И, причем выход перового счетчика соединен с управляющим входом второго дчетчика, информационный вход которого соединен с инверсным выходом второго счетчика и с п€)рвыми вхо дами группы элементов И, вторые входы которых соединены с инверсным выходом первого счетчика и с информационным входом первого счетчика, синхровход которого соединен с синхровходом второго счетчика с третьими входами группы эле ментов И и 5тляется входом блока, выходы группы элементов И являются выходамя блока. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока выработки синхросигналов) на фиг. схема узла упр ления; на фиг. 4 - схем узла дешифрашп и сравнения логического состояния; на фиг. 5 - схема блока переключателей; на фиг. 6 - схема блока формирования сигналов управления режимами на фиг. 7 - схема блока выработки сигналов начальной установки, на фиг. 8 временная диаграмма выработки синхросигналов в режиме ШАГ; на фиг. 9 временная диаграмма синхросигналов в режиме АВТОМАТ. Устройство содержит задающий генератор 1, элем.енты задержки 2, блоки 3 выработки синхросигналов, элементы задержки 4, блок 5 выработки сигналов начальной установки, блок 6 переключателей, блок 7формирования сигналов управления режимами, выходы Э« Блок 3 выработки синхросигналов содержит счетчик 9, регистр 10 сдвига, дешифратор 11, узел 12 дешифрации и сравнения логического состояния содержит селектор 13, триггер 14, триггер 15, регистр сдвига 16, узел управления 17, элементы И 18 - 27, входы 28 - 32, выходы 33 - 42, выходы 43 - 46 счетчика 9, выходы 47 50 регистра 10 и элемент НЕ 51. Узел управления 17 содержит элементы И-НЕ 52, 53, селекторы 54 и 55, элемент И-НЕ 56, элемент И 57. Узел 12 содержит элементы И-НЕ 58-62, выход 63. Блок 7 содержит триггеры 64 и ,65, регистр сдвига 66, группу элементов И 67 - 69, элемент И-НЕ 70. Блок 5 содержит счетчики 71 и 72, группу элементов И 73. Блок 6 содержит переключатели 74 - 77. Устройство работает следующим образом. ЗаЬаюший генератор 1 вырабатывает исходную последовательность, поступающую через элементы 2 задержки, служащие для выравнивания синхросигналов, на входы 29 блоков выработки синхросигналов. Исходная последовательность поступает также на вход блока 5 выработки сигналов начапьной становкя, счетчики 71 и 72 делят исходную последова тельность соответственно на два и на четыре, элемент И 73 блока выработки сигналов начальной установки вырабатывает сигналы начальной установки, поступающие через элементы 2 задержки, служащие также для выравнивания сигналов начальной установки, на вход 28 блоков выработки синхросигналов. Сигналы начальной установки через элемент И-НЕ 61 поступают на вход начальной установки счетчика. Вьфавнивание сигналов начальной установки осуществляется для обеспечения одновременной установки в исходное состояние счетчиков 9 всех бло ков выработки синхросигналов. Исходная последовательность поступает в блоках выработки синхросигналов на синхровход счетчиков 9, которые делят исходную последовательность на четыре. Сигналы со счетчика поступают на входы дешифраторов 11, инверсный выход второго разр да счетчика поступает на информационный вход регистра 1О сдвига, который осуществляет перепись информации счетчика под управлением управляющих сигналов, поступающих от узла управления. Узел управления управляет переписью информации регистра 10 сдвига под управлением сигналов, поступающих на входы ЗО-32, поступающих на входы блоков выработки синхросигналов от блока формирования сигналов управле1гия режимами, который вырабатывает управляющие сигналы в зависимости от положения переключателей обеспечивающих выбор режима АВТОМАТ ШАГ, ТАКТ, ПУСК. Блок 6 переключателей состоит из переключателей 74-76, например Т1КБ1-2 со взаимным сбросом, осуществляющих выбор режима АВТОМАТ, ШАГ, ТАКТ. Переключатель 77 (ПКБ 2 - 7) осуществляет управление по нажатиям кнопки. Сигналы от переключателей в блоке формирования сигналов управления рюжимами синхронизируются и поступают через элементы И 68, 69 и через элементы И-НЕ 7О на входы ЗО32 блоков выработки синхросигналов. В блоках выработки синхросигналов сигналы ШАГ/АВТ, ТАКТ/АВТ, ПУСК синхронизируются триггерами 14, 15 и регистром 16. Синхронизация осуществляется для одновременной установки всех блоков выработки синхросигналов в. заданный режим Регистр 16 осуществляет выработку управляющего импульса длительностью мащинный такт. Узел управления блоков выработки огахросигналов,осуществляет . выработку управляющего сигнала. В режиме ТАКТ селекторы 54 и 55 не работаю В режиме АВТОМАТ на выходе элемента 57 .ет разрешение и первый регистр 10 сдвига блоков выработки синхросигналов переписывает информацию счетчика. Выходы счетчика 9 и первого регистра 10 сдвига сравниваются в блоке дешифрации и сравнения логического состояния, И в каждые моменты времени Тм/4 (где Тм - время машинного такта) происходит сравнение состояний счетчика и дешифратора, следовательно, осуществляется выра ботка непрерывных последовательностей синхросигналов на выходах 33+42 блоков выработки синхросигналов. В режиме ТАКТ происходит блокировка управляющего входа регистра сдвига. При появлении сигнала ПУСК в режиме ТАКТ на входе 32 блоков выработки синхросигналов узел управле1гая разрешает прохождение синхроимпульсов на вход регистра 10 в течение Йлительности Тм. При установке режима ШАГ узел управления блокирует перепись информации регистром 1О сдвига. При появлешш сигнала ПУСК в режиме UJAr узел управления поочередно дает разрешение на время Тм/4 со сдвигом Тм/4, т.е. в каждую четверть такта поочередно появляется разрешетше, что разрешает выработку синхросигналов поочередно в зависимости от ПУСК. Введение режимов ТАКТ и ШАГ устройства позволяет выполнять команды, обрабатывающие канал, поэтапно. С помощью данных режимов работы устройства синхронизации, которое определяет време1шую диаграмму работы канала ЕС 4001, можно последовательно проследить выполнение команды в канале от момента начала выполнения до момента окончания. Каждый этап выполнения отображается на инженерном пульте канала в виде .индикации регистров. В режиме ТАКТ команда выполняется с дискретом одного машинного такта и с частотой, определяемой оператором. В ШАГ команда выполняется с дискретом следования одного синхросигнала устройства синхронизации канала и с частотой, определяемой оператором. Данное устройство позволяет использовать те же цепи выработки синхросигналов, что и в автоматическом режиме и сохраняет параметры синхросигналов автоматического режима. Применение данных режимов работы канала позволяет значительно сократить время и облегчЕГГь процедуру наладки канала при изготовлении и при эксплуата- . шш. Режим ТАКТ и ШАГ могут быть использованы при построении ЭВМ, в которых применяется синхронный принцип работы и имеется устройство выработки синхросигналов, определяющее временную диаграмму обработки команд. Применение данных режимов работы в ЭВМ позволяет сократить процедуру поиска неисправной аппаратуры и уменьшить экономические затраты на обслуживание ЭВМ. Формула изобретения 1. Устройство для синхронизации вычислительной системы, содержащее задаюший генератор, первую и вторую грутшы элементов задержки, группу блоков выработки синхросигналов, каждьгй из которых содержит счетчик, дешифратор, селектор, первую группу элементов И, причем группа выходов задающего генератора соединена соответственно со входами элементов задержки первой группы с первого по п -и (где п - каналов),, в каждом блоке выработки синхросигналов выходы счетчика соединены сос)ТВ(гтственно со входами селектора и входами дешифратора, первый, второй, третий, четвертый выходы которого соединены с первыми входами соотвегственно первого, второго, третьего и четвертого элементов И первой группы, прямой и инверсный выходы селектора соединены с первыми входами соответственно пятого и шестого элементов И, а вторые входы элементов И первой rTDfvnnbi и синхровход счетчика каждоt o из блоков выработки синхросигналов соединены с выходом соответствующего элемента задержки первой группы, причем выходы элементов И первой группы каждого из блоков выработки синхросигналов соединены со входами соответст вующих элементов задержки второй групift r, выходы которых являются первой груп пой выходов устройства,, отлич аю щ е е с я тем, что, с целью расширения функхшональных возможностей за счет обеспечения возможности получения синхр импульсов с регулируемым периодом сле дования, в устройство введен блок переключатепей, блок формирования спягналов управления режимами, с п+ 1 по 2п элементы задержки первой и второй групп, блок выработки сигналов начальной установки и в каждый блок выработки синхррсигналов введены два регистра сдвига, два триггера, узел управления, узел деши рации и сравнения логического состояния, элемент НЕ, вторая группа элементов И, первые входы которых соединены с синхр входами первого и второго регистров сдвига, с синхровходами первого и второго триггеров, с синхровходом узла управления, с синхровходом счетчика, вход на чальиой установки которого соединен с выходом элемента НЕ, вход которого сое динен с соответствующим выходом злемента задержки с п + 1 по 2п первой групзЛы, инверсный выход второго разряда счетчика соединен с информационным входом первого регистра сдвига, управляющи вход которого соедзанен со вторыми входа ivffl элементов И-второй группы и с выходом узла улравйе тя, первый управляющи вход которого соединен с выходом первого триггера, выход второго триггера соединен со вторым управляющим входом узла управления, третий управляющий вход которого соединенс прямым выходом первого разряда второго регистра сдвига, инверсный выход второго разряда которого соединен с четвертым управляющим входом узла управления, третьи входы первого, второго, третьего и четвертого элементов И второй группы каждого блока выработки синхросигналов соединены соответственно с первыми входами первого, второго, третьего и четвертого элементов И первой группы, выходы элементов И второй группы каждого блока выработки синхросигналов соединены со .входами соответствующих элементов задержки второй группы, выходы которых являются соответствующи ми выхрдами второй группы выходов устройства, группа выходов счетчика каждого блока выработки синхросигналов соединена соответственно с первой группой входов узла дешифрации и сравнения логического состояния, вторая группа входов которого соединена соответственно с выходами перового регистра сдвига, выход узла дешифрации и сравнения логического состояния каждого блока вьфаботки синхросигналов соединен с пятым управляюгцйм входом узла управления, управляющие входы пер. вого и второго триггеров и второго регистра сдвига каждого блока выработки синхросигналов соединены с четвертым выходам дешифратора, информационные входы первых триггеров блоков выработки синхросигналов соединены соответственно с первой группой выходов блока формирования сигналов управления, вторая группа выходов которого соединена соответственно с информационными входами вторых триггеров блоков выработки синхросигналов, информационные входы вторых регистров сдвига блоков выработки синхросигналов соединены соответственно с третьей группой выходов блока формирования сигналов управления, дополнительный выход задающего генератора соединен со входом блока выработки сигналов начальной установки, группа выходов которого соединена соответственно со входами элементов задержки первой группы с (п+ +1)-го по 2п -и соответственно, группа выходов блока переключателей соединена соответственно с Группой информационных входов блока формирсвания сигналов управления, синхровход кргорого соединен с выходом четвертого элемента И первой группыпервого блока выработки синхропигиалов. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что узел управления бло ка выработки синхросигналов содержит три элемента И-НЕ, элемент И, два селектора, причем первый управляющий вхо узла управления соединен с управляющим входами первого и второго селекторов, второй утфавляюпшй вход узла управления соединен с первыми входами первого и второго элементов И-НЕ, вторые входы которых соединены соответственно с трет им и четвертым управляющими входами узла управления, первые информационные входы первого и второго селекторов соединены с третьим управляющим входом узла управления, выход которого соединен с выходом элемента И и с первым входом третьего элемента И-НЕ, второй вход которого соединен с синхровходом узла управления, выхоц третьего элемента И-НЕ соединен с тактовыми входами первого и второго селекторов, прямой выход второго селектора соединен со вторым информационным входом второго селектора, инверсный выход которого соединен со вторым информационным входом первого селектора, инверсный выход которого сое динен с первым входом элемента И, второй и третий входы которого соединены соответственно с выходами первого и второго элементов И-НЕ, четвертый вход элемента И является пятым управляющим входом узла управления. 3. Устройство по п. 1, отличаю щ е е с я тем, что узел дешифрации и сравнения логического состояния блока вы работки синхросигналов содержит пять элементов И-НЕ, при этом первый вход .первой группы входов узла соединен с пер вым входом первого элемента И-НЕ и с первым входом второго элемента И-НЕ, выход которсго соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, второй вход первой группы входов узла соединен с первым входом четвертого элемента И-НЕ и с первым входом пятого элемента И-НЕ, выход которого соединен с третьим входом третьего элемента И-НЕ, четвертый вход которого соединен с выходом четвертого элемента И-НЕ, третий вход первой группы входов узла соединен со вторыми входами второго и пятого элементов И-НЕ, четвертый вход первой грулпы входов узла соединен со вторыкли входами первого и четвертого элементов И-НЕ, первый вход второй группы входов узла соединен с третьими входакти первого и пторого элементов И-НЕ, вход второй группы входов узла соединен с третьими входами четвертого и пятчэго элементов И-НЕ, третий вход второй группы входов узЛа соединен с четвертыми входами второго и пятого элементов И-НЕ, вход второй группы входов узла соединен с четвертыми входами перв.ого и четвернтого элементов И-НЕ, выход третьего элемента И-НЕ является выходом узла. 4.Устройство по п. 1, о т л и ч а е е с я тем, что блок формирования сигналов управления режимами содержит два триггера, регистр сдвига, три группы элементов И, элемент И, причем первый информационный вход блока соединен с информационным входом первого тритера, синхровход которого соединен с синхровходом второго триггера, синхровход которого соединен с синхровходом третьего триггера, синхровход которого соединен с синхровходом блока, первая группа выходов которого соединена соответственно с выходами элементов И первой группы, входы которых соединены с выходом первого триггера, второй информационный вход блока соединен с информационным входом второго триггера, выход которого соединен со входами элементов И второй, группы, выходы которых являются второй группой выходов блока, третья группа выходов которого соединена с выходами элементов И третьей группы, входы которых соединены с выходом элемента И, первый вход которого соединен с выходом первого разряда регистра сдвига и с информационным входом второго разряда регистра сдвига, инверюный выход второго разряда регистра сдвига соединен со вторым входом элемента И, информациогшый вход первого разряда регистра сдвига является третьим информационным входом блока. 5.Устройство по п. 1, отличающееся тем, что блок выработки сигналов начальной установки содержит два счетчика и группу элементов И, причем выход первого счетчика соединен с управляющим входом второго счетчика, инфорнмаиионный вход которого соединен с инверсным выходом второго счетчика и с первыми входами элементов И группы, вторые входы которых соединены с инверсным выходом первого счетчика и с информацио1П1ым входом первого счетчика, синхро- вход которюго соединен с синхровходом второго счетчика, с третьи га входами элементов И группы и является входом блока, выходы элементов И грутшы являются выходами блока. Источники информации, принятые во внимание при экспертизе 5 1. Электронная вычястггвпьная машина ЕС-1О50, М.,Статистика, 1976, с,254. 2, Авторское свидетельство СССР I 752314, кл. G 06 F 1/04, 1978 (прототип).

JJ JV

J5 JS

37

38

uo jfl

«2

#w.2

1

57

ФитЛ

уск

Фи1.5

lilai

5r

Такт

65

%i

66 36

72,

30

68

S9

32

70

32

Фиг.6

28

7J

Фиг-7

.«ff

Д«1 W,f

тГ

38

Авторы

Даты

1982-11-15—Публикация

1980-11-12—Подача