Изобретение относится к вычислительной технике и может быть использовано для построения интегральных : i полупроводниковых эапоминаюпщх устройств.

Целью изобретения является -упрощение элемента и повышение его надежности.

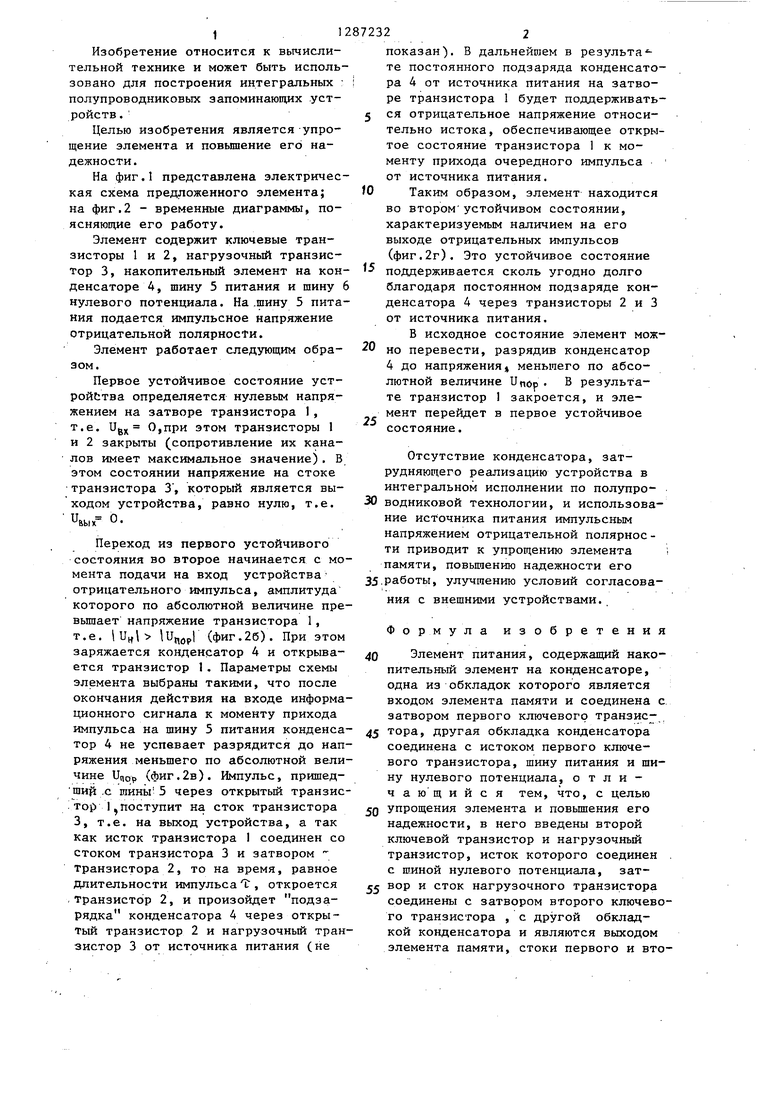

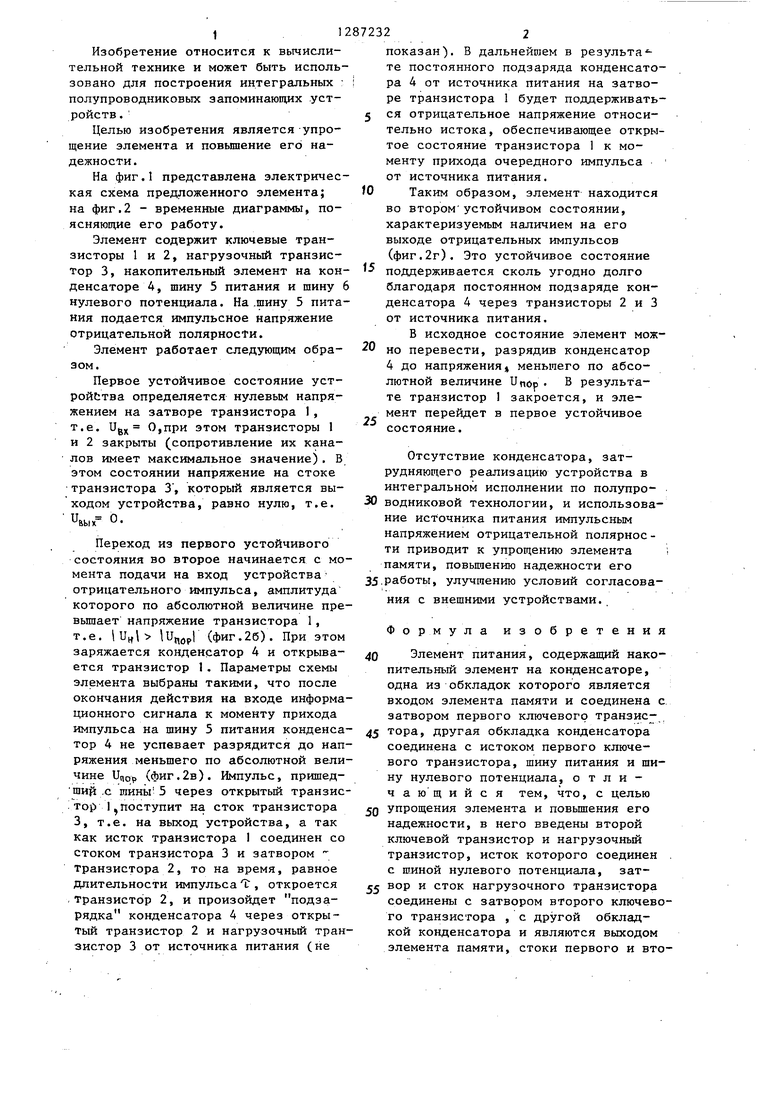

На фиг.1 представлена электрическая схема предложенного элемента; на фиг.2 - временные диаграммы, по- ясняюЕдие его работу.

Элемент содержит ключевые транзисторы 1 и 2, нагрузочный транзистор 3, накопительный элемент на конденсаторе 4, шину 5 питания и шину 6 нулевого потенциала. На .шину 5 питания подается импульсное напряжение отрицательной полярности.

Элемент работает следующим образом.

Первое устойчивое состояние уст- ройЬтва определяется нулевым напряжением на затворе транзистора 1 , т.е. Ugx О,при этом транзисторы 1 и 2 закрыты (сопротивление их каналов имеет максимальное значение). В этом состоянии напряжение на стоке транзистора 3, который является выходом устройства, равно нулю, т.е.

ишк ОПереход из первого устойчивого состояния во второе начинается с момента подачи на вход устройства отрицательного импульса, амплитуда которого по абсолютной величине пре- вьшает напряжение транзистора 1, т.е. I 1и,рГ (фиг.26). При этом заряжается конденсатор 4 и открывается транзистор 1. Параметры схемы элемента выбраны такими, что после окончания действия на входе информационного сигнала к моменту прихода импульса на шину 5 питания конденсатор 4 не успевает разрядится до напряжения меньшего по абсолютной величине Uqqp (фиг.2в). Импульс, пришед- ший .с шины 5 через открытый транзистор Ц поступит на сток транзистора 3, т.е. на выход устройства, а так как исток траизистора I соединен со стоком транзистора 3 и затвором Транзистора 2, то на время, равное длительности импульса t, откроется транзистор 2, и произойдет подзарядка конденсатора 4 через открытый транзистор 2 и нагрузочный транзистор 3 от источника питания (не

показан). В дальнейшем в результа- те постоянного подзаряда конденсатора 4 от источника питания на затворе транзистора 1 будет поддерживаться отрицательное напряжение относительно истока, обеспечивающее открытое состояние транзистора 1 к моменту прихода очередного импульса от источника питания.

Таким образом, элемент находится во втором устойчивом состоянии, характеризуемым наличием на его выходе отрицательных импульсов (фиг.2г). Это устойчивое состояние поддерживается сколь угодно долго благодаря постоянном подзаряде конденсатора 4 через транзисторы 2 и 3 от источника питания.

В исходное состояние элемент можно перевести, разрядив конденсатор 4 до напряжения меньшего по абсо

лютной величине U

те транзистор 1 мент перейдет в состояние.

пор

в результазакроется, и эле- первое устойчивое

Отсутствие конденсатора, затрудняющего реализацию устройства в интегральном исполнении по полупро30 водниковой технологии, и использование источника питания импульсным напряжением отрицательной полярное - ти приводит к упрощению элемента памяти, повьшзению надежности его

35.работы, улучшению условий согласования с внешними устройствами.

Ф о р м ула изобретения

40 Элемент питания, содержащий накопительный элемент на конденсаторе, одна из обкладок которого является входом элемента памяти и соединена с затвором первого ключевого транзис-

45 тора, другая обкладка конденсатора соединена с истоком первого ключевого транзистора, шину питания и шину нулевого потенциала, отличающийся тем, что, с целью

50 упрощения элемента и повьш1ения его надежности, в него введены второй ключевой транзистор и нагрузочный транзистор, исток которого соединен с шиной нулевого потенциала, зат вор и сток нагрузочного транзистора соединены с затвором второго ключевого транзистора , с другой обкладкой конденсатора и являются выходом элемента памяти, стоки первого и второго ключевых транзисторов подключе- чевого транзистора соединен с затво- ны к шине питания, исток второго клю- ром первого ключевого транзистора.

г

Unop

пор.

t fJnop

Составитель А.Воронин Редактор А.Долинич Техред А.Кравчук Корректор М.Демчик

Заказ 7724/56 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород,, ул.Проектная, 4

t

Unop

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамический элемент памяти | 1988 |

|

SU1599898A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Формирователь напряжения смещения подложки для интегральных схем | 1986 |

|

SU1322374A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1987 |

|

SU1453378A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Интегральная ячейка памяти для постоянного запоминающего устройства | 1975 |

|

SU551700A1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения интегральных полупроводниковых запоминающих устройств. Цель изобретения фиг./ упрощение элемента памяти и повышение его степени интеграции - достигается введением второго ключевого транзистора и нагрузочного транзисто- pa. Элемент содержит ключевые транзисторы 1 и 2, нагрузочный транзистор 3, конденсатор 4, шину 5 питания и шику 6 нулевого потенциала. Введение второго ключевого транзистора 2 и нагрузочного транзистора 3 позволи ло упростить предложенный элемент и повысить степень его интеграции За .счет исключения из прототипа второго ковденсатора и образования конденса- ; : тора 4 емкостью между затвором и истоком транзистора 1. 1 ил. 00 ч СО ю

| Патент США № 4112510, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU662972A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-25—Подача