ON 4

4 Ю Ю Ю

Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных схемах памяти на МДП-транзисторах.

Цель изобретений-повышение быстро-, действия дешифратора.

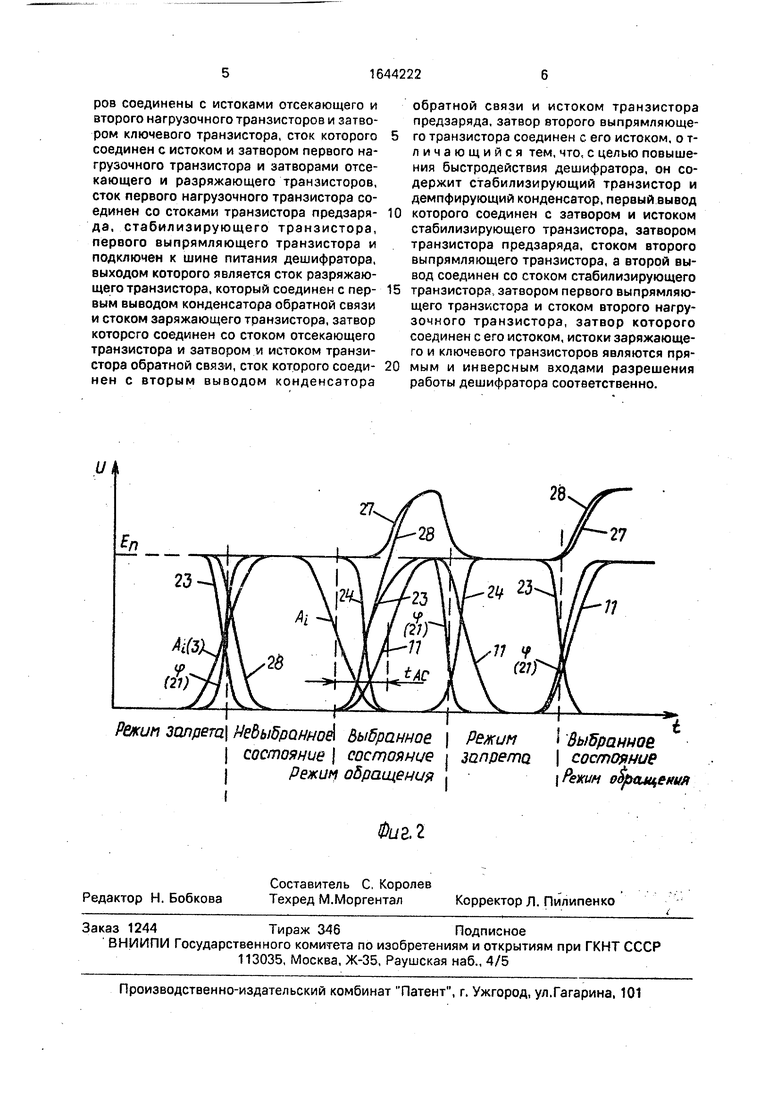

На фиг. 1 представлена принципиальная электрическая схема дешифратора; на фиг. 2 - временные диаграммы его работы.

Дешифратор содержит адресные транзисторы 1, шину 2 нулевого потенциала, адресные входы 3, ключевой транзистор 4, первый нагрузочный транзистор 5, шину 6 питания, отсекающий транзистор 7, транзистор 8 обратной связи, транзистор 9 пред- заряда, разряжающий транзистор 10, выход 11, заряжающий транзистор 12, конденсатор 13 обратной связи, фильтрующий конденсатор 14, вход 15 смещения, первый 16 и второй 17 выпрямляющие транзисторы, второй нагрузочный транзистор 18, стабилизирующий транзистор 19, демпфирующий конденсатор 20, прямой 21 и инверсный 22 входы разрешения работы.

Дешифратор работает следующим образом.

В режиме запрета обращения все сигналы на адресных входах 3 дешифратора и сигнал на входе 21 разрешения работы дешифратора имеют низкий логический уровень, а на входе 22 - высокий. Поэтому все адресные транзисторы 1 закрыты, и в узлах 23 и 24 с помощью нагрузочных транзисторов 18 и 5 установлен высокий логический уровень, равный напряжению питания. Последовательностью периодических импульсов, поступающих через конденсатор 14 и транзистор 17с входа 15, установлен потенциал в узле 25, равный сумме напряжения питания и порогового напряжения МДП- транзистора. Диапазоны изменения потенциалов в узлах 25 и 26 ограничены транзисторами 16. 17 и 19. Конденсатор 20 служит для сглаживания пульсаций в узле 25. В узлах 27 и 28 при этом через открытые транзисторы 9 и 8 устанавливаются потенциалы, равные напряжению питания. Транзистор 10 открыт и на выходе 11 дешифратора установлен потенциал до низкого логического уровня О.

Таким образом, конденсатор 13 в режиме запрета обращения заряжен до уровня питания. В режиме обращения на прямой вход 21 разрешения работы поступает сигнал высокого логического уровня, а инверсный вход 22 - 0й.

При переключении дешифратора из режима запрета в невыбранное состояние хотя бы один из адресных сигналов на входах 3 переключается в высокое логическое состояние, что приводит к понижению до логического нуля потенциала в узле 23. Транзистор 4 при этом закрывается, транзистор

10 остается открытым, потенциал на выходе 11 дешифратора не имзеняется, остается низким, а транзистор 7 понижает потенциал в узле 28 и закрывает заряжающий транзистор 12.

При переключении дешифратора из режима запрета в выбранное состояние все адресные сигналы остаются в низком логическом состоянии, потенциал в узле 23 остается высоким. Переключение сигнала на

входе 22 в низкое логическое состояние понижает потенциал в узле 24, транзисторы 7 и 10 закрываются. Одновременно происходит переключение сигнала на входе 21 в высокое логическое состояние, что приводит к повышению потенциала на выходе 11 дешифратора через открытый транзистор 12. Для ускорения повышения потенциала на выходе 11 дешифратора служат транзистор 8 и конденсатор 13 обратной связи за

счет бутстрепного эффекта: повышение потенциала на выходе 11 через конденсатор ,13 и транзистор 8 перезаряжается на затвор транзистора 12.

При переключении дешифратора из невыбранного состояния в выбранное все сигналы нз входах 3 дешифратора переключаются в низкое логическое состояние. Нагрузочный транзистор 18 повышает потенциал в узле 23, открывает ключевой

транзистор 4, который закрывает отсекающий 7 и разряжающий 10 транзисторы. Конденсатор 13 и транзистор 8 обратной связи за счет бутстрепного эффекта ускоряют повышение потенциала в узле 28, заряжающий транзистор 12 открывается и устанавливает на выходе 11 дешифратора высокий логический уровень.

Формула изобретения Дешифратор, содержащий адресные транзисторы, ключевой транзистор, два нагрузочных транзистора, отсекающий транзистор, транзистор обратной связи, транзистор предзаряда, разряжающий транзистор, заряжающий транзистор, конденсатор обратной связи, фильтрующий конденсатор, два выпрямляющих транзистора, истоки которых соединены с первым выводом фильтрующего конденсатора, второй вывод которого является входом смещения дешифратора, адресными входами которого являются затворы адресных транзисторов, истоки которых соединены с истоком разряжающего транзистора и подключены к шине нулевого потенциала дешифратора, стоки адресных транзисторов соединены с истоками отсекающего и второго нагрузочного транзисторов и затвором ключевого транзистора, сток которого соединен с истоком и затвором первого нагрузочного транзистора и затворами отсекающего и разряжающего транзисторов, сток первого нагрузочного транзистора соединен со стоками транзистора предзаря- да, стабилизирующего транзистора, первого выпрямляющего транзистора и подключен к шине питания дешифратора, выходом которого является сток разряжающего транзистора, который соединен с пер- вым выводом конденсатора обратной связи и стоком заряжающего транзистора, затвор которого соединен со стоком отсекающего транзистора и затвором и истоком транзистора обратной связи, сток которого соеди- нен с вторым выводом конденсатора

обратной связи и истоком транзистора предзаряда, затвор второго выпрямляющего транзистора соединен с его истоком, о т- личающийся тем, что, с целью повышения быстродействия дешифратора, он содержит стабилизирующий транзистор и демпфирующий конденсатор, первый вывод которого соединен с затвором и истоком стабилизирующего транзистора, затвором транзистора предзаряда, стоком второго выпрямляющего транзистора, а второй вывод соединен со стоком стабилизирующего транзистора затвором первого выпрямляющего транзистора и стоком второго нагрузочного транзистора, затвор которого соединен с его истоком, истоки заряжающего и ключевого транзисторов являются прямым и инверсным входами разрешения работы дешифратора соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Формирователь импульсов | 1985 |

|

SU1374416A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Устройство для записи информации в блоки памяти с произвольной выборкой | 1984 |

|

SU1156136A1 |

Изобретение относится к цифровой вычислительной технике, в частности к интегральным схемам памяти на МДПтранэисторах. Цель изобретения - повышение быстродействия дешифратора. Поставленная цель достигается тем, что дешифратор содержит стабилизирующий транзистор 19 и демпфирующий конденсатор 20 с соответствующими связями. Перечисленные элементы сглаживают пульсации, возникающие вследствие поступления на вход 15 периодических импульсов. Это позволяет заряжать конденсатор 13 обратной связи до более высокого напряжения. В результате за счет бутстреп- ного эффекта ускоряется формирование сигнала на выходе 11 дешифратора. 2 ил.

tgfy forn n F

Р&кип запрета} №Ьы5ранно& Выбранное

состояние состояние

Рехин обращения

Режим

запрета

« Выбранное состояние

Рехин оврлщемия

| IEEE Journal of Solid State Circuits, 1983, v.SC-l8, № 5, p | |||

| Льномолотилка веялка | 1923 |

|

SU498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| IEEE Journal of Solid State Circuits, 1981 | |||

| v | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Способ получения твердых неплавких и нерастворимых продуктов уплотнения формальдегида с фонолами | 1925 |

|

SU435A1 |

| des | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-04-23—Публикация

1989-03-24—Подача