Изобретение относится к электронике и может быть использовано в БИС на МДП- транзисторах.

Цель изобретения - повышение нагрузочной способности формирователя напряжения смещения подложки.

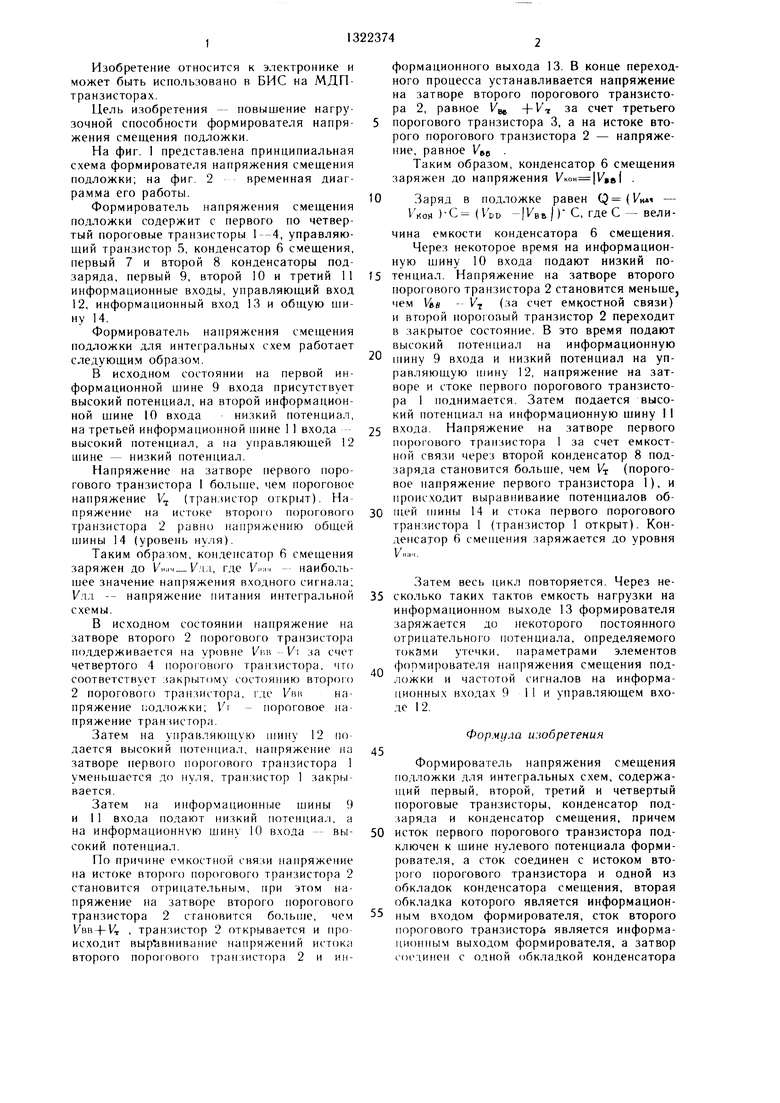

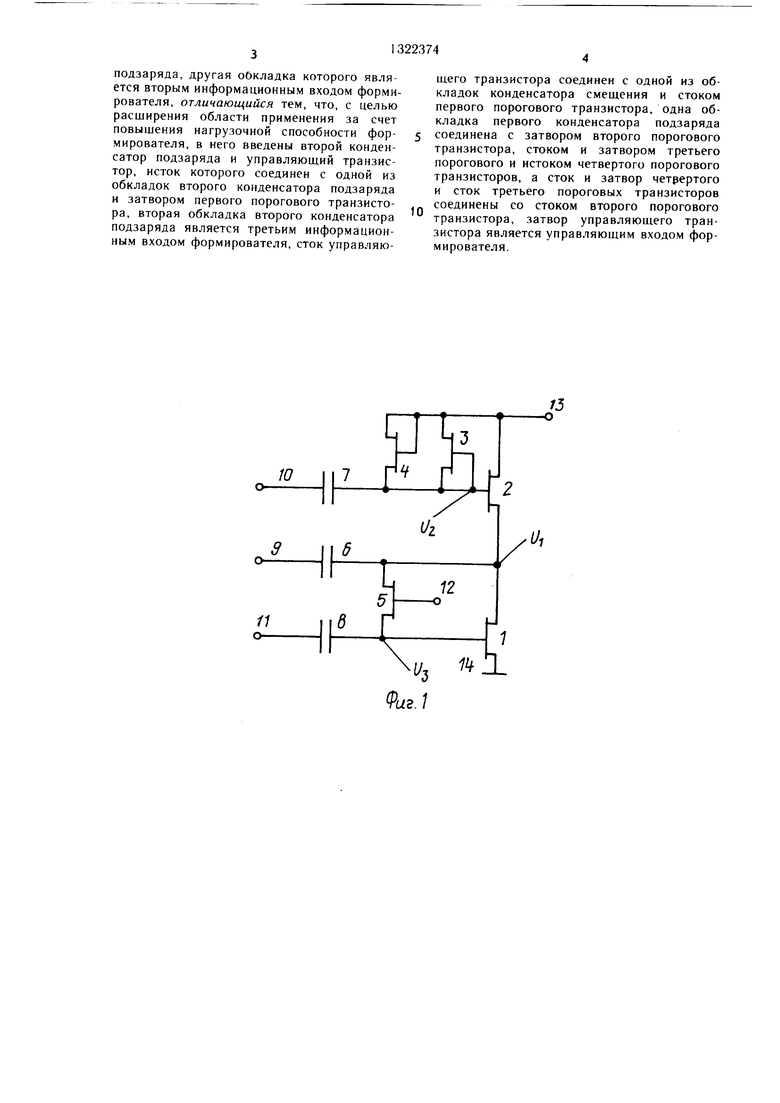

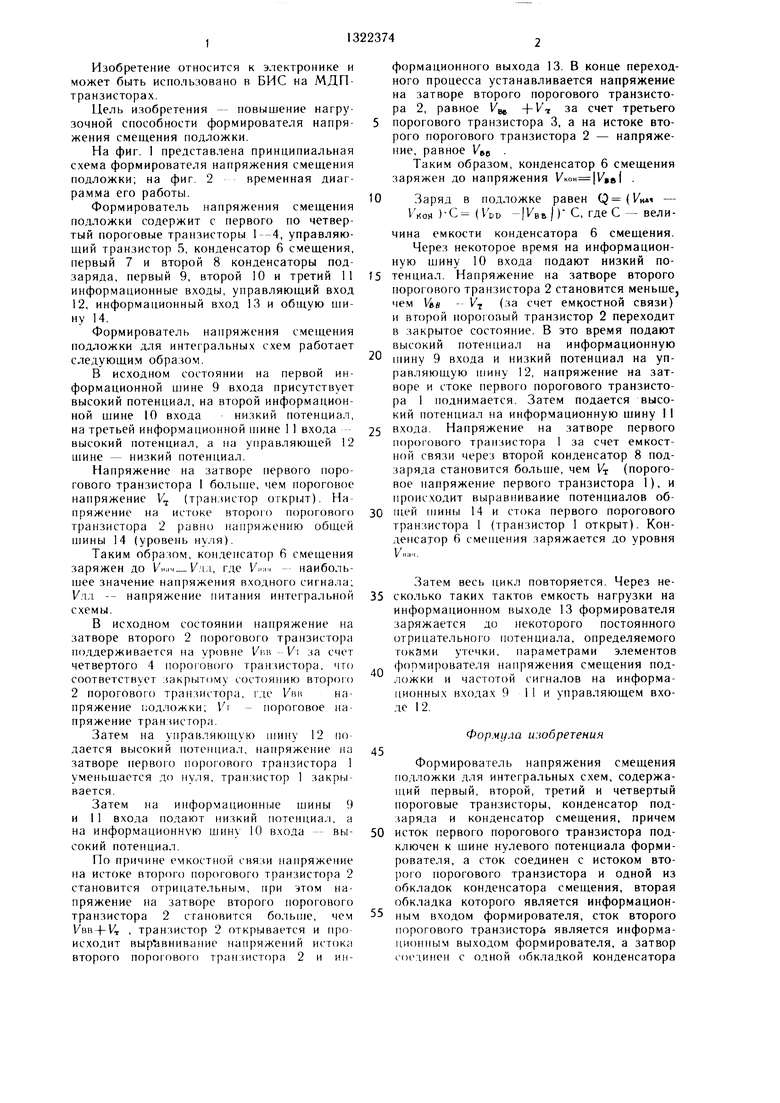

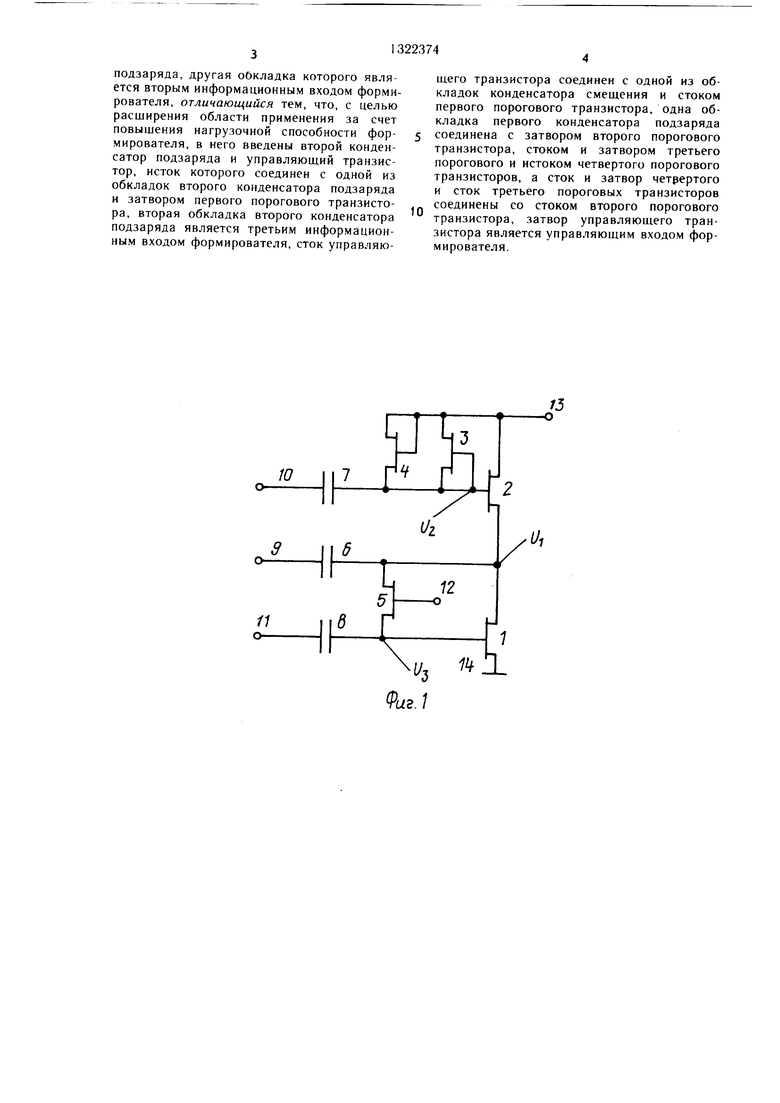

На фиг. 1 представлена принципиальная схема формирователя напряжения смещения подложки; на фиг. 2временная диаграмма его работы.

Формирователь напряжения смещения подложки содержит с первого по четвертый пороговые транзисторы 1-4, управляющий транзистор 5, конденсатор 6 смещения, первый 7 и второй 8 конденсаторы под- заряда, первый 9, второй 10 и третий 11 информационные входы, управляющий вход 12, информационный вход 13 и общую шину 14.

Формирователь напряжения смещения подложки для интегральных схем работает следующим образом.

В исходном состоянии на первой информационной шине 9 входа присутствует высокий потенциал, на второй информационной шине 10 входанизкий потенциал, на третьей информационной шине 1 1 входа - высокий потенциал, а на управляющей 12 щине - низкий потенциал.

Напряжение на затворе первого порогового транзистора I больше, чем пороговое напряжение V , (транзистор открыт). Напряжение на истоке второго порогового транзистора 2 равно напряжению общей шины 14 (уровень нуля).

Таким образом, конде 1сатор 6 смещения заряжен до VH-..:i, где VHMH - наибольшее значение напряжения входного сигнала; Улл -- напряжение питания интегральной схемы.

В исходном состоянии напряжение на затворе второго 2 порогового тра)1зистора поддерживается на уровне Kiui l/i за счет четвертого 4 порогового транзистора, что соответствует закрытому состоянию второго 2 порогового транзистора, где KtiRнапряжение подложки; V i - пороговое па- пряжение транзистора.

Затем на управляющую шину 12 подается высокий потенциал, напряжение на затворе первого порогового транзистора 1 уменьшается до нуля, транзистор 1 закрывается.

Затем на информационные шины 9 и 11 входа подают низкий потенциал, а на информационную шину 10 входа - высокий потенциал.

По причине емкостной связи напряжение па истоке второго порогового транзистора 2 становится отрицательным, при этом напряжение на затворе второго порогового транзистора 2 становится бо.чыне, чем l/BH-j-V, , транзистор 2 открывается и происходит выравнивание напряжений истока второго порогового транзистора 2 и информационного выхода 13. В конце переходного процесса устанавливается напряжение на затворе второго порогового транзистора 2, равное Квв +V-t за счет третьего порогового транзистора 3, а на истоке второго порогового транзистора 2 - напряжение, равное Vee .

Таким образом, конденсатор 6 смещения заряжен до напряжения 1/кон |У,в1 .

0 Заряд в подложке равен Q(Viwt - )-С (VoD ) С, где С - величина емкости конденсатора 6 смещения. Через некоторое время на информационную шину 10 входа подают низкий по5 тенциал. Напряжение на затворе второго порогового транзистора 2 становится меньше, чем Ves - V T (за счет емкостной связи) и второй пороговый транзистор 2 переходит в закрытое состояние. В это время подают высокий потенциал на информационную

0 П1ину 9 входа и низкий потенциал на управляющую 12, напряжение на затворе и стоке первого порогового транзистора 1 поднимается. Затем подается высокий потенциал на информационную щину 11

5 входа. Напряжение на затворе первого nopoi OBoro транзистора 1 за счет емкостной связи через второй конденсатор 8 под- заряда становится больше, чем VT (пороговое напряжение первого транзистора 1), и происходит выравнивание потенциалов об0 щей шины 14 и стока первого порогового транзистора 1 (транзистор 1 открыт). Конденсатор 6 смещения заряжается до уровня V

Затем весь цикл повторяется. Через не- 5 сколько таких тактов емкость нагрузки на информационном выходе 13 формирователя заряжается до некоторого постоянного отрицательного потенциала, определяемого токами утечки, параметрами элементов формирователя напряжения смещения подложки и частотой сигналов на информационных входах 9 1 1 и управляющем входе 12.

Формула изобретения

Формирователь напряжения смещения подложки для интегральных схем, содержащий первый, второй, третий и четвертый пороговые транзисторы, конденсатор под- заряда и конденсатор смещения, причем

исток первого порогового транзистора подключен к шине нулевого потенциала формирователя, а сток соединен с истоком второго порогового транзистора и одной из обкладок конденсатора смещения, вторая обкладка которого является информационцым входом формирователя, сток второго порогового транзистора является информационным выходом формирователя, а затвор гоелипен с одной обкладкой конденсатора

подзаряда, другая обкладка которого является вторым информационным входом формирователя, отличающийся тем, что, с целью расширения области применения за счет повышения нагрузочной способности формирователя, в него введены второй конденсатор подзаряда и управляющий транзистор, исток которого соединен с одной из обкладок второго конденсатора подзаряда и затвором первого порогового транзистора, вторая обкладка второго конденсатора подзаряда является третьим информационным входом формирователя, сток управляю

щего транзистора соединен с одной из обкладок конденсатора смещения и стоком первого порогового транзистора, одна обкладка первого конденсатора подзаряда соединена с затвором второго порогового транзистора, стоком и затвором третьего порогового и истоком четвертого порогового транзисторов, а сток и затвор четрертого и сток третьего пороговых транзисторов соединены со стоком второго порогового транзистора, затвор управляющего транзистора является управляющим входом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигнала напряжения смещения подложки для интегральных схем | 1983 |

|

SU1149311A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Формировтель напряжения смещения подложки для интегральных схем | 1983 |

|

SU1185396A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Дешифратор для запоминающего устройства | 1981 |

|

SU980160A1 |

Изобретение относится к области электроники и может быть использовано в БИС на МДП-транзисторах. Цель изобретения - повышение нагрузочной способности формирователя напряжения смешения подложки для интегральных схем. Поставленная цель достигается тем, что в формирователь напряжения смещения подложки для интегральных схем, содержащий первый, второй, третий и четвертый пороговые транзисторы, конденсатор подзаряда и смещения, первую и вторую информационные щины входа, информационный выход, введены управляющий транзистор, второй конденсатор подзаряда, третий информационный вход и управляющий выход. Повышение нагрузочной способности обеспечивается за счет повышения напряжения перезаряда конденсатора смещения на величину порогового напряжения первого порогового транзистора, что, в свою очередь, обусловлено повышением напряжения на затворе первого порогового транзистора до величины, превышающей пороговое напряжение первого порогового транзистора при заряде емкости смещения. 2 ил. а со N5 o со 4

10

1i w

7

::

fe.2

j/fi6 -t

lJuB i

/

Use

| Электроника, 1977, № 16, с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Формировтель напряжения смещения подложки для интегральных схем | 1983 |

|

SU1185396A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-12—Подача