Изобретение относится к вычислительной технике, в частности к динамическим элементам памяти, и может быть использовано для построения интегральных полупроводниковых буферных устройств динамического типа для запоминания цифровой информации.

Цель изобретения - увеличение времени хранения информации.

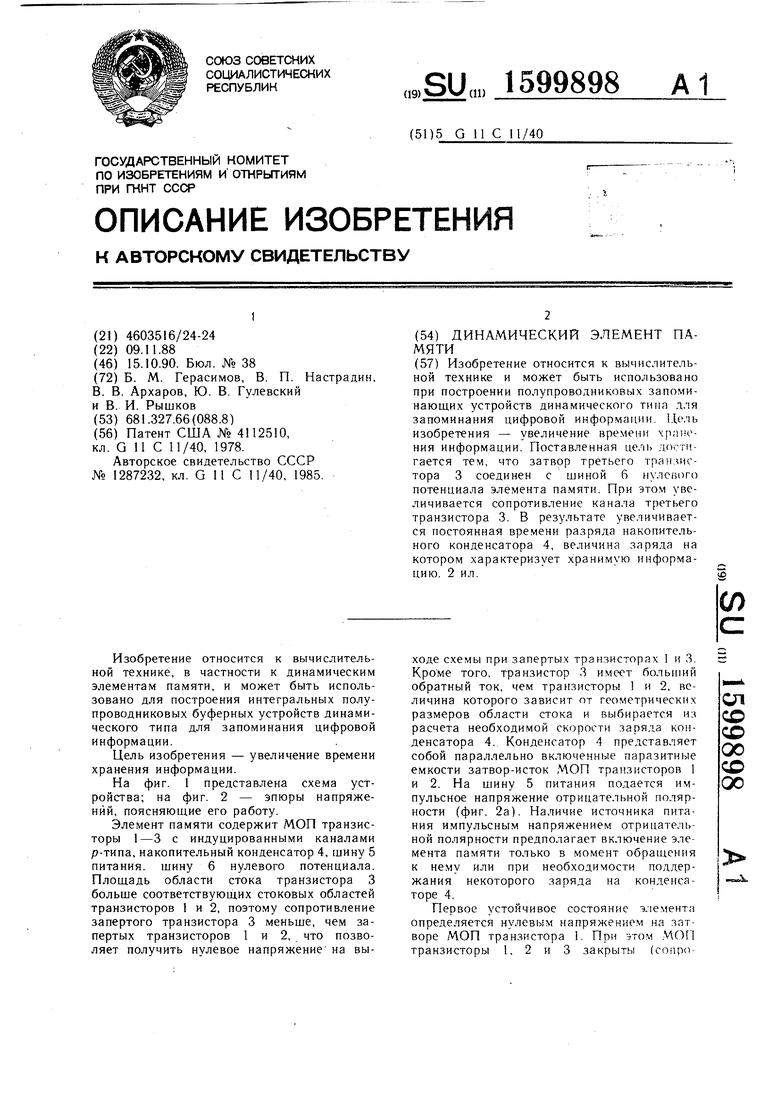

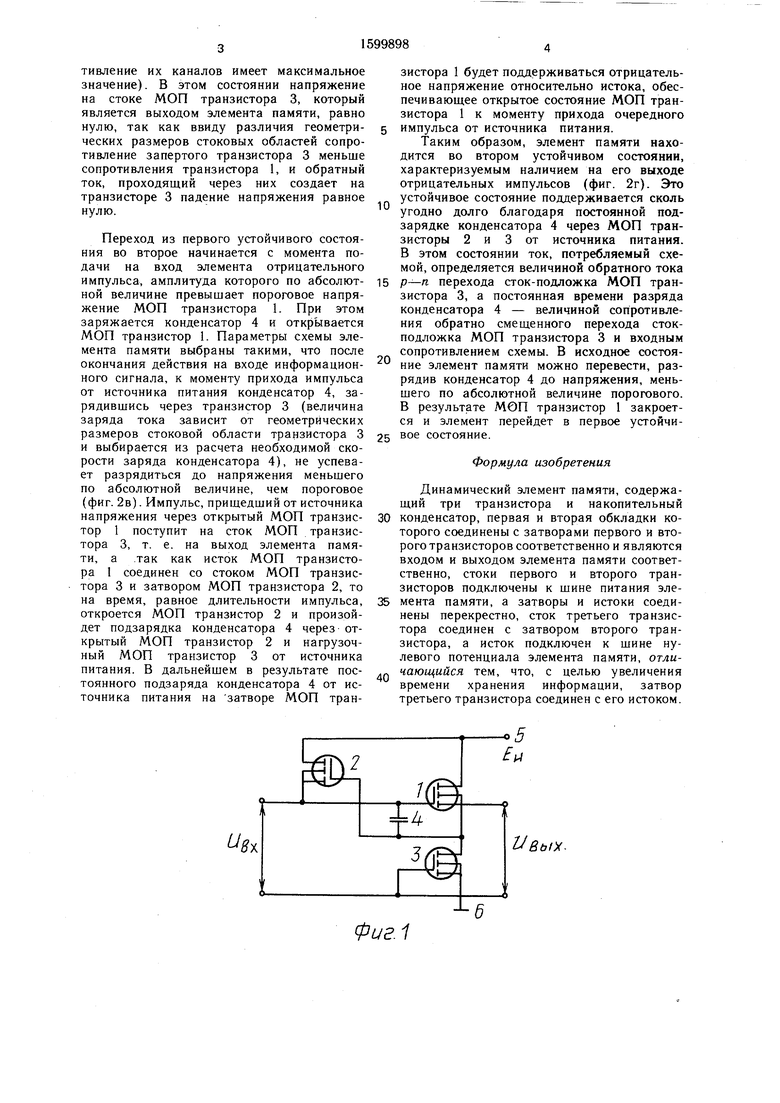

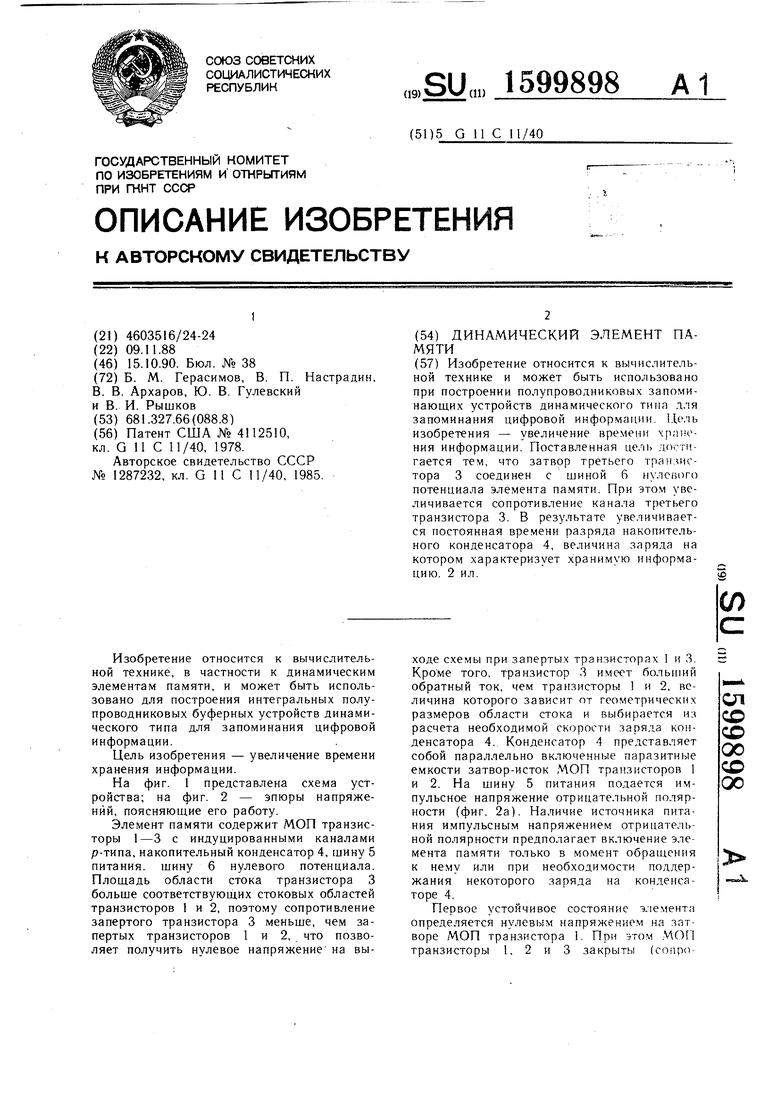

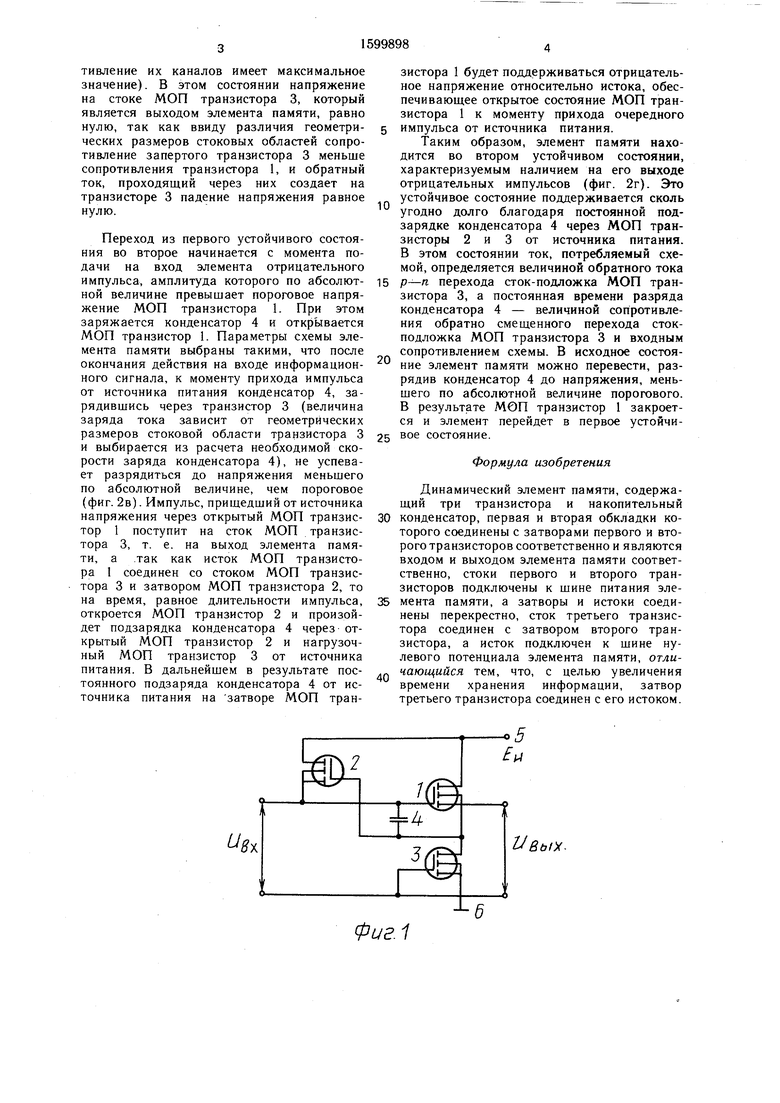

На фиг. 1 представлена схема устройства; на фиг. 2 - эпюры напряжений, поясняющие его работу.

Элемент памяти содержит МОП транзисторы 1-3 с индуцированными каналами р-типа, накопительный конденсатор 4, шину 5 питания, шину 6 нулевого потенциала. Площадь области стока транзистора 3 больше соответствующих стоковых областей транзисторов 1 и 2, поэтому сопротивление запертого транзистора 3 меньше, чем запертых транзисторов 1 и 2, что позволяет получить нулевое напряжение на выходе схемы при запертых транзисторах I и 3. Кроме того, транзистор 3 имеет больший обратный ток, чем транзисторы 1 и 2. величина которого зависит от геометрических размеров области стока и выбирается из расчета необходимой скорости заряда конденсатора 4. Конденсатор 4 представляет собой параллельно включенные паразитные емкости затвор-исток МОП транзисторов 1 и 2. На шину 5 питания подается импульсное напряжение отрицательной полярности (фиг. 2а). Наличие источника питания импульсным напряжением отрицательной полярности предполагает включение элемента памяти только в момент обращения к нему или при необходимости поддержания некоторого заряда на конденсаторе 4.

Первое устойчивое состояние элемента определяется нулевым напряжением на затворе МОП транзистора 1. При этом транзисторы 1, 2 и 3 закрыты (сопросд со со

00

со

00

..«.х

тивление их каналов имеет максимальное значение). В этом состоянии напряжение на стоке МОП транзистора 3, который является выходом элемента памяти, равно нулю, так как ввиду различия геометрических размеров стоковых областей сопротивление запертого транзистора 3 меньше сопротивления транзистора 1, и обратный ток, проходящий через них создает на транзисторе 3 падение напряжения равное нулю.

Переход из первого устойчивого состояния во второе начинается с момента подачи на вход элемента отрицательного импульса, амплитуда которого по абсолютной величине превышает пороговое напряжение МОП транзистора 1. При этом заряжается конденсатор 4 и открывается МОП транзистор 1. Параметры схемы элемента памяти выбраны такими, что после окончания действия на входе информационного сигнала, к моменту прихода импульса от источника питания конденсатор 4, зарядившись через транзистор 3 (величина заряда тока зависит от геометрических размеров стоковой области транзистора 3 и выбирается из расчета необходимой скорости заряда конденсатора 4), не успевает разрядиться до напряжения меньшего по абсолютной величине, чем пороговое (фиг. 2в). Импульс, пришедший от источника напряжения через открытый МОП транзистор 1 поступит на сток МОП транзистора 3, т. е. на выход элемента памяти, а .так как исток МОП транзистора 1 соединен со стоком МОП транзистора 3 и затвором МОП транзистора 2, то на время, равное длительности импульса, откроется МОП транзистор 2 и произойдет подзарядка конденсатора 4 через открытый МОП транзистор 2 и нагрузочный МОП транзистор 3 от источника питания. В дальнейшем в результате постоянного подзаряда конденсатора 4 от источника питания на затворе МОП тран

зистора 1 будет поддерживаться отрицательное напряжение относительно истока, обеспечивающее открытое состояние МОП транзистора 1 к моменту прихода очередного

импульса от источника питания.

Таким образом, элемент памяти находится во втором устойчивом состоянии, характеризуемым наличием на его выходе отрицательных импульсов (фиг. 2г). Это устойчивое состояние поддерживается сколь угодно долго благодаря постоянной подзарядке конденсатора 4 через МОП транзисторы 2 и 3 от источника питания. В этом состоянии ток, потребляемый схемой, определяется величиной обратного тока

р-п перехода сток-подложка МОП транзистора 3, а постоянная времени разряда конденсатора 4 - величиной сопротивления обратно смещенного перехода сток- подложка МОП транзистора 3 и входным сопротивлением схемы. В исходное состояние элемент памяти можно перевести, разрядив конденсатор 4 до напряжения, меньшего по абсолютной величине порогового. В результате МОП транзистор 1 закроется и элемент перейдет в первое устойчивое состояние.

Формула изобретения

Динамический элемент памяти, содержащий три транзистора и накопительный

конденсатор, первая и вторая обкладки которого соединены с затворами первого и второго транзисторов соответственно и являются входом и выходом элемента памяти соответственно, стоки первого и второго транзисторов подключены к шине питания элемента памяти, а затворы и истоки соединены перекрестно, сток третьего транзистора соединен с затвором второго транзистора, а исток подключен к шине нулевого потенциала элемента памяти, отличающийся тем, что, с целью увеличения времени хранения информации, затвор третьего транзистора соединен с его истоком.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одновибратор | 1978 |

|

SU748810A1 |

| ПОЛУПРОВОДНИКОВОЕ КЛЮЧЕВОЕ УСТРОЙСТВО С ПОЛЕВЫМ УПРАВЛЕНИЕМ | 2001 |

|

RU2199795C2 |

| Постоянное запоминающее устройство | 1973 |

|

SU444246A1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1985 |

|

SU1345165A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| ПОЛУПРОВОДНИКОВОЕ КЛЮЧЕВОЕ УСТРОЙСТВО | 2003 |

|

RU2268545C2 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Ячейка памяти на основе комплементарных МОП-транзисторов | 1989 |

|

SU1640738A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении полупроводниковых запоминающих устройств динамического типа для запоминания цифровой информации. Цель изобретения - увеличение времени хранения информации. Это достигается тем, что затвор третьего транзистора 3 соединен с шиной 6 нулевого потенциала элемента памяти. При этом увеличивается сопротивление канала третьего транзистора 3. В результате увеличивается постоянная времени разряда накопительного конденсатора 4, величина заряда на котором характеризует хранимую информацию. 2 ил.

Фиг.1

УС

У пор

Ипор

Упор

иг.г

| Патент США № 4112510, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Элемент памяти | 1985 |

|

SU1287232A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-10-15—Публикация

1988-11-09—Подача