25

Изобретение относится к радиотех- нике, в частности к цифровым фазовым искриминаторам.

Цель изобретения - повышение точности измерения за счет повьпиения 5 остоверности обнаружения слабых игналов с определенным фазовым сдвигом-,

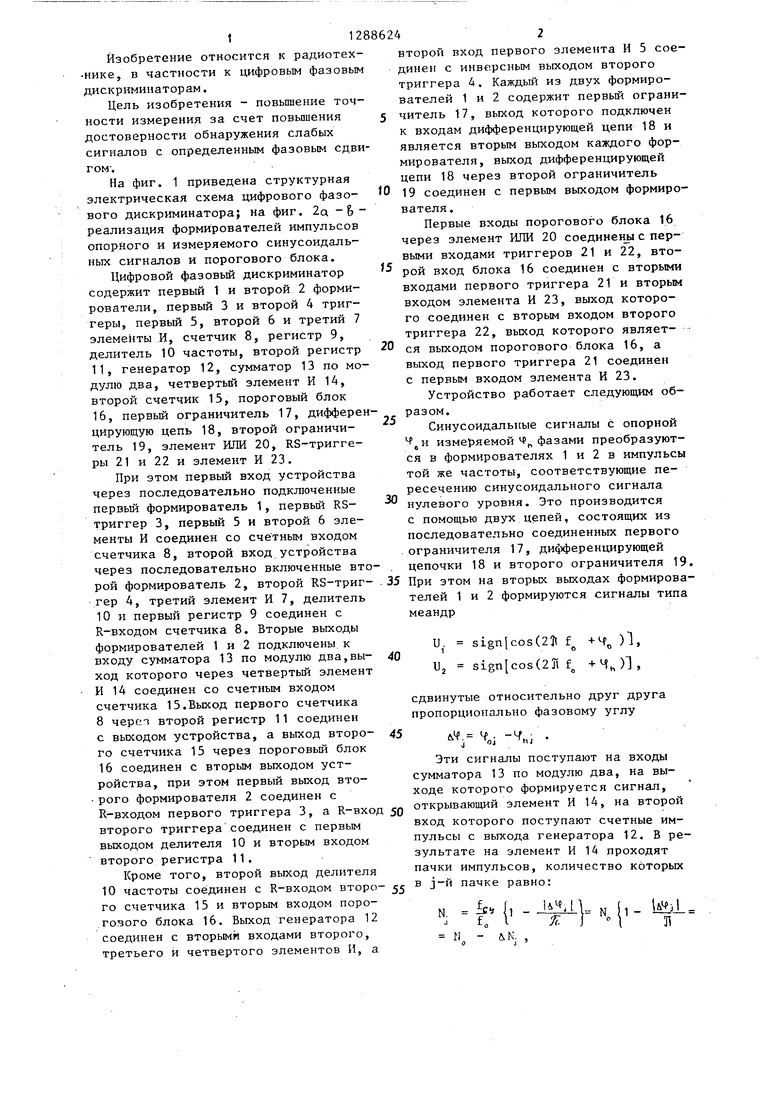

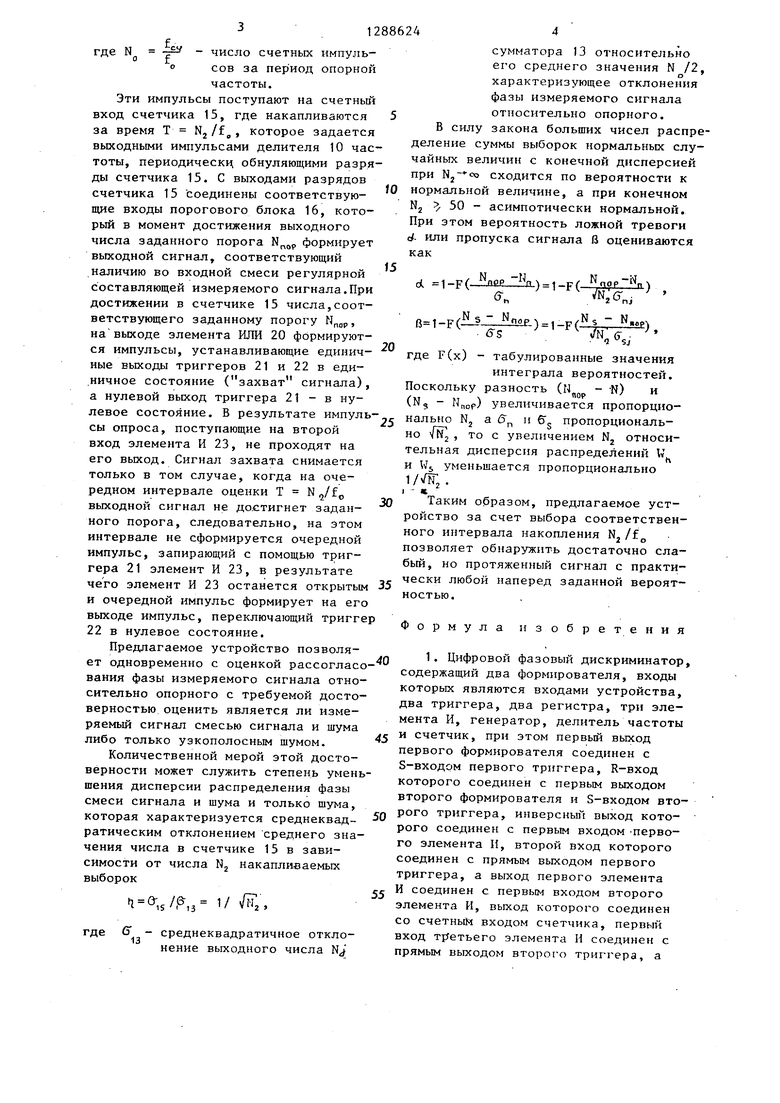

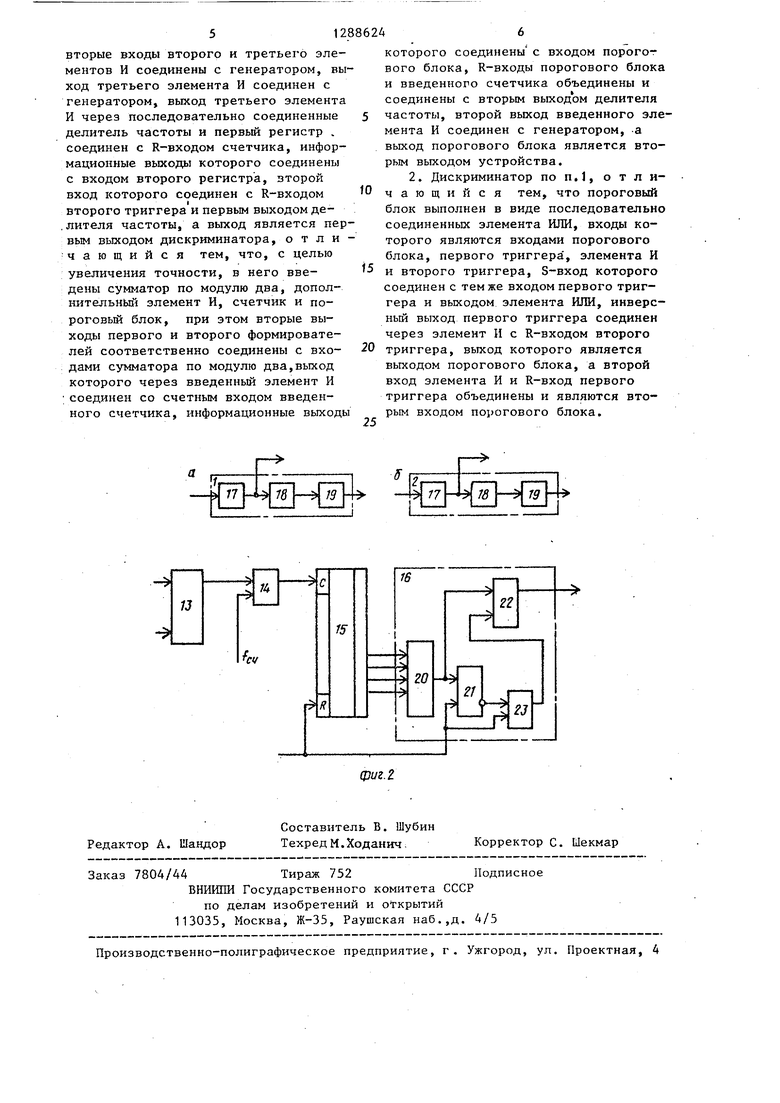

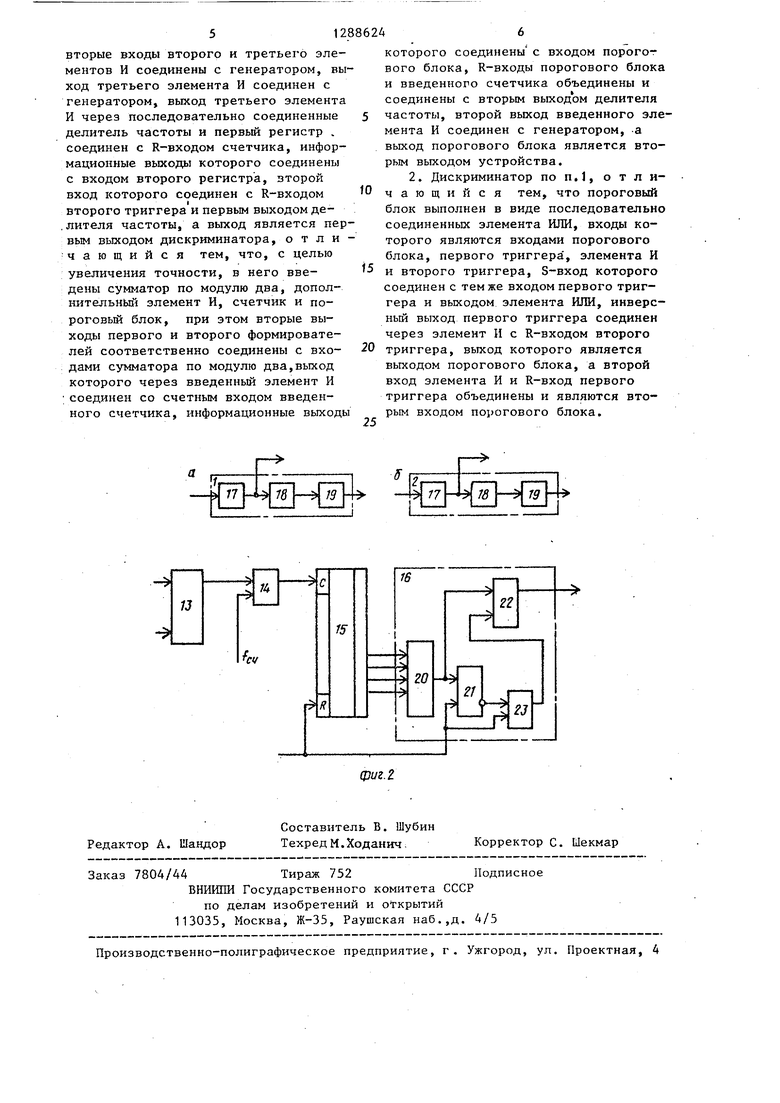

На фиг. 1 приведена структурная электрическая схема цифрового фазо- О ого дискриминатора; на фиг. 2с1 - Ь- реализация формирователей импульсов опорного и измеряемого синусоидальных сигналов и порогового блока.

Цифровой фазовый дискриминатор содержит первый 1 и второй 2 формиователи, первый 3 и второй 4 триггеры, первый 5, второй 6 и третий 7 элементы И, счетчик 8, регистр 9, елитель 10 частоты, второй регистр 0 11, генератор 12, сумматор 13 по модулю два, четвертьш элемент И 14, второй счетчик 15, пороговый блок 16, первый ограничитель 17, дифференцирующую цепь 18, второй ограничитель 19, элемент ИЛИ 20, RS-тригге- ры 21 и 22 и элемент И 23.

Цри этом первый вход устройства через последовательно подключенные первый формирователь 1, первый RS- триггер 3, первый 5 и второй 6 элементы И соединён со сче тным входом счетчика 8, второй вход устройства через последовательно включенные второй формирователь 2, второй RS-триг- . 35 гер 4, третий элемент И 7, делитель 10 и первый регистр 9 соединен с R-входом счетчика 8, Вторые выходы формирователей 1 и 2 подключены к входу сумматора 13 по модулю два,вы- 40 од которого через четвертый элемент 14 соединен со счетным входом счетчика 15.Выход первого счетчика 8 через второй регистр 11 соединен с выходом устройства, а выход второ- 45 го счетчика 15 через пороговьш блок 16 соединен с вторьм выходом устройства, при этом первый выход вто- рого формирователя 2 соединен с R-входом первого триггера 3, а К-вход 50 второго триггера соединен с первым вькодом делителя 10 и вторым входом второго регистра 11.

Кроме того, второй выход делителя 10 частоты соединен с R-входом второ- 55 го счетчика 15 и вторым входом порогового блока 16. Выход генератора 12 соединен с вторыми входами второго, третьего и четвертого элементов И, а

5

5

О

0

5 0 5 0

5

второй вход первого элемента И 5 соединен с инв€ ,рсным вьсходом второго триггера 4. Каждый из двух формирователей 1 и 2 содержит первьА ограничитель 17, выход которого подключен к входам дифференцирующей цепи 18 и является вторым выходом каждого формирователя, выход дифференцирующей цепи 18 через второй ограничитель 19 соединен с первым выходом формирователя.

Первые входы порогового блока 16 через элемент ИЛИ 20 соединены с первыми входами триггеров 21 и 22, второй вход блока 16 соединен с вторыми входами первого триггера 21 и вторым входом элемента И 23, выход которого соединен с вторым входом второго триггера 22, выход которого является выходом порогового блока 16, а выход первого триггера 21 соединен с первым входом элемента И 23.

Устройство работает следующим образом.

Синусоидальные сигналы с опорной и измеряемой Ч фазами преобразуются в формирователях 1 и 2 в импульсы той же частоты, соответствующие пересечению синусоидального сигнала нулевого уровня. Это производится с помощью двух цепей, состоящих из последовательно соединенных первого ограничителя 17, ди41ференцирующей цепочки 18 и второго ограничителя 19. Цри этом на вторых выходах формирователей 1 и 2 формируются сигналы типа меандр

и, sign|cos(27l f -ьЧ„ )1, Uj (2ri f +Ч Л ,

сдвинутые относительно друг друга пропорционально фазовому углу

V o - -Эти сигналы поступают на входы сумматора 13 по модулю два, на выходе которого формируется сигнал, открывающий элемент И 14, на второй вход которого поступают счетные импульсы с выхода генератора 12. В результате на элемент И 14 проходят пачки импульсов, количество которых в пачке равно:

1с.

l - I J

fsK.

)М - т -

где N - - число счетных нмпуль- о сов за период опорной

частоты.

Эти импульсы поступают на счетньй вход счетчика 15, где накапливаются за время Т N2/f„, которое задается выходными импульсами делителя 10 частоты, периодически обнуляющими разряды счетчика 15. С выходами разрядов счетчика 15 соединены соответствующие входы порогового блока 16, который в момент достижения выходного числа заданного порога формирует выходной сигнал, соответствующий наличию во входной смеси регулярной составляющей измеряемого сигнала.При достижении в счетчике 15 числа,соответствующего заданному порогу ,

на выходе элемента ИЛИ 20 формируют

ся импульсы, устанавливающие единич-

ные выходы триггеров 21 и 22 в еди- .ничное состояние (захват сигнала), а нулевой выход триггера 21 - в нулевое состояние. В результате импульсы опроса, поступающие на второй вход элемента И 23, не проходят на его выход. Сигнал захвата снимается только в том случае, когда на очередном интервале оценки Т N /f выходной сигнал не достигнет заданного порога, следовательно, на этом интервале не сформируется очередной импульс, запирающий с помощью триггера 21 элемент И 23, в результате чего элемент И 23 останется открытым и очередной импульс формирует на его выходе импульс, переключающий тригге 22 в нулевое состояние.

Предлагаемое устройство позволяет одновременно с оценкой рассогласо вания фазы измеряемого сигнала относительно опорного с требуемой достоверностью оценить является ли измеряемый сигнал смесью сигнала и шума либо только узкополосным шумом.

Количественной мерой этой достоверности может служить степень уменьшения дисперсии распределения фазы смеси сигнала и шума и только шума, которая характеризуется среднеквад- ратическим отклонением среднего значения числа в счетчике 15 в зависимости от числа Nj накапливаемьк выборок

,sA ,3 1/ 2

где б - среднеквадратичное отклонение выходного числа NJ

л

10

15

25

5 20

35

-

30

40

сумматора 13 относительно его среднего значения N /2, характеризующее отклонения фазы измеряемого сигнала относительно опорного. В силу закона больших чисел распределение суммы выборок нормальньос случайных величин с конечной дисперсией при сходится по вероятности к нормальной величине, а при конечном N2 50 - асимпотически нормальной. При этом вероятность ложной тревоги с/, или пропуска сигнала В оцениваются как

oL i-F( ПРР .n) i-F( )

((JJ-g.- P-) i-F( ) ,

где F(x) - табулированные значения интеграла вероятностей. Поскольку разность (N - -N) и (N, - Nnop) увеличивается пропорционально N, а , и 6. пропорциональ1f о

но 5 то с увеличением N относительная дисперсия распределений U

f

и Wj уменьшается пропорционально

.

I - «

Таким образом, предлагаемое устройство за счет выбора соответственного интервала накопления позволяет обнаружить достаточно слабый, но протяженный сигнал с практически любой наперед заданной вероятностью.

Формула изобретения

1. Цифровой фазовый дискриминатор, содержащий два формирователя, входы которых являются входами устройства, два триггера, два регистра, три элемента И, генератор, делитель частоты и счетчик, при этом первый выход первого формирователя соединен с S-входом первого триггера, R-вход которого соединен с первым выходом второго формирователя и S-входом второго триггера, инверсный выход которого соединен с первым входом -первого элемента И, второй вход которого соединен с прямым выходом первого триггера, а выход первого элемента И соединен с первым входом второго элемента И, выход которого соединен со счетный входом счетчика, первый вход трУетьего элемента Н соединен с прямым выходом второго триггера, а

вторые входы второго и третьего элементов И соединены с генератором, выход третьего элемента И соединен с генератором, выход третьего элемента И через последовательно соединенные делитель частоты и первый регистр , соединен с R-входом счетчика, информационные выходы которого соединены с входом второго регистра, второй вход которого соединен с R-входом второго триггера и первым выходом де- .лителя частоты, а выход является первым выходом дискриминатора, отличающийся тем, что, с целью

увеличения точности, в него введены сумматор по модулю два, дополнительный элемент И, счетчик и пороговый блок, при этом вторые выходы первого и второго формирователей соответственно соединены с входами сумматора по модулю два,выход которого через введенный элемент И ; соединен со счетным входом введенного счетчика, информационные выходы

7

-1

rr -if78 - fJi

Редактор А. Шандор

Составитель В. Шубин Техред М. Ходанич.

Заказ 7804/44Тираж 752Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

которого соединены с входом порогог вого блока, R-входы порогового блока и введенного счетчика объединены и соединены с вторым выход ом делителя частоты, второй выход введенного элемента И соединен с генератором, а выход порогового блока является вторым выходом устройства.

2. Дискриминатор по п., отличающийся тем, что пороговый блок выполнен в виде последовательно соединенных элемента ИЛИ, входы которого являются входами порогового блока, первого триггера , элемента И и второго триггера, S-вход которого соединен с тем же входом первого триггера и вькодом элемента ИЛИ, инверсный выход первого триггера соединен через элемент И с R-входом второго триггера, выход которого является выходом порогового блока, а второй вход элемента И и R-вход первого триггера объединены и являются вторым входом порогового блока.

1

Корректор С. Ыекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1131036A1 |

| Цифровой фазовый дискриминатор | 1986 |

|

SU1354387A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368856A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1338094A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368857A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| АВТОКОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ПСЕВДОСЛУЧАЙНОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 1991 |

|

RU2013005C1 |

| АВТОКОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ПСЕВДОСЛУЧАЙНОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 1991 |

|

RU2007875C1 |

Изобретение относится к радиотехнике. Цель изобретения - повьшеФиг.1 ние точности измерения. Дискримина- ;тор содержит формирователи 1 и 2, триггеры 3 и 4, элементы И 5, 6 и 7, счетчик 8, регистры 9 и 11, делитель 10 частоты, генератор 12, ограничители, дифференцирующую цепь, элемент ИЛИ и RS-триггеры. Введение сумматора 13 по модулю два, элемента И 14, порогового блока 16, счетчика 15 и конкретное выполнение порогового блока 16 повьшают достоверность обнаружения слабых протяженных сигнапов с практически любой наперед заданной вероятностью. 1 з.п. ф-лы, 2 ил. to 00 00 О5 ГчЭ

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР | 0 |

|

SU349007A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-07—Публикация

1985-05-08—Подача