Изобретение относится к вычислительной технике и автоматике и может быть использовано при создании высоконадежных одноканальных и многоканальных синхронных резервированных вычислительных комплексов, а также в системах жесткой логики с тактирующими частотами.

Цель изобретения - расширение функциональных возможностей за счет обеспечения многофазного тактирования.

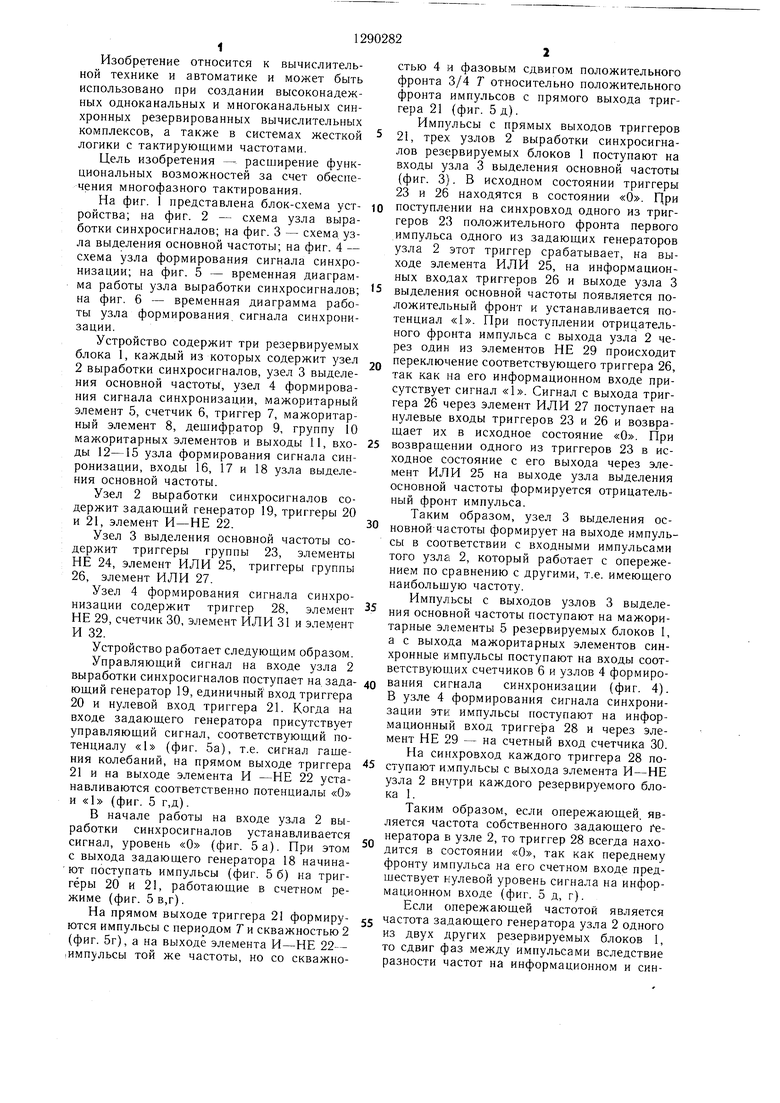

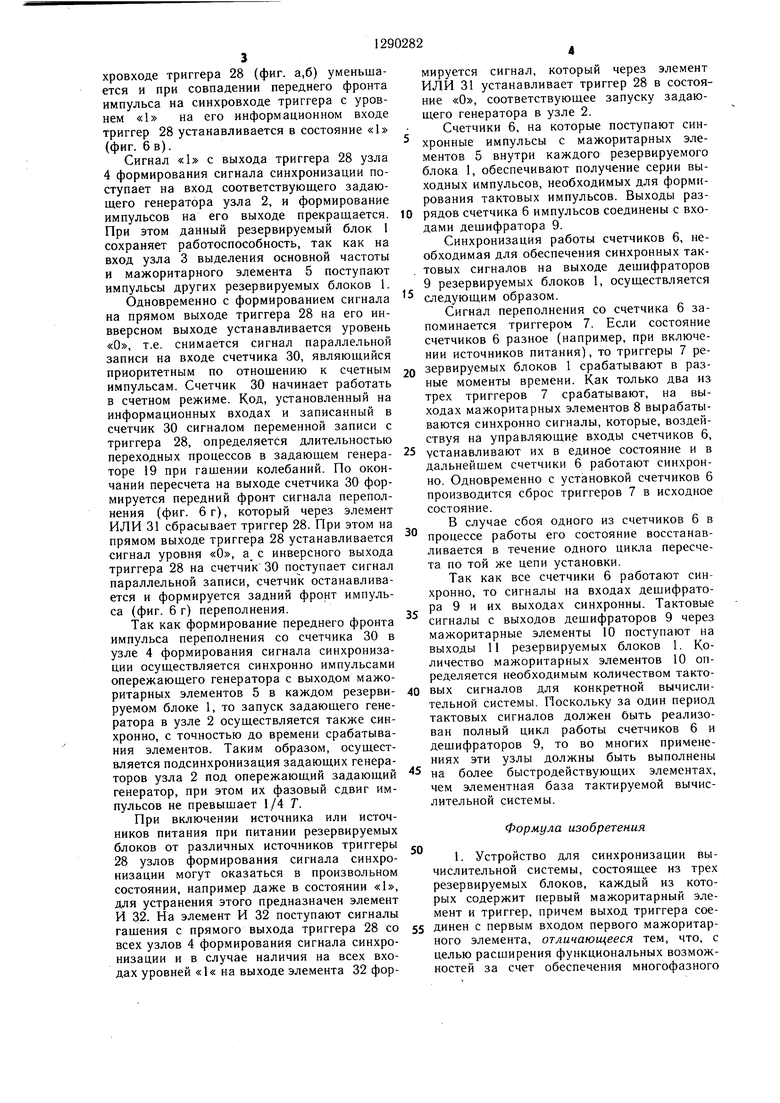

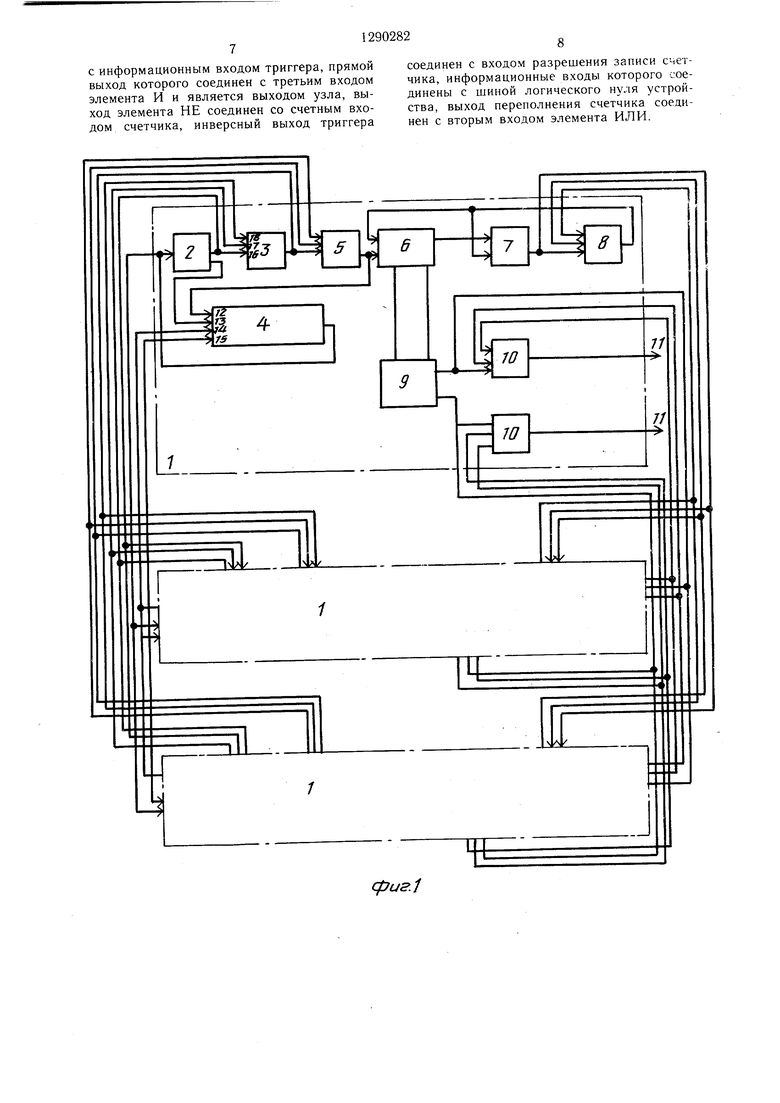

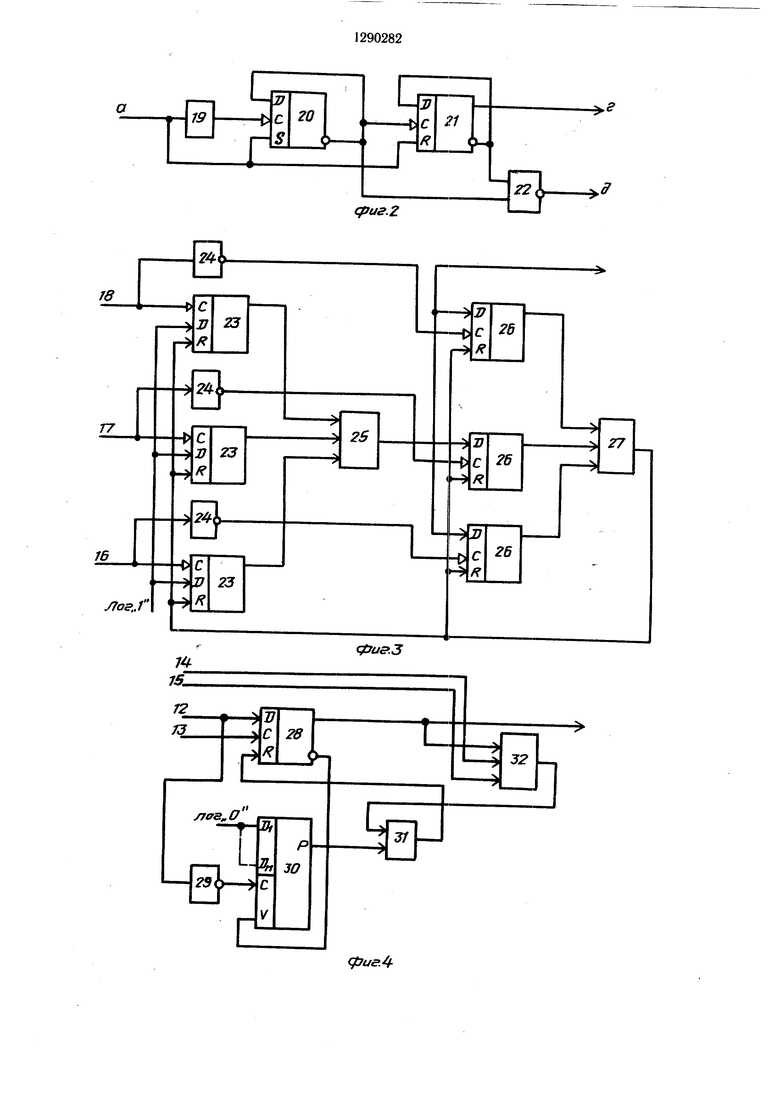

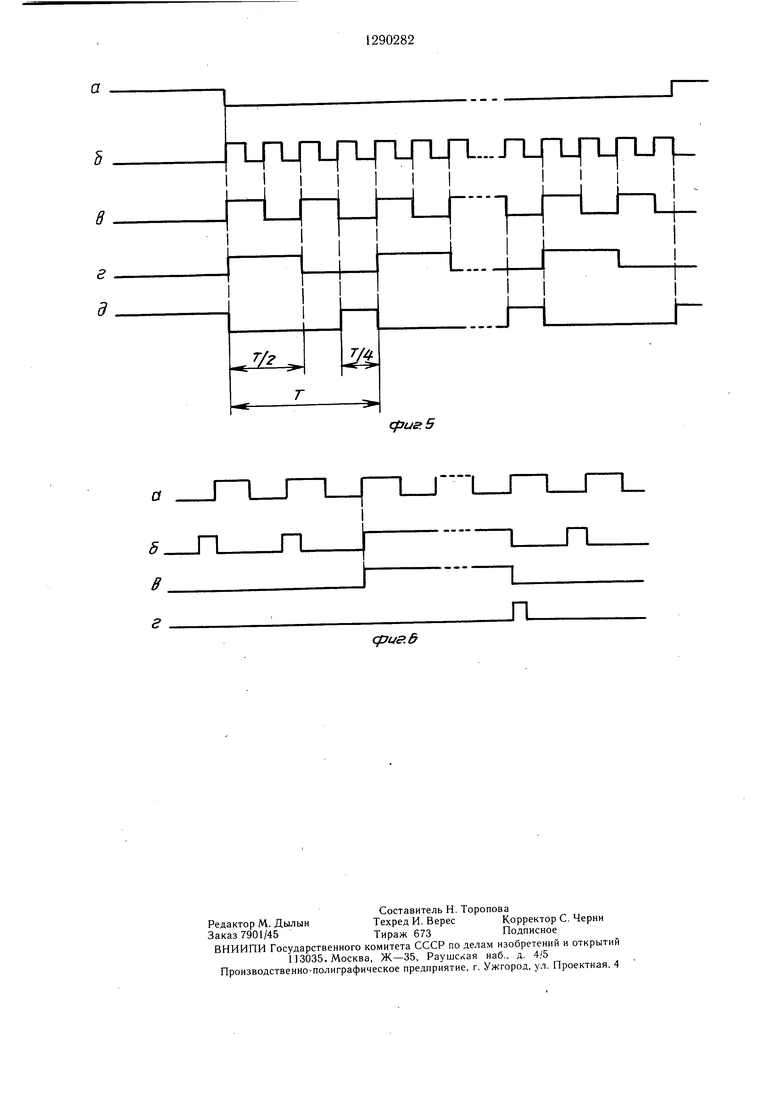

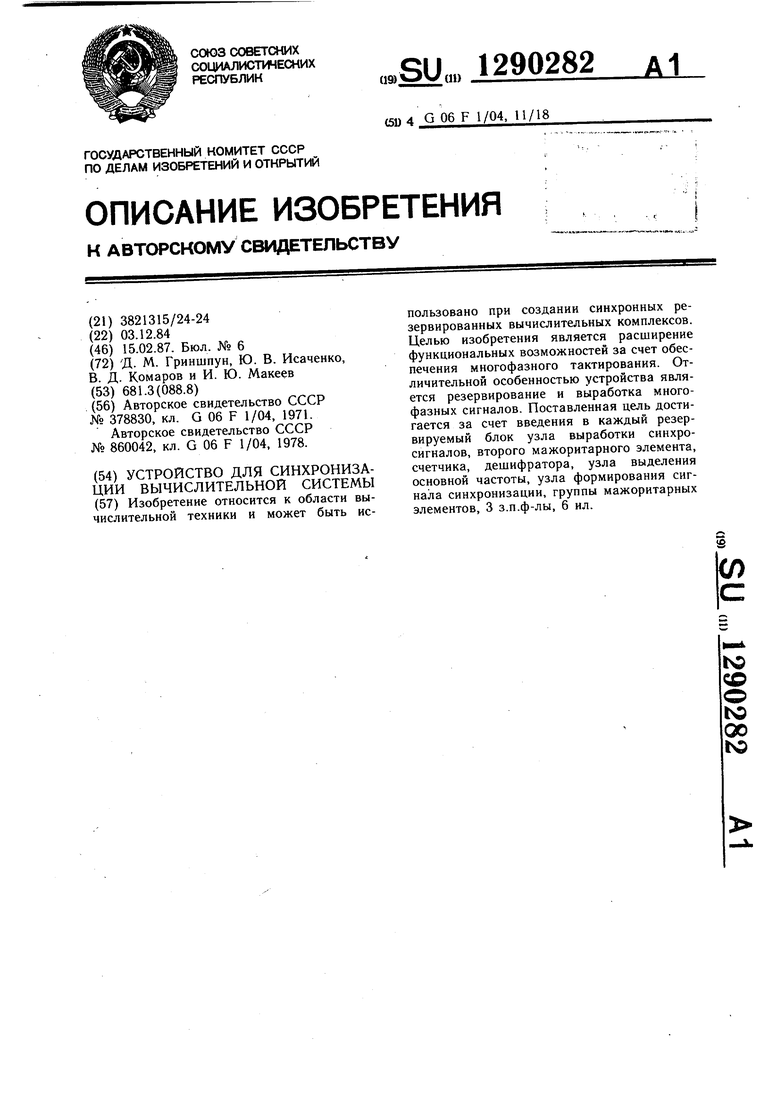

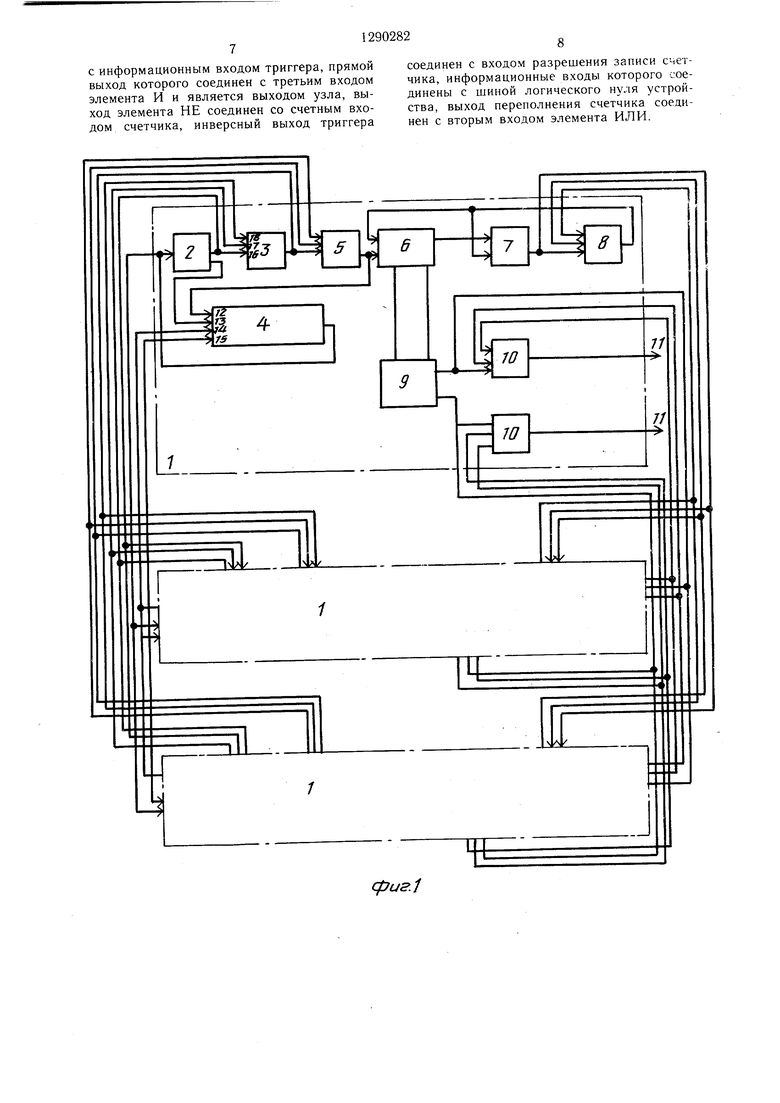

На фиг. 1 представлена блок-схема уст- ю ройства; на фиг. 2 - схема узла выработки синхросигналов; на фиг. 3 - схема узла выделения основной частоты; на фиг. 4 - схема узла формирования сигнала синхронизации; на фиг. 5 - временная диаграмма работы узла выработки синхросигналов; 5 на фиг. 6 - временная диаграмма работы узла формирования, сигнала синхронизации.

Устройство содержит три резервируемых

стью 4 и фазовым сдвигом положительного фронта 3/4 Т относительно положительного фронта импульсов с прямого выхода триггера 21 (фиг. 5 д).

Импульсы с прямых выходов триггеров 21, трех узлов 2 выработки синхросигналов резервируемых блоков 1 поступают на входы узла 3 выделения основной частоты (фиг. 3). В исходном состоянии триггеры 23 и 26 находятся в состоянии «О. При поступлении на синхровход одного из триггеров 23 положительного фронта первого импульса одного из задающих генераторов узла 2 этот триггер срабатывает, на выходе элемента ИЛИ 25, на информацион- ных входах триггеров 26 и выходе узла 3 выделения основной частоты появляется положительный фронт и устанавливается потенциал «1. При поступлении отрицательного фронта импульса с выхода узла 2 через один из элементов НЕ 29 происходит

35

блока 1, каждый из которых содержит узел -п переключение соответствующего триггера 26, 2 выработки синхросигналов, узел 3 выделе- так как на его информационном входе присутствует сигнал «1. Сигнал с выхода триггера 26 через элемент ИЛИ 27 поступает на нулевые входы триггеров 23 и 26 и возвращает их в исходное состояние «О. При возвращении одного из триггеров 23 в исходное состояние с его выхода через элемент ИЛИ 25 на выходе узла выделения основной частоты формируется отрицательный фронт импульса.

Таким образом, узел 3 выделения ос- 30 новной частоты формирует на выходе импульсы в соответствии с входными импульсами того узла 2, который работает с опережением по сравнению с другими, т.е. имеющего наибольшую частоту.

Импульсы с выходов узлов 3 выделения основной частоты поступают на мажоритарные элементы 5 резервируемых блоков 1, а с выхода мажоритарных элементов синхронные импульсы поступают на входы соот- ветствуюпдих счетчиков 6 и узлов 4 формировыработки синхросигналов поступает на зада- 40 вания сигнала синхронизации (фиг. 4). ющий генератор 19, единичный вход триггера В узле 4 формирования сигнала синхрони- 20 и нулевой вход триггера 21. Когда на зации эти импульсы поступают на инфор- входе задающего генератора присутствует мационный вход триггера 28 и через эле- управляющий сигнал, соответствующий по- мент НЕ 29 - на счетный вход счетчика 30. тенциалу «1 (фиг. 5а), т.е. сигнал гаще-На синхровход каждого триггера 28 пония колебаний, на прямом выходе триггера 45 ступают импульсы с выхода элемента И-НЕ

узла 2 внутри каждого резервируемого блока 1.

Таким образом, если опережающей, является частота собственного задающего Генератора в узле 2, то триггер 28 всегда находится в состоянии «О, так как переднему фронту импульса на его счетно.м входе предшествует нулевой уровень сигнала на информационном входе (фиг. 5 д, г).

Если опережающей частотой является частота задающего генератора узла 2 одного из двух других резервируемых блоков 1, то сдвиг фаз между импульсами вследствие разности частот на информационном и синния основной частоты, узел 4 формирования сигнала синхронизации, мажоритарный элемент 5, счетчик 6, триггер 7, мажоритарный элемент 8, дешифратор 9, группу 10 мажоритарных элементов и выходы II, вхо- 25 ды 12-15 узла формирования сигнала син- ронизации, входы 16, 17 и 18 узла выделения основной частоты.

Узел 2 выработки синхросигналов содержит задающий генератор 19, триггеры 20 и 21, элемент И-НЕ 22.

Узел 3 выделения основной частоты содержит триггеры группы 23, элементы НЕ 24, элемент ИЛИ 25, триггеры группы 26, элемент ИЛИ 27.

Узел 4 формирования сигнала синхронизации содержит триггер 28, элемент НЕ 29, счетчик 30, элемент ИЛИ 31 и элемент И 32.

Устройство работает следующим образом.

Управляющий сигнал на входе узла 2

21 и на выходе элемента И -НЕ 22 устанавливаются соответственно потенциалы «О и «1 (фиг. 5 г,д).

В начале работы на входе узла 2 выработки синхросигналов устанавливается сигнал, уровень «О (фиг. 5 а). При этом с выхода задающего генератора 18 начина- ют поступать импульсы (фиг. 56) на триггеры 20 и 21, работающие в счетном режиме (фиг. 5 в,г).

На прямом выходе триггера 21 формируются импульсы с периодом Т и скважностью 2 (фиг. 5г), а на выходе элемента И-НЕ 22- ИМпульсы той же частоты, но со скважно55

стью 4 и фазовым сдвигом положительного фронта 3/4 Т относительно положительного фронта импульсов с прямого выхода триггера 21 (фиг. 5 д).

Импульсы с прямых выходов триггеров 21, трех узлов 2 выработки синхросигналов резервируемых блоков 1 поступают на входы узла 3 выделения основной частоты (фиг. 3). В исходном состоянии триггеры 23 и 26 находятся в состоянии «О. При поступлении на синхровход одного из триггеров 23 положительного фронта первого импульса одного из задающих генераторов узла 2 этот триггер срабатывает, на выходе элемента ИЛИ 25, на информацион- ных входах триггеров 26 и выходе узла 3 выделения основной частоты появляется положительный фронт и устанавливается потенциал «1. При поступлении отрицательного фронта импульса с выхода узла 2 через один из элементов НЕ 29 происходит

хровходе триггера 28 (фиг. а,б) уменьшается и при совпадении переднего фронта импульса на синхровходе триггера с уровнем «1 на его информационном входе триггер 28 устанавливается в состояние «1 (фиг. 6 в).

Сигнал «1 с выхода триггера 28 узла 4 формирования сигнала синхронизации поступает на вход соответствующего задающего генератора узла 2, и формирование импульсов на его выходе прекращается. При этом данный резервируемый блок 1 сохраняет работоспособность, так как на вход узла 3 выделения основной частоты и мажоритарного элемента 5 поступают импульсы других резервируемых блоков 1.

мируется сигнал, который через элемент ИЛИ 31 устанавливает триггер 28 в состояние «О, соответствующее запуску задающего генератора в узле 2.

Счетчики 6, на которые поступают син- хронные импульсы с мажоритарных элементов 5 внутри каждого резервируемого блока 1, обеспечивают получение серии выходных импульсов, необходимых для формирования тактовых импульсов. Выходы раз- 10 рядов счетчика б импульсов соединены с входами дешифратора 9.

Синхронизация работы счетчиков 6, необходимая для обеспечения синхронных тактовых сигналов на выходе дешифраторов 9 резервируемых блоков 1, осуществляется

Одновременно с формированием сигнала следующим образом. на прямом выходе триггера 28 на его ин-Сигнал переполнения со счетчика 6 запоминается триггером 7. Если состояние

вверсном выходе устанавливается уровень «О, т.е. снимается сигнал параллельной записи на входе счетчика 30, являющийся приоритетным по отношению к счетным импульсам. Счетчик 30 начинает работать в счетном режиме. Код, установленный на информационных входах и записанный в счетчик 30 сигналом переменной записи с триггера 28, определяется длительностью переходных процессов в задающем генераторе 19 при гащении колебаний. По окончании пересчета на выходе счетчика 30 формируется передний фронт сигнала переполнения (фиг. 6 г), который через элемент ИЛИ 31 сбрасывает триггер 28. При этом на прямом выходе триггера 28 устанавливается сигнал уровня «О, а с инверсного выхода триггера 28 на счетчик 30 поступает сигнал параллельной записи, счетчик останавливается и формируется задний фронт импульса (фиг. 6 г) переполнения.

Так как формирование переднего фронта импульса переполнения со счетчика 30 в узле 4 формирования сигнала синхронизации осуществляется синхронно импульсами опережающего генератора с выходом мажоритарных элементов 5 в каждом резервируемом блоке 1, то запуск задающего генератора в узле 2 осуществляется также синхронно, с точностью до времени срабатывания элементов. Таким образом, осуществляется подсинхронизация задающих генера25

счетчиков 6 разное (например, при включении источников питания), то триггеры 7 ре2Q зервируемых блоков 1 срабатывают в разные моменты времени. Как только два из трех триггеров 7 срабатывают, на выходах мажоритарных элементов 8 вырабатываются синхронно сигналы, которые, воздействуя на управляющие входы счетчиков 6, устанавливают их в единое состояние и в дальнейшем счетчики 6 работают синхронно. Одновременно с установкой счетчиков 6 производится сброс триггеров 7 в исходное состояние.

В случае сбоя одного из счетчиков 6 в процессе работы его состояние восстанавливается в течение одного цикла пересчета по той же цепи установки.

Так как все счетчики 6 работают синхронно, то сигналы на входах дешифратора 9 и их выходах синхронны. Тактовые сигналы с выходов дешифраторов 9 через мажоритарные элементы 10 поступают на выходы 11 резервируемых блоков 1. Количество мажоритарных элементов 10 определяется необходимым количеством такто40 вых сигналов для конкретной вычислительной системы. Поскольку за один период тактовых сигналов должен быть реализован полный цикл работы счетчиков б и дешифраторов 9, то во многих применениях эти узлы должны быть выполнены

45

35

торов узла 2 под опережающий задающий на более быстродействующих элементах.

генератор, при этом их фазовый сдвиг импульсов не превышает 1/4 Т.

При включении источника или источников питания при питании резервируемых блоков от различных источников триггеры 28 узлов формирования сигнала синхронизации могут оказаться в произвольном состоянии, например даже в состоянии «1, для устранения этого предназначен элемент И 32. На элемент И 32 поступают сигналы гашения с прямого выхода триггера 28 со всех узлов 4 формирования сигнала синхронизации и в случае наличия на всех входах уровней «1« на выходе элемента 32 форчем элементная база тактируемой вычислительной системы.

Формула изобретения

50

1. Устройство для синхронизации вычислительной системы, состоящее из трех резервируемых блоков, каждый из которых содержит первый мажоритарный элемент и триггер, причем выход триггера сое- 55 динен с первым входом первого мажоритарного элемента, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения многофазного

мируется сигнал, который через элемент ИЛИ 31 устанавливает триггер 28 в состояние «О, соответствующее запуску задающего генератора в узле 2.

Счетчики 6, на которые поступают син- хронные импульсы с мажоритарных элементов 5 внутри каждого резервируемого блока 1, обеспечивают получение серии выходных импульсов, необходимых для формирования тактовых импульсов. Выходы раз- рядов счетчика б импульсов соединены с входами дешифратора 9.

Синхронизация работы счетчиков 6, необходимая для обеспечения синхронных тактовых сигналов на выходе дешифраторов 9 резервируемых блоков 1, осуществляется

следующим образом. Сигнал переполнения со счетчика 6 за5

счетчиков 6 разное (например, при включении источников питания), то триггеры 7 реQ зервируемых блоков 1 срабатывают в разные моменты времени. Как только два из трех триггеров 7 срабатывают, на выходах мажоритарных элементов 8 вырабатываются синхронно сигналы, которые, воздействуя на управляющие входы счетчиков 6, устанавливают их в единое состояние и в дальнейшем счетчики 6 работают синхронно. Одновременно с установкой счетчиков 6 производится сброс триггеров 7 в исходное состояние.

В случае сбоя одного из счетчиков 6 в процессе работы его состояние восстанавливается в течение одного цикла пересчета по той же цепи установки.

Так как все счетчики 6 работают синхронно, то сигналы на входах дешифратора 9 и их выходах синхронны. Тактовые сигналы с выходов дешифраторов 9 через мажоритарные элементы 10 поступают на выходы 11 резервируемых блоков 1. Количество мажоритарных элементов 10 определяется необходимым количеством такто0 вых сигналов для конкретной вычислительной системы. Поскольку за один период тактовых сигналов должен быть реализован полный цикл работы счетчиков б и дешифраторов 9, то во многих применениях эти узлы должны быть выполнены

5

5

на более быстродействующих элементах.

на более быстродействующих элементах.

чем элементная база тактируемой вычислительной системы.

Формула изобретения

1. Устройство для синхронизации вычислительной системы, состоящее из трех резервируемых блоков, каждый из которых содержит первый мажоритарный элемент и триггер, причем выход триггера сое- динен с первым входом первого мажоритарного элемента, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения многофазного

10

20

1290282 5

тактирования, в каждый резервируемый блок введен узел выработки синхросигналов, второй мажоритарный элемент, счетчик, дешифратор, узел выделения основной частоты, узел формирования сигнала синхронизации, группа мажоритарных элементов, причем первый выход каждого резервируемого блока соединен соответственно с первым и вторым входами остальных резервируемых блоков, второй выход каждого резервируемого блока соединен соответственно с третьим и четвертым входами остальных резервируемых блоков, третий выход каждого резервируемого блока соединен соответственно с пятым и шестым входами остальных резервируемых блоков, четвертый выход каждого резервируемого блока соединен соответственно с седьмым и восьмым входами остальных резервируемых блоков, причем в каждом резервируемом блоке первый выход узла выработки синхросигналов соединен с первым входом узла выделения основной частоты и является первым выходом каждого резервируемого блока, первый и второй входы каждого резервируемого блока являются соответственно вторым и третьим входами узла выделения основной частоты, выход узла формирования сигнала синхронизации в каждом резервируемом блоке соединен с входом узла выработки синхросигналов и является вторым выходом каждого резерввируемоого блока, третий и четвертый входы каждого резервируемого блока соединены соответственно с первым и вторым входами узла формирования сигнала синхронизации, третий вход которого соединен в каждом резервируемом блоке с вторым выходом узла выработки синхросигналов, выход второго мажоритарного элемента в каждом резервируемом блоке соединен с синхровходом счетчика и с четвертым входом узла формирования сигнала синхронизации, выход узла выделения основной частоты каждого резервируемого блока соединен с первым входом второго мажоритарного элемента и являтеся третьим выходом каждого резервируемого блока, пятый и шестой входы которого являются соответственно вторым и третьим входами второго мажоритарного элемента.

выми входами мажоритарных элементов группы, выходы которых являются группой выходов каждого резервируемого блока и соединены соответственно с вторым и третьим в: :одами мажоритарных элементов группы.

2.Устройство по п. 1, отличающееся тем, что узел выработки синхросигналов содержит задающий генератор, два триггера, элемент И-НЕ, причем выход задающего генератора соединен с синхровходрм первого триггера, инверсный выход которого соединен с информационным входом первого триггера, с первым входом элемента И-НЕ и с синхровходом второго триггера, инверсный выход которого соединен с информационным входом второго триг 5 гера и с вторым входом элемента И-Н прямой выход второго триггера является первым выходом узла, выход элемента И- НЕ является вторым выходом узла, вход которого соединен с входом запуска задающего генератора, с единичным входом первого триггера и с нулевым входом второго триггера.

3.Устройство по. 1, отличающееся тем, что узел выделения основной частоты содержит две группы триггеров, два элемента ИЛИ, три элемента HF, причем первый, второй и третий входы узла соединены с синхровходами соответственно первого, второго и третьего триггеров первой группы и с входами соответственно первого, второго и третьего элемента НЕ, выходы которых соединены с синхровходами соответственно первого, второго и третьего триггеров второй группы, выходы первого, второго и третьего триггеров первой группы соединены соответственно с входами первого элемента ИЛИ, выход которого соединен с информационными входами первого, второго и третьего триггеров второй группы и является выходом узла, выходы первого, второго и третьего триггеров второй группы соединены соответственно с входами

40 второго элемента ИЛИ, выход которого соединен с нулевыми входами первого, второго и третьего триггеров первой группы и с нулевыми входами первого, второго и третьего триггеров второй группы, информационные входы первого, второго и третьего

25

30

35

50

выход переполнения счетчика каждого резер- триггеров первой группы соединены с шиной

единичного потенциала устройства.

4. Устройство по п. 1, отличающееся тем, что узел формирования сигнала синхронизации содержит триггер, счетчик, элемент НЕ, элемент ИЛИ, элемент И, причем первый и второй входы узла соединены соответственно с первым и вторым входами элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с нулевым входом триггера, третий вход узла соединен с информационным входом триггера и с входом элемента НЕ, четвертый вход узла соединен

вируемого блока соединен с единичным входом триггера, выход которого соединен с первым входом первого мажоритарного элемента и является четвертым выходом каждого резервируемого блока, второй и третий входы первого мажоритарного элемента являются соответственно седьмым и восьмым входами каждого резервируемого блока, выход первого мажоритарного элемента соединен с нулевым входом триггера и с входом разрешения счета счетчика, выходы которого в каждом резервируемом блоке соединен с входами дешифратора, выходы которого соединены соответственно с пер55

0

выми входами мажоритарных элементов группы, выходы которых являются группой выходов каждого резервируемого блока и соединены соответственно с вторым и третьим в: :одами мажоритарных элементов группы.

2.Устройство по п. 1, отличающееся тем, что узел выработки синхросигналов содержит задающий генератор, два триггера, элемент И-НЕ, причем выход задающего генератора соединен с синхровходрм первого триггера, инверсный выход которого соединен с информационным входом первого триггера, с первым входом элемента И-НЕ и с синхровходом второго триггера, инверсный выход которого соединен с информационным входом второго триггера и с вторым входом элемента И-Н прямой выход второго триггера является первым выходом узла, выход элемента И- НЕ является вторым выходом узла, вход которого соединен с входом запуска задающего генератора, с единичным входом первого триггера и с нулевым входом второго триггера.

3.Устройство по. 1, отличающееся тем, что узел выделения основной частоты содержит две группы триггеров, два элемента ИЛИ, три элемента HF, причем первый, второй и третий входы узла соединены с синхровходами соответственно первого, второго и третьего триггеров первой группы и с входами соответственно первого, второго и третьего элемента НЕ, выходы которых соединены с синхровходами соответственно первого, второго и третьего триггеров второй группы, выходы первого, второго и третьего триггеров первой группы соединены соответственно с входами первого элемента ИЛИ, выход которого соединен с информационными входами первого, второго и третьего триггеров второй группы и является выходом узла, выходы первого, второго и третьего триггеров второй группы соединены соответственно с входами

0 второго элемента ИЛИ, выход которого соединен с нулевыми входами первого, второго и третьего триггеров первой группы и с нулевыми входами первого, второго и третьего триггеров второй группы, информационные входы первого, второго и третьего

5

0

5

триггеров первой группы соединены с шиной

с информационным входом триггера, прямой выход которого соединен с третьим входом элемента И и является выходом узла, выход элемента НЕ соединен со счетным входом счетчика, инверсный выход триггера

соединен с входом разрешения записи счетчика, информационные входы которого соединены с шиной логического нуля устройства, выход переполнения счетчика соединен с вторым входом элемента ИЛИ.

сриг.1

74

(иг.г

фи&.З

дзиеЛ

cfJue.S

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Устройство для синхронизации цифровой системы | 1981 |

|

SU981980A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Многоканальный резервированный генератор | 1989 |

|

SU1699028A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для мажоритарного выбора сигналов | 1981 |

|

SU1018120A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании синхронных резервированных вычислительных комплексов. Целью изобретения является расширение функциональных возможностей за счет обеспечения многофазного тактирования. Отличительной особенностью устройства является резервирование и выработка многофазных сигналов. Поставленная цель достигается за счет введения в каждый резервируемый блок узла выработки синхросигналов, второго мажоритарного элемента, счетчика, дешифратора, узла выделения основной частоты, узла формирования сигнала синхронизации, группы мажоритарных элементов, 3 з.п.ф-лы, 6 ил. ь: QO о 00 Ю

а

n

ff

n

n

CptJc &

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ СИГНАЛОВ | 0 |

|

SU378830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синхронизации сигналов | 1978 |

|

SU860042A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1984-12-03—Подача