11

Изобретение относится к вычисли- 1 тельной технике и может быть исполь зовано при построении цифровых вычислительных машин высокого быстродействия.

Цель изобретения - увеличение быстродействия устройства.

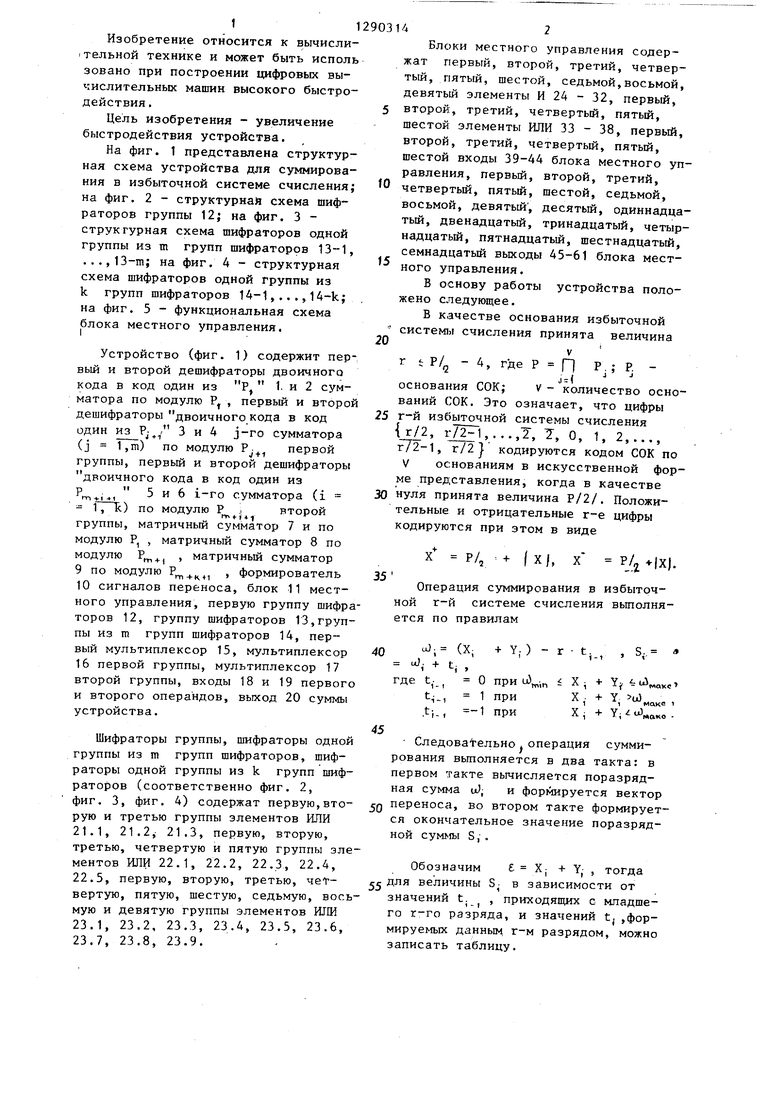

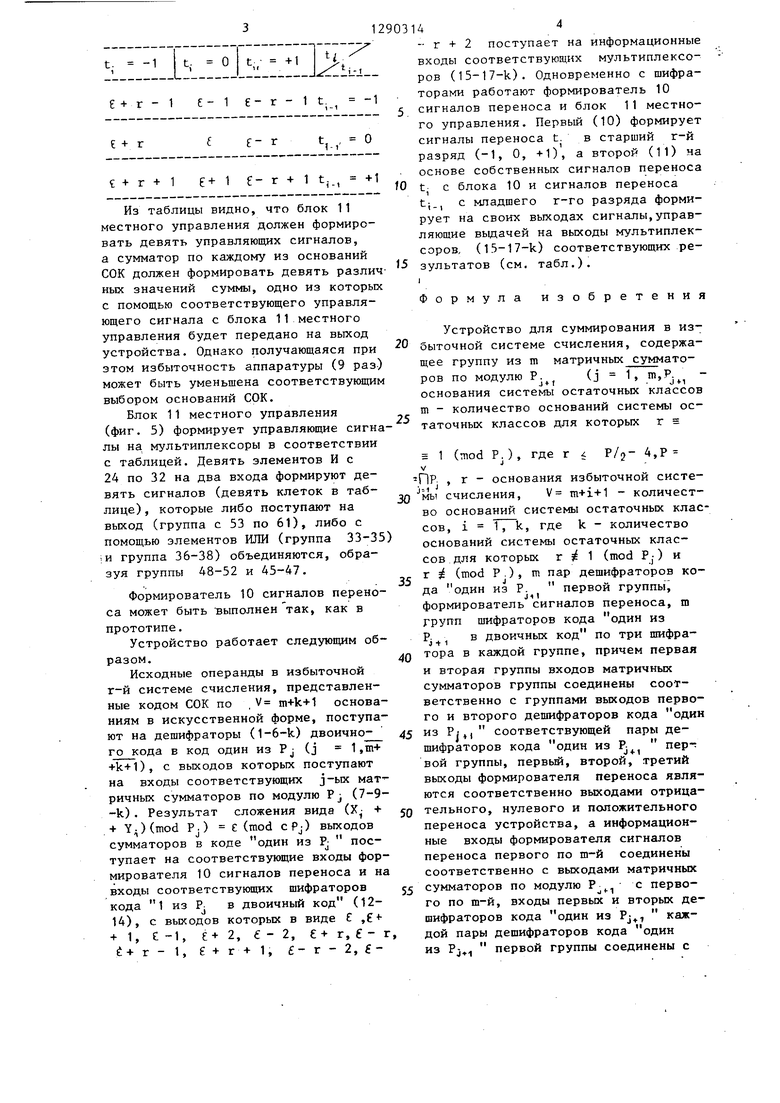

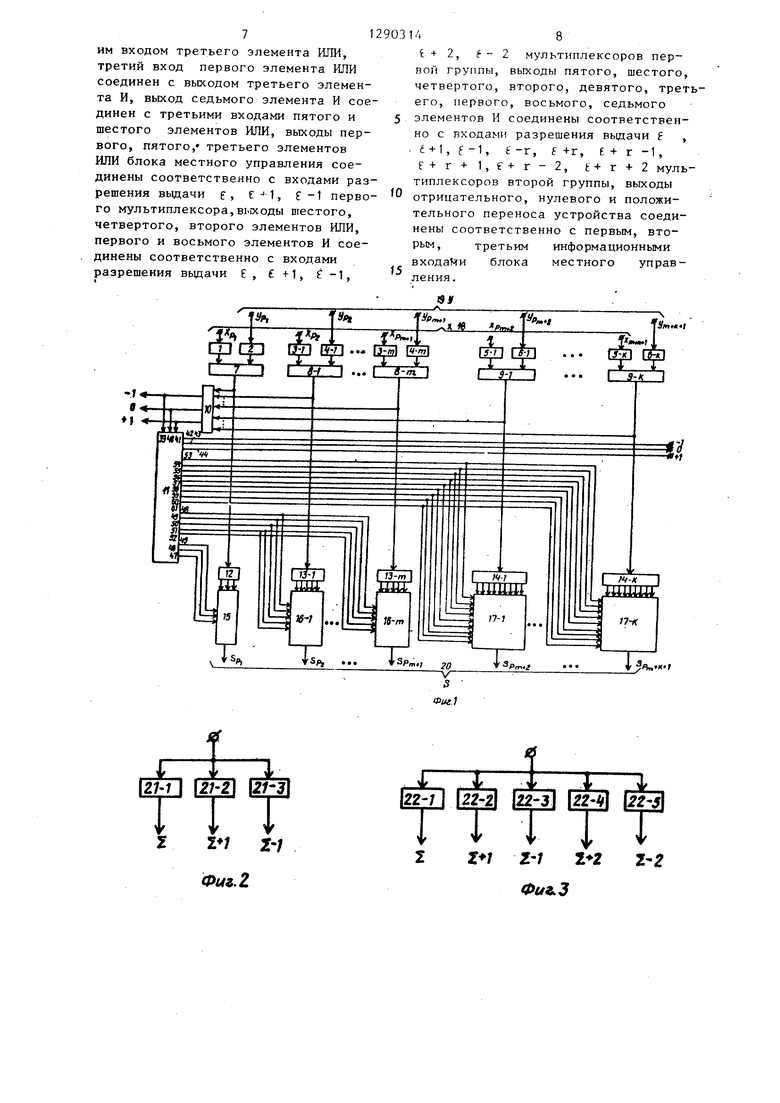

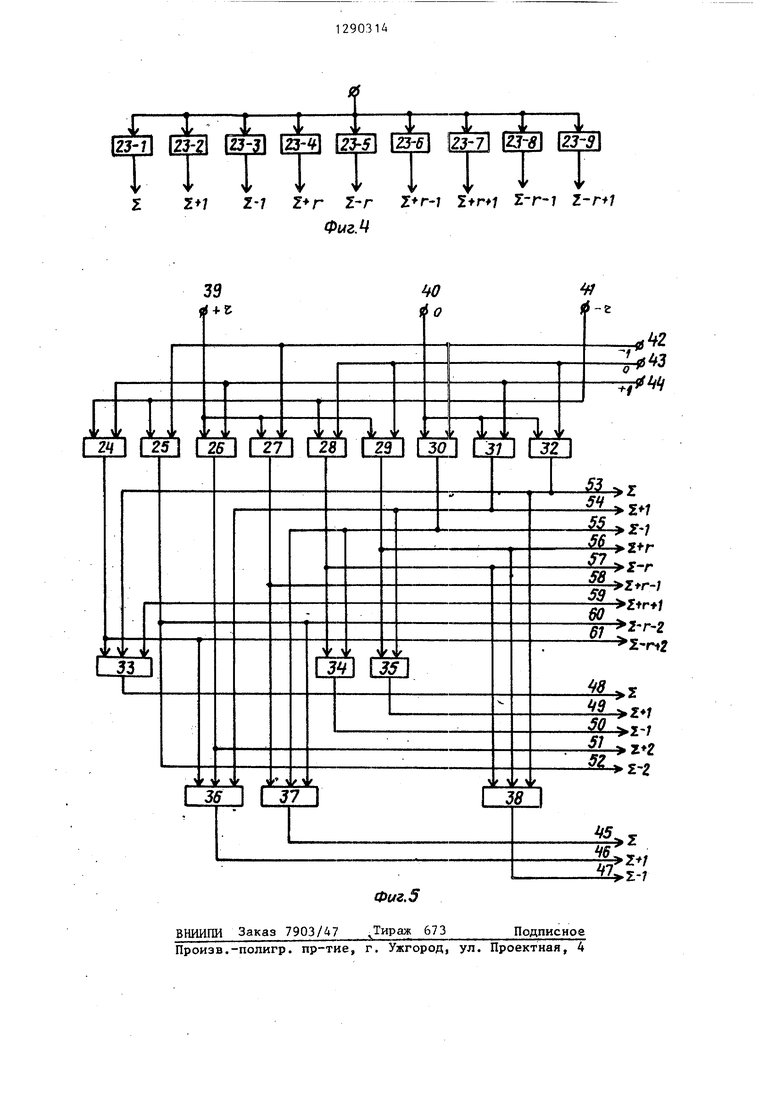

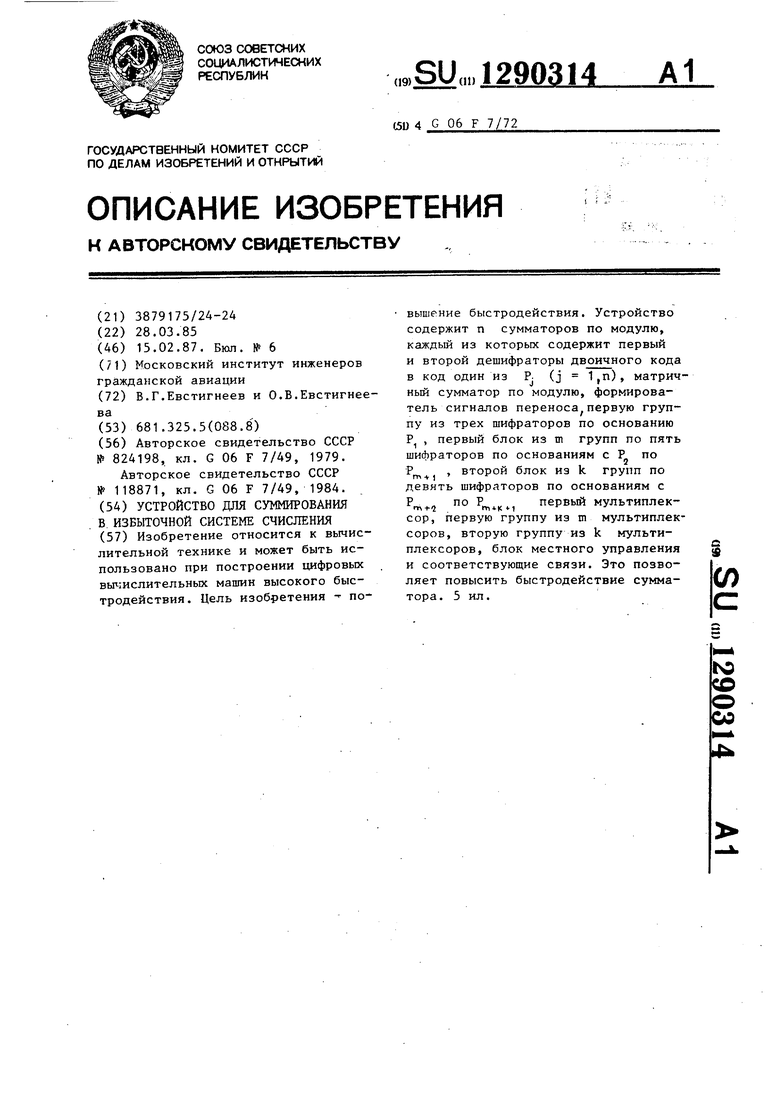

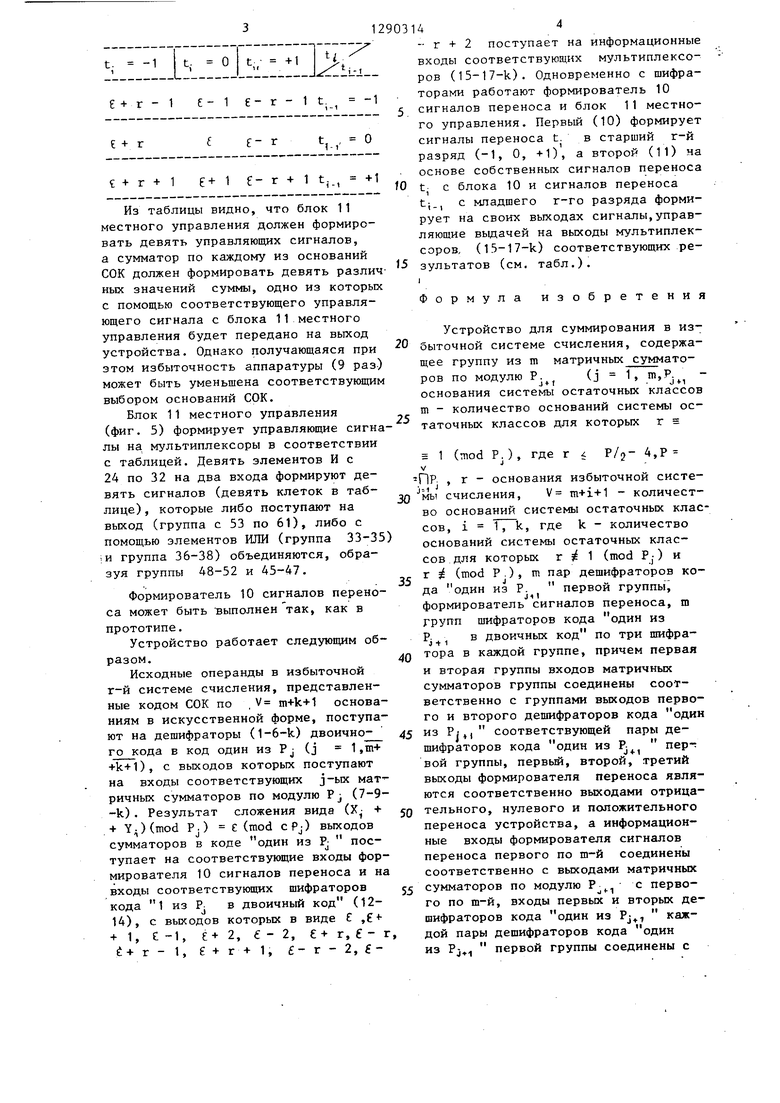

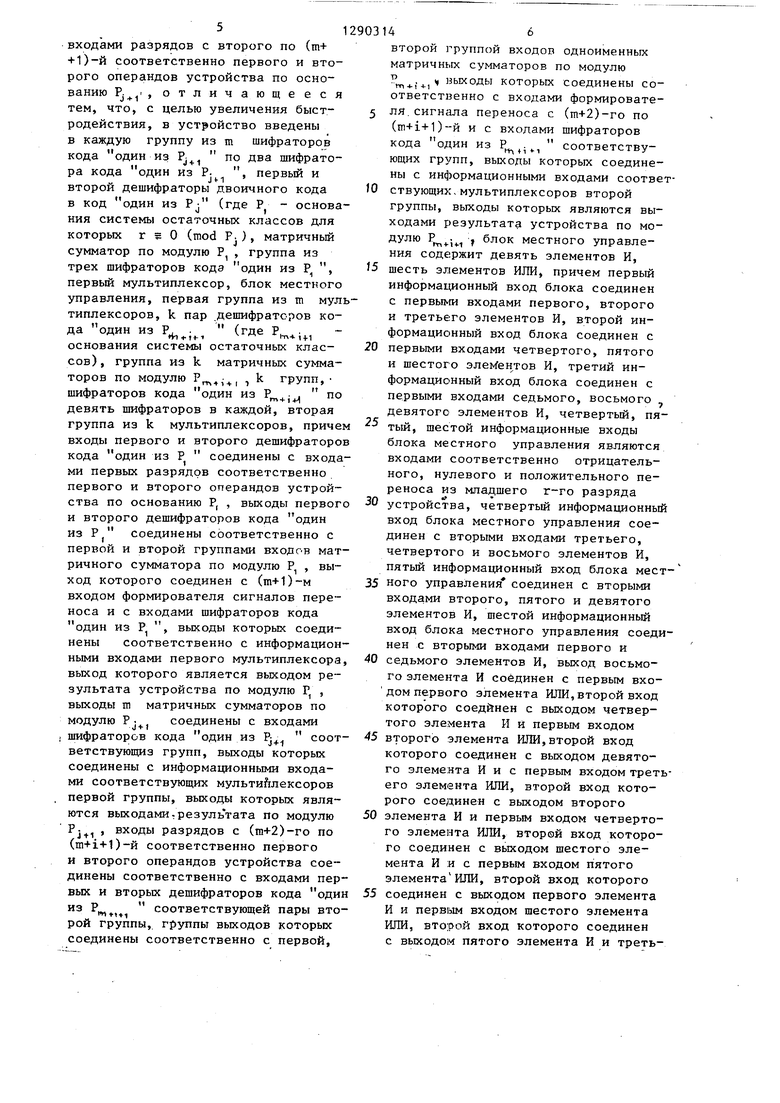

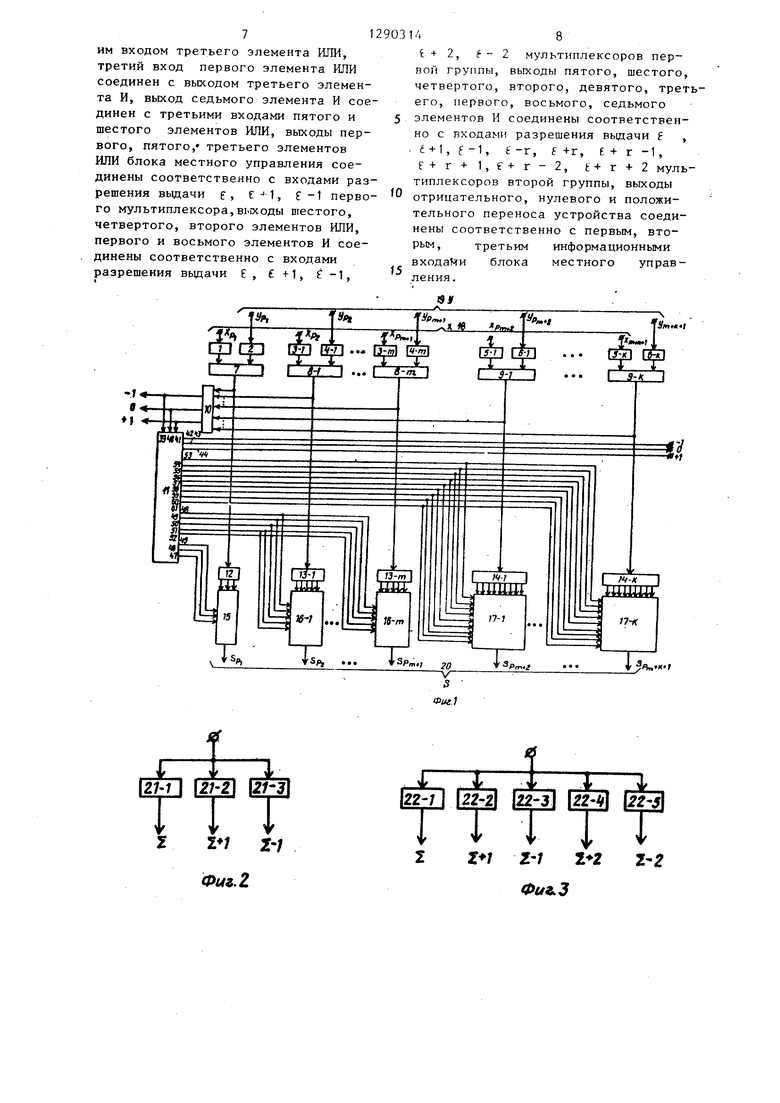

На фиг. 1 представлена структурная схема устройства для суммирования в избыточной системе счисленияj на фиг. 2 - структурная схема шифраторов группы 12; на фиг, 3 - структурная схема шифраторов одной группы из m групп шифраторов 13-1, ...,13-т; на фиг. 4 - структурная схема шифраторов одной группы из k групп шифраторов 14-1,...,14-k; на фиг. 5 - функциональная схема

блока местного управления.

Устройство (фиг. 1) содержит первый и второй дешифраторы двоичного кода в код один из Р, 1. и 2 сумматора по модулю Р , первый и второ

дешифраторы двоичного кода в код один из PJ+Y 3 и 4 j-ro сумматора (J 1,т) по модулю Р. первой группы, первый и второй дешифраторы двоичного кода в код один из

5 и 6 i-ro сумматора (i второй

по модулю Р .1

„ «.(

группы, матричный сумматор 7 и по модулю Р, , матричный сумматор 8 по модулю Р.4., , матричный сумматор

9 по модулю Р

пп -tK 1

формирователь

10 сигналов переноса, блок 11 местного управления, первую группу шифраторов 12, группу шифраторов 13,группы из m групп шифраторов 14, первый мультиплексор 15, мультиплексор 16 первой группы, мультиплексор 17 второй группы, входы 18 и 19 первого и второго операндов, выход 20 сумтл устройства.

Шифраторы группы, шифраторы одной группы из m групп шифраторов, шифраторы одной группы из k групп шифраторов (соответственно фиг. 2,

35

Операция суммирования в избыточной г-й системе счисления вьтолня- ется по правилам

40

-1- Y; ) - Г t;

u). (Х; , + tj ,

где t., О при u)in t.. 1 при -1 при

s..,

-1-1 t-,-,

X i 4- Y 4 ui X .. + Y: Ы. X

мак + Yj iJ«aKO 45

Следовательно , операция суммирования вьтолняется в два такта: в первом такте вычисляется поразрядная сумма uJ- и формируется вектор

фиг. 3, фиг. 4) содержат первую,вто- 50 переноса, во втором такте формирует- рую и третью группы элементов ИЛИ ся окончательное значение поразряд- 21.1, 21.2, 21.3, первую, вторую, ной суммы S,. третью, четвертую и пятую группы элементов ИЛИ 22.1, 22.2, 22.3, 22.4, Обозначим X; + Y, , тогда 22.5, первую, вторую, третью, чеТ- для величины S,- в зависимости от вертую, пятую, шестую, седьмую, вось- значений t. , приходящих с младше- мую и девятую группы элементов И1Ш го г-го разряда, и значений tj ,фор- 23.1, 23.2, 23.3, 23.4, 23.5, 23.6, мируемь Х данным г-м разрядом, можно 23.7, 23.8, 23 .9 . -записать таблицу.

Блоки местного управления содержат первый, второй, третий, четвер- тьй, пятый, шестой, седьмой,восьмой, девятый элементы И 24 - 32, первый, второй, третий, четвертый, пятый, шестой элементы ИЛИ 33 - 38, первый, второй, третий, четвертый, пятый, шестой входы 39-44 блока местного управления, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый выходы 45-61 блока местного управления.

В основу работы устройства положено следующее.

В качестве основания избыточной систем счисления принята величина

Р.

Р. г t Р/,2 - 4, где Р П

j (

основания СОК; V - количество оснований СОК. Это означает, что цифры

г-й избыточной системы счисления г/2, I-/2-1,. ..,2, Y, О, 1, 2,..., г72-1, r/2j кодируются кодом СОК по V основаниям в искусственной форме представления, когда в качестве

нуля принята величина Р/2/. Положительные и отрицательные г-е цифры кодируются при этом в виде

35

х Р/, + ( X/, х Р/г(х).

Операция суммирования в избыточной г-й системе счисления вьтолня- ется по правилам

0

-1- Y; ) - Г t;

u). (Х; , + tj ,

где t., О при u)in t.. 1 при -1 при

s..,

-1-1 t-,-,

X i 4- Y 4 ui X .. + Y: Ы. X

мак + Yj iJ«aKO 45

Следовательно , операция суммирования вьтолняется в два такта: в первом такте вычисляется поразрядная сумма uJ- и формируется вектор

+r-1 E-1 €-r-1 t. -1

e + r

e- r t,, 0

€+r+i e+1 e-r+it.,

Из таблицы видно, что блок 11 местного управления должен формировать девять управляющих сигналов, а сумматор по каждому из оснований СОК должен формировать девять различных значений суммы, одно из которых с помощью соответствующего управляющего сигнала с блока 11 местного управления будет передано на выход устройства. Однако получающаяся при этом избыточность аппаратуры (9 раз) может быть уменьшена соответствунщим выбором оснований СОК.

Блок 11 местного управления (фиг. 5) формирует управляющие сигналы на мультиплексоры в соответствии с таблицей. Девять элементов И с 24 по 32 на два входа формируют девять сигналов (девять клеток в таблице) , которые либо поступают на выход (группа с 53 по 61), либо с помощью элементов ИЛИ (группа 33-35 |и группа 36-38) объединяются, образуя группы 48-52 и 45-47.

Формирователь 10 сигналов переноса может быть выполнен так, как в прототипе.

Устройство работает следующим образом.

Исходные операнды в избыточной г-й системе счисления, представленные кодом СОК по , V m+k+1 основаниям в искусственной форме, поступают на дешифраторы (l-6-k) двоично- го кода в код один из PJ (j 1 ,ni+ +k-)-1), с выходов которых поступают на входы соответствующих j-ых матричных сумматоров по модулю PJ (7-9- -k). Результат сложения вида (Х + + Y;)(mod PJ ) е (mod cPj) выходов сумматоров в коде один из Pj поступает на соответствующие входы формирователя 10 сигналов переноса и на входы соответствующих шифраторов кода 1 из PJ в двоичный код (12- 14), с выходов которых в виде ,-1-1, е 1, е-1- 2, € - 2, €-1- г, е - г

i+ г - , е+г+1, -г-2,

03144

- г + 2 поступает на информационные входы соответствующих мультиплексоров (15-17-k). Одновременно с шифраторами работают формирователь 10

5 сигналов переноса и блок 11 местного управления. Первый (10) формирует сигналы переноса t. в старший г-й разряд (-1, О, +1), а второй (11) на основе собственных сигналов переноса

О t с блока 10 и сигналов переноса tj., с мпадшего г-го разряда формирует на своих выходах сигналы,управляющие выдачей на выходы мультиплексоров, (15-17-k) соответствующих ре15 зультатов (см. табл.).

Формула изобретения

Устройство для суммирования в избыточной системе счисления, содержащее группу из m матричных сумматоров по модулю Р.

J + I

(J 1. .n.,Pj

основания системы остаточных классов m - количество оснований системы остаточных классов для которых г н

S 1 (mod Р.), где г i Р/2- 4,Р V

П , г - основания избыточной систе- 1мы счисления, V m+i+1 - количество оснований системы остаточньк клас- i TTk,

сов,

где k - количество

оснований системы остаточных классов для которьк г э 1 (mod Pj) и г 3 (mod Р .), ш пар дешифраторов кода один из Р. первой группы, формирователь сигналов переноса, m групп шифраторов кода один из Р 1 в двоичных код по три шифратора в каждой группе, причем первая и вторая группы входов матричных сумматоров группы соединены соответственно с группами выходов первого и второго дешифраторов кода один

из Р

t соответствующей пары дешифраторов кода один из Р- пер- вой группы, первый, второй, третий выходы формирователя переноса являются соответственно выходами отрицательного, нулевого и положительного переноса устройства, а информационные входы формирователя сигналов переноса первого по ш-й соединены соответственно с выходами матричных

с первосумматоров по модулю Р

jt-1

го по т-й, входы первых и вторых дешифраторов кода один из Pj, каждой пары дешифраторов кода один из Pj первой группы соединены с

входами разрядов с второго по (т+ +1)-й соответственно первого и второго операндов устройства по основанию Pj,, о тлич ающе е с я тем, что, с целью увеличения быстродействия, в устройство введены в каждую группу из m шифраторов кода один из Pj по два шифратора кода один из Р- , первый и второй дешифраторы двоичного кода в код один из PJ (где Р - основания системы остаточных классов для которых г О (mod Р.), матричный сумматор по модулю Р, , группа из трех шифраторов кода один из Р , первьй мультиплексор, блок местного управления, первая группа из m мультиплексоров, k пар .дешифраторов кода один из , (где Р,;, - основания системы остаточных классов), группа из k матричных сумматоров по модулю , k групп, шифраторов кода один из Р„ц.; по девять шифраторов в каждой, вторая группа из k мультиплексоров, причем входы первого и второго дешифраторов кода один из Р соединены с входами первых разрядов соответственно первого и второго операндов устройства по основанию Р, , выходы первог и второго дешифраторов кода один из Р соединены соответственно с первой и второй группами входов матричного сумматора по модулю Р, , выход которого соединен с (т+1)-м входом формирователя сигналов переноса и с входами шифраторов кода один из Р , выходы которых соединены соответственно с информационными входами первого мультиплексора выход которого является выходом результата устройства по модулю Р , выходы m матричных сумматоров по

модулю Р соединены с входами J I

, шифраторов кода один из Р:

J+1

соответствующиз групп, выходы которых соединены с информационными входами соответствующих мультиплексоров первой группы, выходы которых являются выходами-результата по модулю Pj , входы разрядов с (т+2)-го по (т+1+1)-й соответственно первого и второго операндов устройства соединены соответственно с входами первых и вторых дешифраторов кода один из Р соответствующей пары -H + l

рой группы. Группы выходов которых соединены соответственно с первой.

второй группой входов одноименных матричных сумматоров по модулю n-n +i зькоды которых соединены соответственно с входами формирователя.сигнала переноса с (т+2)-го по (т+1+1)-й и с входами шифраторов кода один из Р, соответствующих групп, выходы которых соединены с информационными входами соответствующих-мультиплексоров второй

группы, выходы которых являются выходами результата устройства по модулю ,., f блок местного управления содержит девять элементов И,

шесть элементов ИЛИ, причем первый информационный вход блока соединен с первьге-ги входами первого, второго и третьего элементов И, второй информационный вход блока соединен с

первыми входами четвертого, пятого и шестого И, третий информационный вход блока соединен с первыми входами седьмого, восьмого девятого элементов И, четвертый, пятый, шестой информационные входы блока местного управления являются входами соответственно отрицательного, нулевого и положительного переноса из младшего г-го разряда

устройства, четвертый информационный вход блока местного управления соединен с вторыми входами третьего, четвертого и восьмого элементов И, пятый информационный вход блока местного управления соединен с вторыми входами второго, пятого и девятого элементов И, шестой информационный вход блока местного управления соединен с вторыми входами первого и

седьмого элементов И, выход восьмого элемента И соединен с первым вхо- дом первого элемента ИЛИ, в торой вход которого соединен с выходом четвертого элемента И и первым входом

второго элемента ИЛИ,второй вход которого соединен с выходом девятого элемента И и с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом второго

элемента И и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И и с первым входом пятого элемента ИЛИ, второй вход которого

соединен с выходом первого элемента И и первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И и третьим входом третьего элемента ИЛИ, третий вход первого элемента ИЛИ соединен с выходом третьего элемента И, выход седьмого элемента И соединен с третьими входами пятого и шестого элементов ИЛИ, выходы первого, пятого, третьего элементов ИЛИ блока местного управления соединены соответственно с входами разрешения выдачи f, Е - 1, Е -1 первого мультиплексора,вькоды шестого, четвертого, второго элементов ИЛИ, первого и восьмого элементов И соединены соответственно с входами разрешения вьздачи , +1, f -1,

9031Д8

i+ 2, f- 2 мультиплексоров первой группы, выходы пятого, шестого, четвертого, второго, девятого, третьего, первого, восьмого, седьмого элементов И соединены соответственно с входами разрешения выдачи f , + 1, f-1, е -г, +г, + г -1, f+r+1,e+r-2, fc+r + 2 мультиплексоров второй группы, выходы отрицательного, нулевого и положительного переноса устройства соединены соответственно с первьм, вторым, третьим информационными входами блока местного управления.

в

fO

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования для системы передачи цифровых сигналов | 1985 |

|

SU1305884A1 |

| Устройство для сложения @ -разрядных чисел в избыточной системе счисления | 1984 |

|

SU1188731A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

| Устройство для определения момента разладки случайных процессов | 1985 |

|

SU1260973A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| @ -Ичный сумматор | 1984 |

|

SU1273925A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин высокого быстродействия. Цель изобретения - повышение быстродействия. Устройство содержит п сумматоров по модулю, каждый из которых содержит первый и второй дешифраторы двоичного кода в код один из р. (J 1,п), матричный сумматор по модулю, формирователь сигналов переноса первую группу из трех шифраторов по основанию Р , первый блок из m групп по пять шифраторов по основаниям с Р по Р , второй блок из k групп по девять шифраторов по основаниям с P„,.л ° т4.к первый мультиплексор, первую группу из m мультиплексоров, вторую группу из k мультиплексоров, блок местного управления и соответствующие связи. Это позволяет повысить быстродействие сумматора. 5 ил.

122-71 Ш IIFJI

i i 2 Л-; г-2

Фиг.3

25

26

271 2В

ВНИИПИ Заказ 7903/47 Тираж 673Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

23 130

32

Фиг. 5

| Устройство для сложения в избыточнойСиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824198A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ проверки частоты высокостабильных генераторов по передаваемым по радио образцовым частотам | 1957 |

|

SU118871A1 |

Авторы

Даты

1987-02-15—Публикация

1985-03-28—Подача