112

Изобретение относится к вычислительной технике, в частности, к полупроводниковым запоминающим устройствам.

Целью изобретения является повыше- ние быстродействия запоминающего устройства.

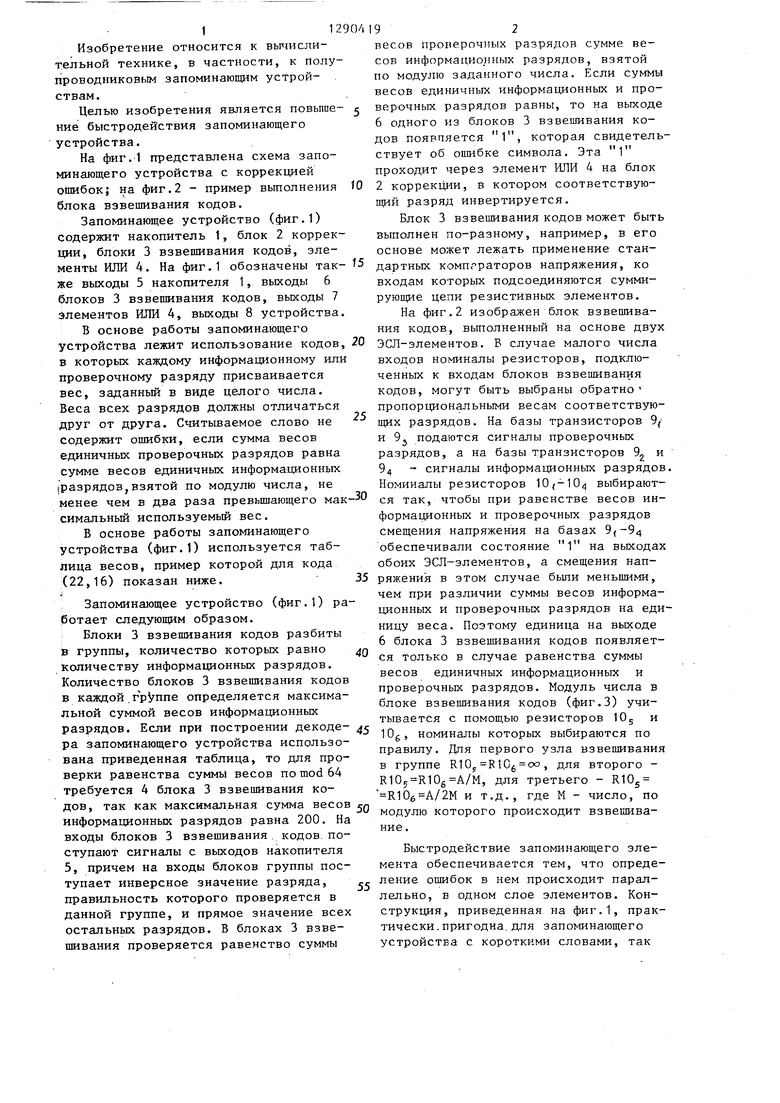

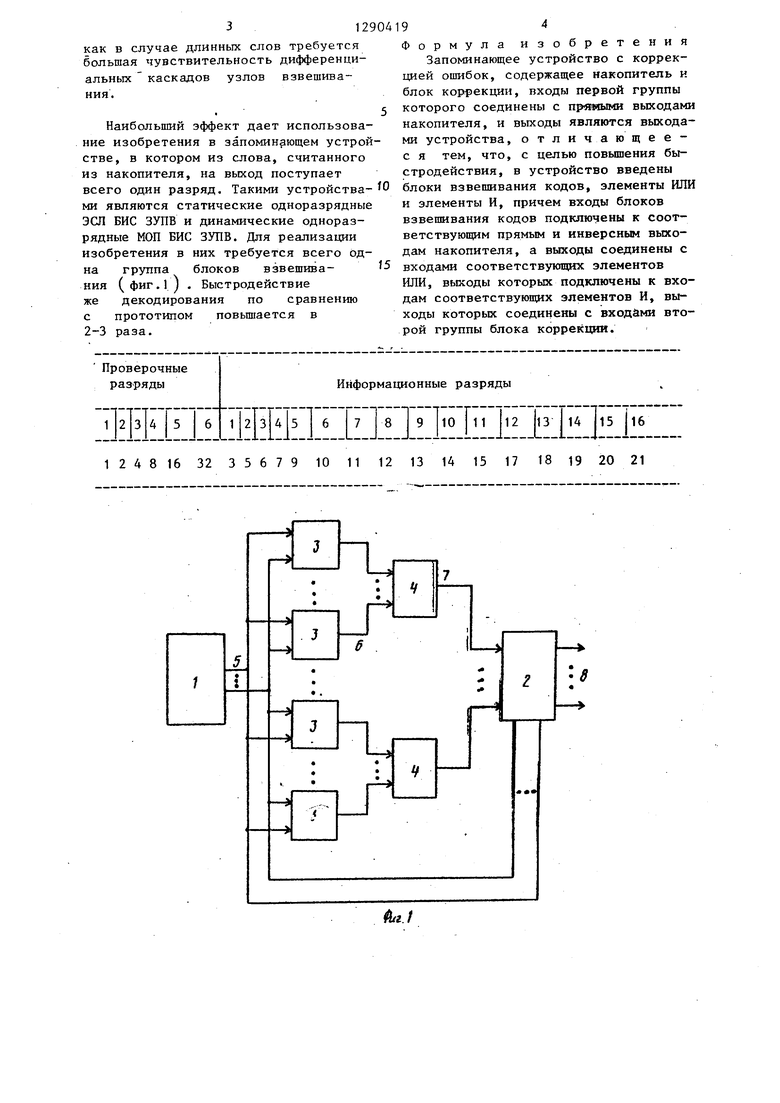

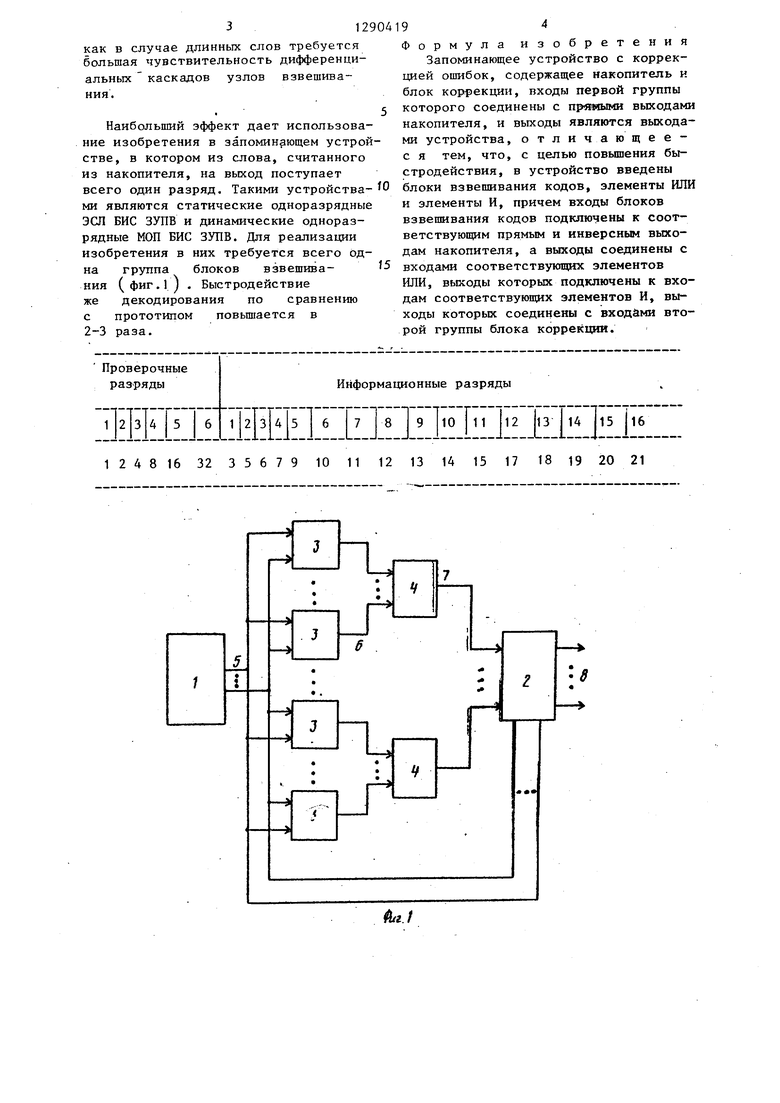

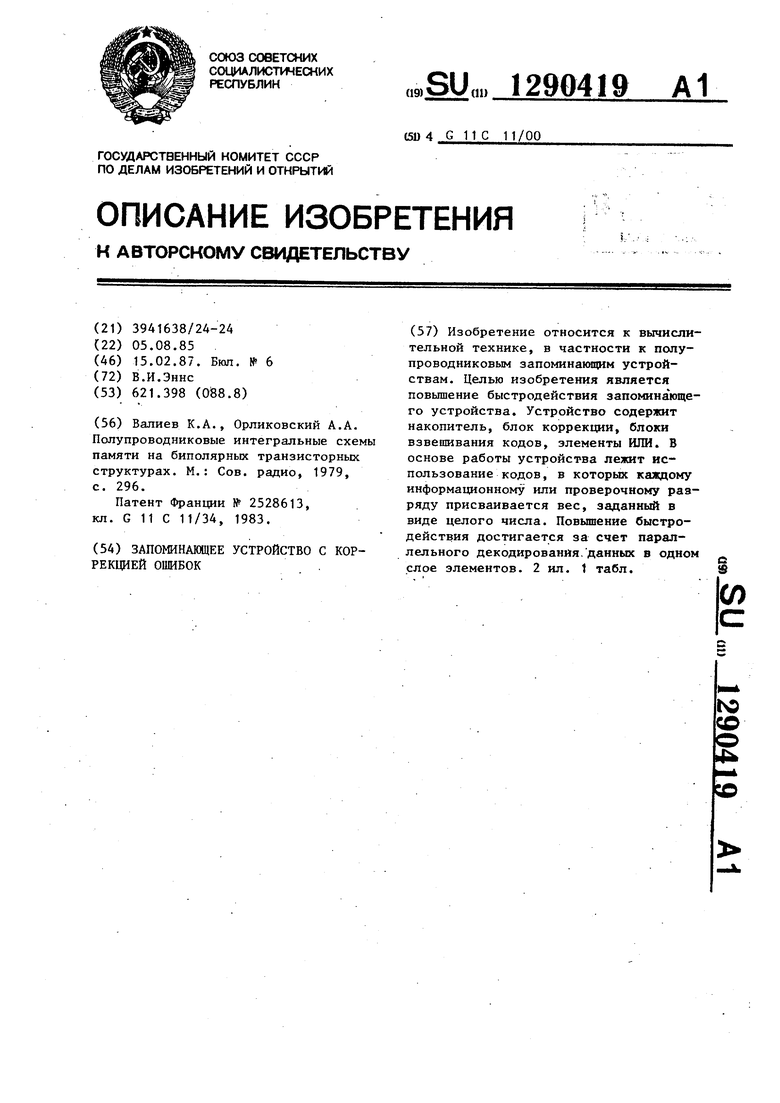

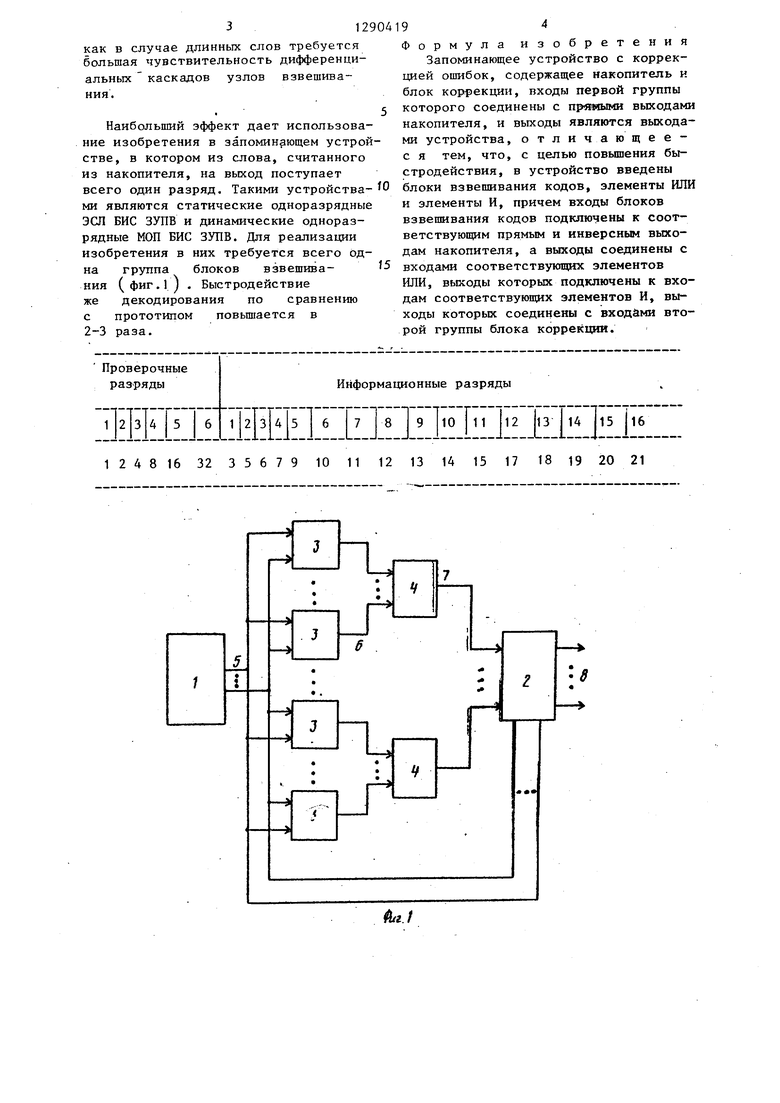

На фиг.1 представлена схема запоминающего устройства с коррекцией ошибок; на фиг.2 - пример вьтолнения блока взвешивания кодов.

Запоминающее устройство (фиг.1) содержит накопитель 1, блок 2 коррекции, блоки 3 взвещивания кодов, элементы ИЛИ 4. На фиг.1 обозначены так- же выходы 5 накопителя 1, выходы 6 блоков 3 взвешивания кодов, выходы 7 элементов ИЛИ 4, выходы 8 устройства.

В основе работы запоминающего устройства лежит использование кодов, в которых каждому информационному или проверочному разряду присваивается вес, заданный в виде целого числа. Веса всех разрядов должны отличаться друг от друга. Считываемое слово не содержит ошибки, если сумма весов единичных проверочньк разрядов равна сумме весов единичных информационных (разрядов,взятой по модулю числа, не менее чем в два раза превышающего мак симальный используемый вес.

В основе работы запоминающего устройства (фиг.1) используется таблица весов, пример которой для кода (22,16) показан ниже.

Запоминающее устройство (фиг.1) работает следующим образом.

Блоки 3 взвешивания кодов разбиты в группы, количество которых равно количеству информационных разрядов. Количество блоков 3 взвешивания кодов в каждой. г рУппе определяется максимальной суммой весов информационных разрядов. Если при построении декоде- ра запоминающего устройства использована приведенная таблица, то для проверки равенства суммы весов по mod 64 требуется 4 блока 3 взвещивания кодов, так как максимальная сумма весов информационных разрядов равна 200. На входы блоков 3 взвешивания. кодов, поступают сигналы с выходов накопителя 5, причем на входы блоков группы поступает инверсное значение разряда, правильность которого проверяется в данной группе, и прямое значение всех остальных разрядов. В блоках 3 взвешивания проверяется равенство суммы

,

25

04

j

Ю

5

20

35

05 Q

30

192

весов пропарочных разрядов сумме весов информационр1ых разрядов, взятой по модулю заданного числа. Если суммы весов единичных информационных и проверочных разрядов равны, то на выходе 6 одного из блоков 3 взвешивания кодов появляется 1, которая свидетельствует об ошибке символа. Эта 1 проходит через элемент ИЛИ 4 на блок 2 коррекции, в котором соответствую- ш;ий разряд инвертируется.

Блок 3 взвешивания кодов может быть выполнен по-разному, например, в его основе может лежать применение стандартных компграторов напряжения, ко входам которых подсоединяются сумми- цепи резистивных элементов.

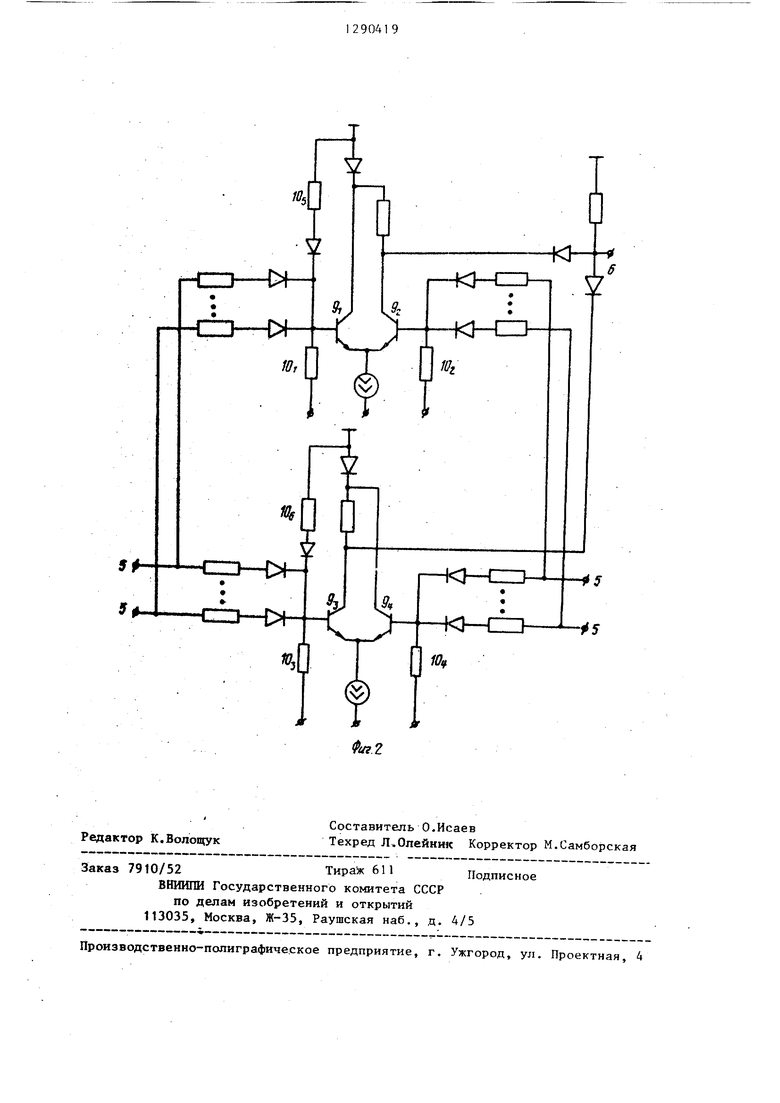

На фиг.2 изображен блок взвешивания кодов, вьшолненный на основе двух ЭСЛ-элементов. В случае малого числа входов но:миналы резисторов, подключенных к входам блоков взвешивания кодов, могут быть выбраны обратно пропорциональными весам соответствующих разрядов. На базы транзисторов 9, и 9j подаются сигналы проверочных разрядов, а на базы транзисторов 9„ и 94 сигналы информационных разрядов. Номиналы резисторов 10,-10 выбираются так, чтобы при равенстве весов информационных и проверочных разрядов смещения напряжения на базах обеспечивали состояние 1 на выходах обоих ЭСЛ-элементов, а смещения напряжения в этом случае бьши меньшими, чем при различии суммы весов информационных и проверочных разрядов на единицу веса. Поэтому единица на выходе 6 блока 3 взвешивания кодов появляется только в случае равенства суммы весов единичных информационных и проверочных разрядов. Модуль числа в блоке взвешивания кодов (фиг.З) учи

тывается с помощью резисторов 10 и lOg, номиналы которых выбираются по правилу. Для первого узла взвешивания в группе , для второго - , для третьего - R105 и т.д., где М - число, по модулю которого происходит взвешивание .

Быстродействие запоминающего элемента обеспечивается тем, что определение ошибок в нем происходит параллельно, в одном слое элементов. Конструкция, приведенная на фиг.1, практически, пригодна, для запоминающего устройства с короткими словами, так

3129

как в случае длинных слов требуется большая чувствительность дифференциальных каскадов узлов взвешивания.

Наибольший эффект дает использование изобретения в запоминающем устройстве, в котором из слова, считанного из накопителя, на выход поступает всего один разряд. Такими устройствами являются статические одноразрядные ЭСЛ БИС ЗУПВ и динамические одноразрядные МОП БИС ЗУПВ. Для реализации изобретения в них требуется всего одна группа блоков взвешива- ния ( фиг.1 . Быстродействие же декодирования по сравнению с прототипом повьш1ается в 2-3 раза.

1 2 4 8 16 32 3 5 6 7 9 10 11 12 13 14 15 17 18 19 20 21

194

Формула изобретения Запоминающее устройство с коррекцией ошибок, содержащее накопитель и блок коррекции, входы первой группы которого соединены с прмняыми выходами накопителя, и выходы являются выходами устройства, отличающее- с я тем, что, с целью повышения быстродействия, в устройство введены блоки взвешивания кодов, элементы ИЛИ и элементы И, причем входы блоков взвешивания кодов подключены к соответствующим прямым и инверсным выходам накопителя, а выходы соединены с входами соответствующих элементов ИЛИ, выходы которых подключены к входам соответствующих элементов И, выходы которых соединены с входами второй группы блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1290420A1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1336122A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство | 1981 |

|

SU972590A1 |

Изобретение относится к вычислительной технике, в частности к полупроводниковым запоминакяцим устройствам. Целью изобретения является повышение быстродействия запоминающего устройства. Устройство содержит накопитель, блок коррекции, блоки взвешивания кодов, элементы ИЛИ. В основе работы устройства лежит использование кодов, в которых каждому информационному или проверочному разряду присваивается вес, заданный в виде целого числа. Повышение быстродействия достигается за счет параллельного декодирования. данных в одном слое элементов. 2 ил. 1 табл. W С to CD О 4 ;о

g

5

Редактор К.Волощук

Составитель О.Исаев

Техред Л Олейнжс Корректор М.Самборская

Заказ 7910/52Тираж 611 Подписное

ВНИИПИ Государственного комитета СССР

По делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Валиев К.А., Орликовский А.А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Сов | |||

| радио, 1979, с | |||

| ДЖИНО-ПРЯДИЛЬНАЯ МАШИНА | 1920 |

|

SU296A1 |

| ЭЛЕКТРИЧЕСКИЙ РАЗЪЕДИНИТЕЛЬ | 2011 |

|

RU2528613C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-05—Подача