. Изобретение относится к вычислительной технике, в частности, к полупроводниковым запоминаюгцим устройствам.

.Целью изобретения является повыше ние быстродействия запоминающего устройства.

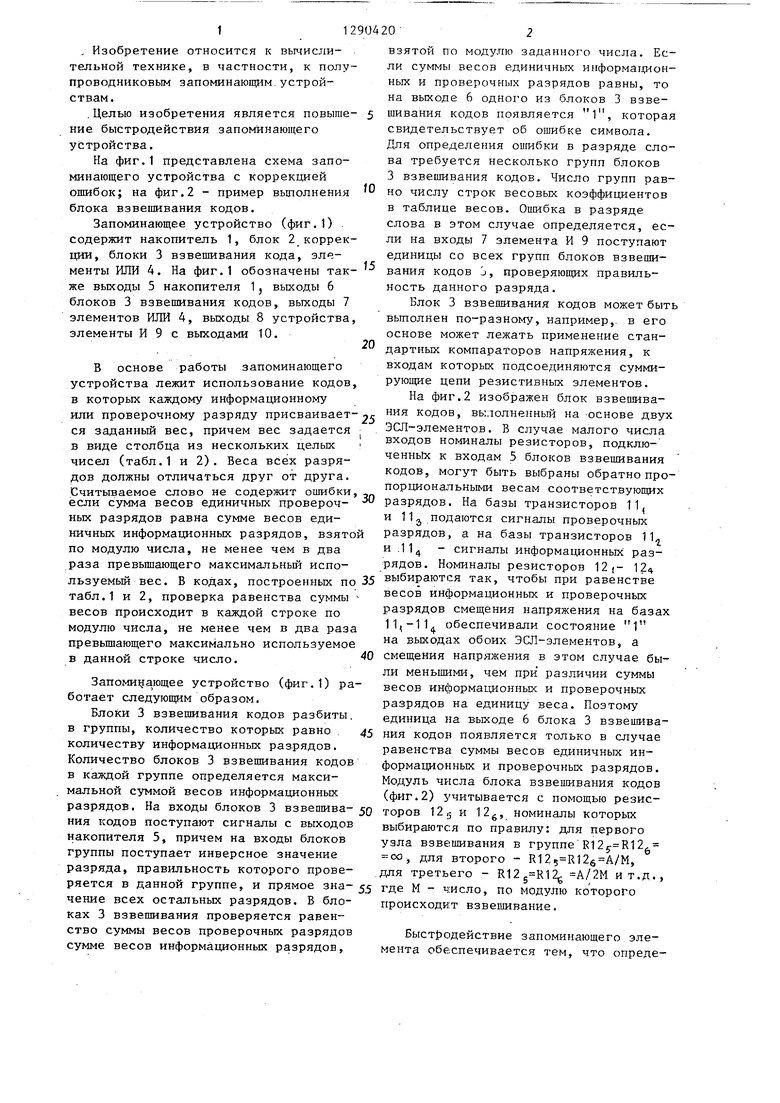

На фиг.1 представлена схема запоминающего устройства с коррекцией ошибок; на фиг.2 - пример вьшолнения блока взвешивания кодов.

Запоминающее устройство (фиг.1) , содержит накопитель 1, блок 2 коррекции, блоки 3 взвешивания кода, элементы ИЛИ 4. На фиг.1 обозначены также выходы 5 накопителя 1, выходы 6 блоков 3 взвешивания кодов, выходы 7 элементов ИЛИ 4, выходы 8 устройства, элементы И 9 с выходами 10.

- 5

fO

15

взятой по модулю заданного числа. Если суммы весов единичных ииформаи юн- ных и проверочных разрядов равны, то на выходе 6 одного из блоков 3 взвешивания кодов появляется 1, которая свидетельствует об ошибке символа. Для определения ошибки в разряде слова требуется несколько групп блоков 3 взвешивания кодов. Число групп равно числу строк весовых коэффициентов в таблице весов. Оиибка в разряде слова в этом случае определяется, если на входы 7 элемента И 9 поступают единицы со всех групп блоков взвешивания кодов J, проверяющих правильность данного разряда.

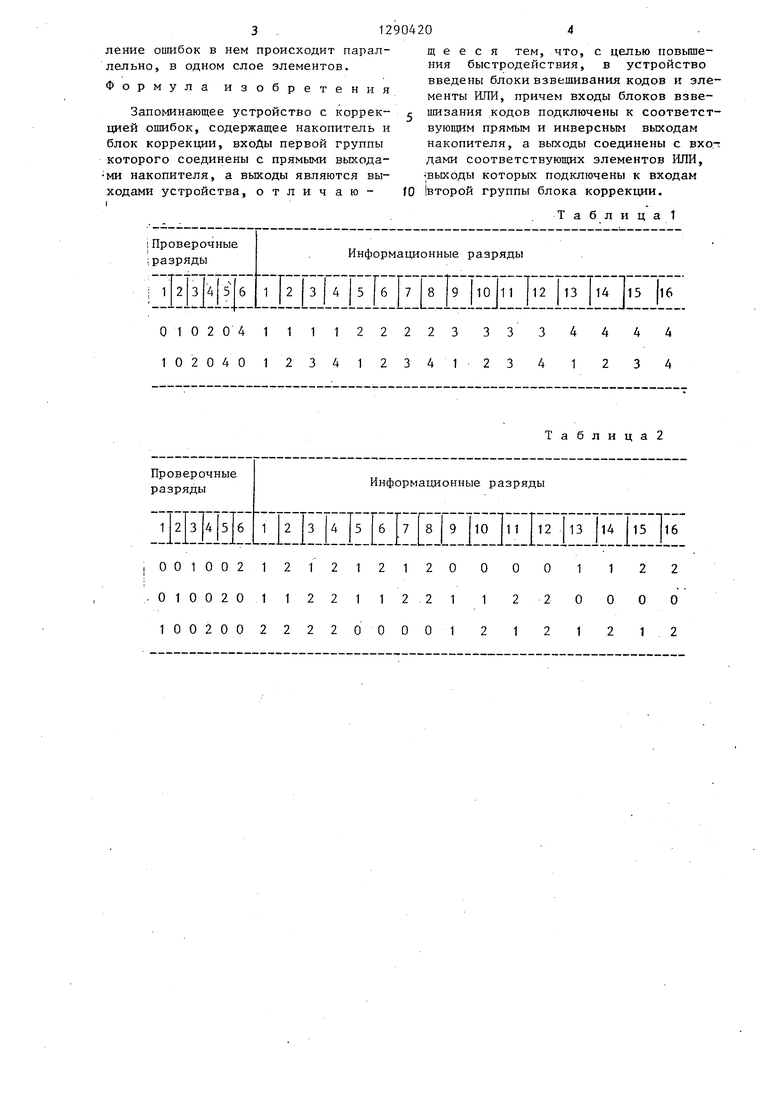

Блок 3 взвешивания кодов может быть вьшолнен по-разному, например,, в его основе может лежать применение стандартных компараторов напряжения, к входам которых подсоединяются суммирующие цепи резистивных элементов.

На фиг.2 изображен блок взвешивания кодов, выполненный на юснове двух ЭСЛ-элементов. В случае малого числа входов номиналы резисторов, подклю- ченнь х к входам 5 блоков взвешивания кодов, могут быть выбраны обратно пропорциональными весам соответствующих разрядов. На базы транзисторов 11. и llj подаются сигналы проверочных разрядов, а на базы транзисторов 11- и .1Ц - сигналы информационных разрядов. Номиналы резисторов 12(- 124

вес. В кодах, построенных „о 35 выбираются так, чтобы при равенстве 2, проверка равенства суммы есов информационньк и проверочньпс

разрядов смещения напряжения на базах 11,-11. обеспечивали состояние 1 на выходах обоих ЭСЛ-элементов, а

20

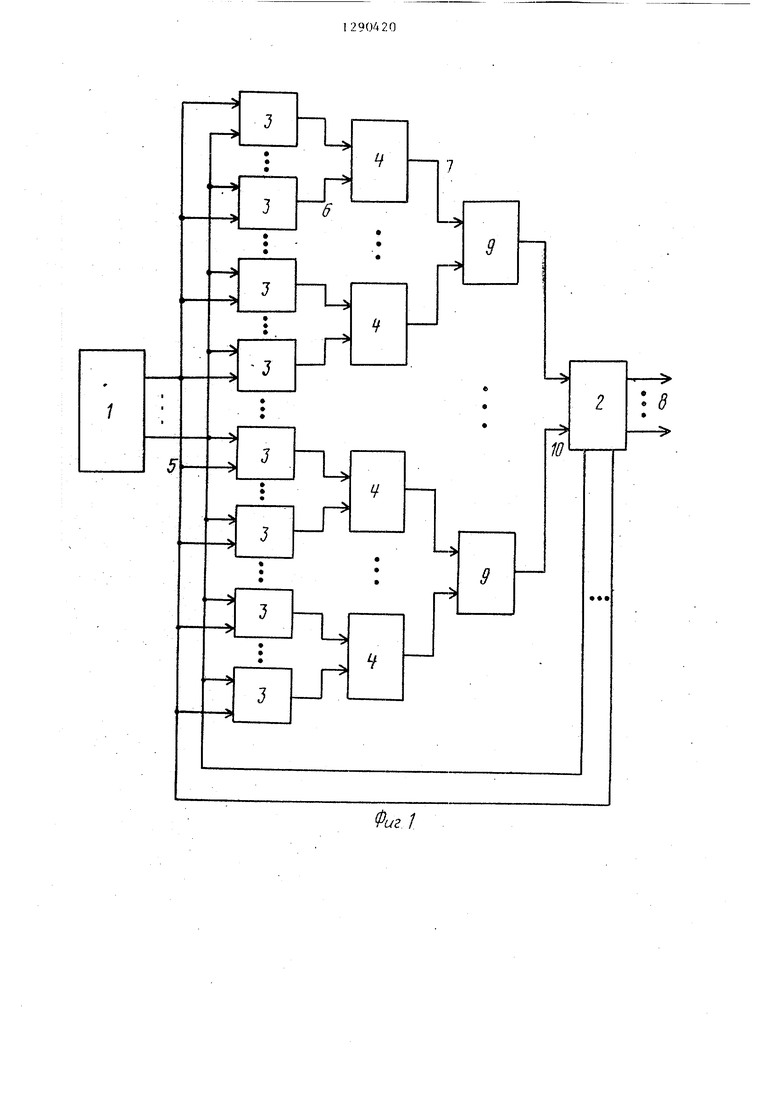

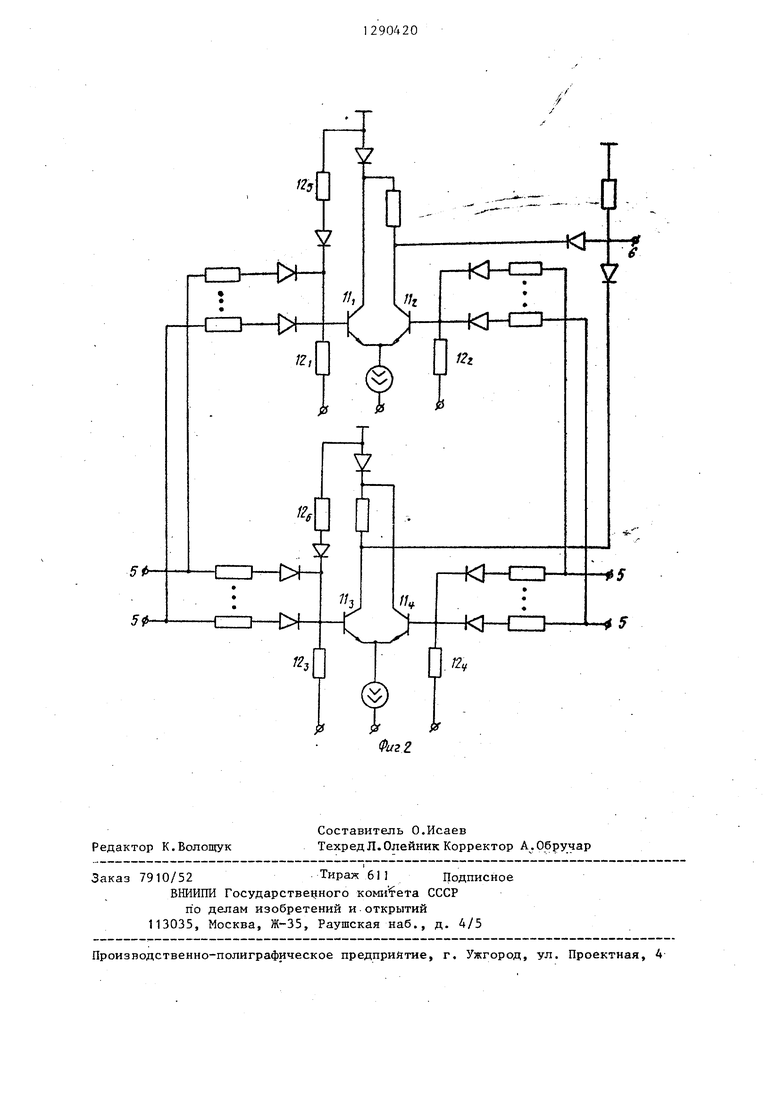

В основе работы запоминающего устройства лежит использование кодов, в которых каждому информационному или проверочному разряду присваивает- 2« ся заданньй вес, причем вес задается в виде столбца из нескольких целых чисел (табл.1 и 2). Веса всех разрядов должны отличаться друг от друга. Считываемое слово не содержит ошибки, -„ если сумма весов единичных провероч- ных разрядов равна сумме весов единичных информационных разрядов, взятой по модулю числа, не менее чем в два раза превьшающего максимальньп используемый

табл.1 и 2, проверка равенства суммы весов происходит в каждой строке по

модулю числа, не менее чем в два раза превьш1ающего максимально используемое в данной строке число.

40 смещения напряжения в этом случае были меньшими, чем при различии суммы весов информационных и проверочных разрядов на единицу веса. Поэтому единица на выходе 6 блока 3 взвешивания кодов появляется только в случае равенства суммы весов единичных информационных и проверочных разрядов. Модуль числа блока взвешивания кодов (фиг. 2) 5 читывается с помощью резис- На входы блоков 3 взвешива-50 торов 12,; и 12g, номиналы которых

Запомица ющее устройство (фиг.1) работает следующим образом.

Блоки 3 взвешивания кодов разбиты. в группы, количество которых равно 45 количеству информационных разрядов. Количество блоков 3 взвешивания кодов в каждой группе определяется максимальной суммой весов информационных разрядов

ния кодов поступают сигналы с выходов накопителя 5, причем на входы блоков группы поступает инверсное значение разряда, правильность которого провевыбираются по правилу: для первого узла взвешивания в группе 8125- К12 --са, для второго - , Д/1Я третьего - А/2М и т.д.,

выбираются по правилу: для первог узла взвешивания в группе 8125- К1 --са, для второго - , Д/1Я третьего - А/2М и т

ряется в данной группе, и прямое зна- 55 где М - число, по модулю ко торого

чение всех остальных разрядов. В блоках 3 взвешивания проверяется равенство суммы весов проверочных разрядов сумме весов информационных разрядов,

происходит взвешивание.

Быстродействие запоминающего эл мента обеспечивается тем, что опр

- 5

выбираются по правилу: для первого узла взвешивания в группе 8125- К12 --са, для второго - , Д/1Я третьего - А/2М и т.д.,

где М - число, по модулю ко торого

происходит взвешивание.

Быстродействие запоминающего элемента обеспечивается тем, что опредеФормула изобретен и

312904204

ление ошибок в нем происходит парал- щ е е с я тем, что, с целью повыше- лельно, в одном слое элементов. ния быстродействия, в устройство

введены блоки взвешивания кодов и элементы ИЛИ, причем входы блоков взве- Запоминающее устройство с коррек- с шизания кодов подключены к соответст- цией ошибок, содержащее накопитель и прямым и инверсным выходам блок коррекции, вхоДы первой группы накопителя, а выходы соединены с вхо.-: которого соединены с прямыми выхода- дами соответствующих элементов ИЛИ, ми накопителя, а выходы являются вы- выходы которых подключены к входам

ходами устройства, отличаю- fO второй группы блока коррекции, I

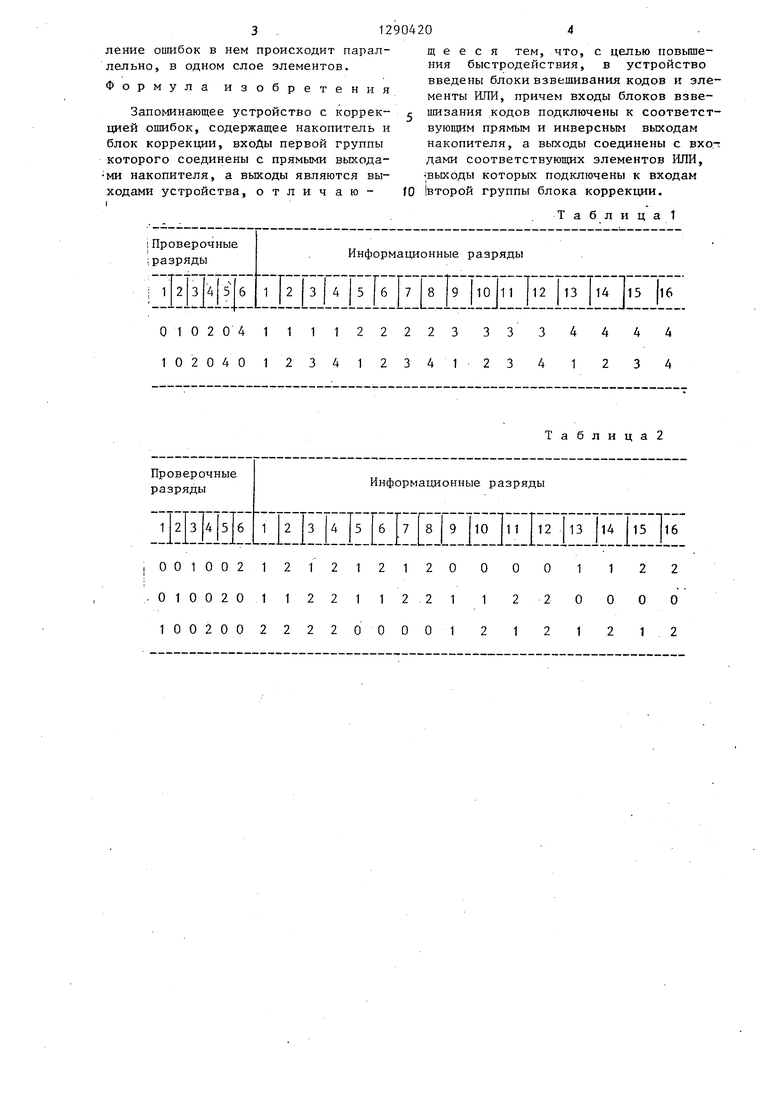

Таблица 1

010204111122223 33 3 4 4 4 А 10204012341234123 4 1 2 3 4

|001002121212120 О О О 1 1 2 2

.010020112211221 1 22 О О О О

100200222200001 2 1 2 1 2 12

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1290419A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1377917A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1336122A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

Изобретение отйосится к вычисли- ;тельной технике, в частности к полупроводниковым запоминающим устройствам. Целью изобретения является повышение быстродействия запоминающего устройства. Устройство содержит накопитель, блок коррекции, блоки взвеши-. вания кодов, элементы ИЛИ, элементы И. В основе работы устройства лежит использование кодов, в которых каждому информационному или проверочному разряду присваивается вес, заданный в виде столбца из нескольких, целых чисел. Повышение быстродействия достигается за счет параллельного деко дирования данных в одном слое элементов. 2 ил. 2 табл. СО

Редактор К.Волощук

Составитель О.Исаев ТехредЛ.Олейник Корректор А.Обручар

Заказ 7910/52Тираж 611 Подписное

ВНИИПИ Государстве1|ного KOMti -eTa СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

| Валиев К.А., Орликовский А.А.- Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Сов-, радио, 1979, с | |||

| ДЖИНО-ПРЯДИЛЬНАЯ МАШИНА | 1920 |

|

SU296A1 |

| ЭЛЕКТРИЧЕСКИЙ РАЗЪЕДИНИТЕЛЬ | 2011 |

|

RU2528613C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-05—Подача