1

Изобретение относится к вычислительной технике и может найти при- ;менение в вьтислительных системах ,для повьшения достоверности информа- ции, хранимой в памяти.

Цель изобретения - повышение надежности устройства.

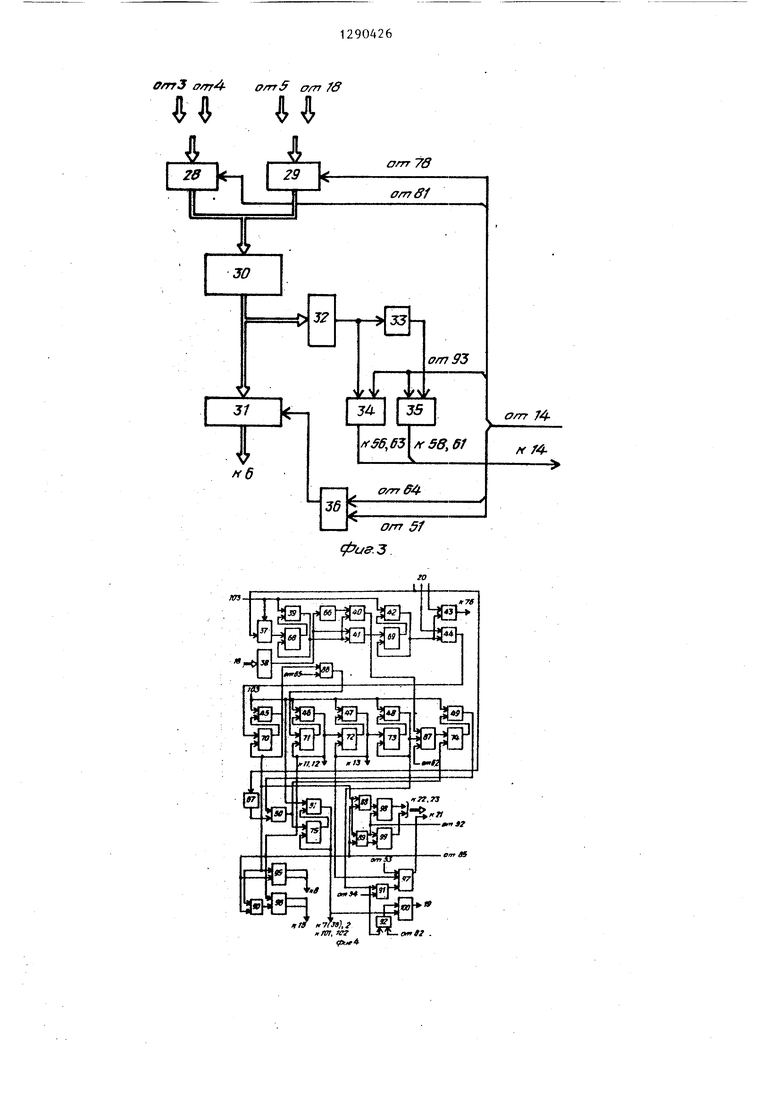

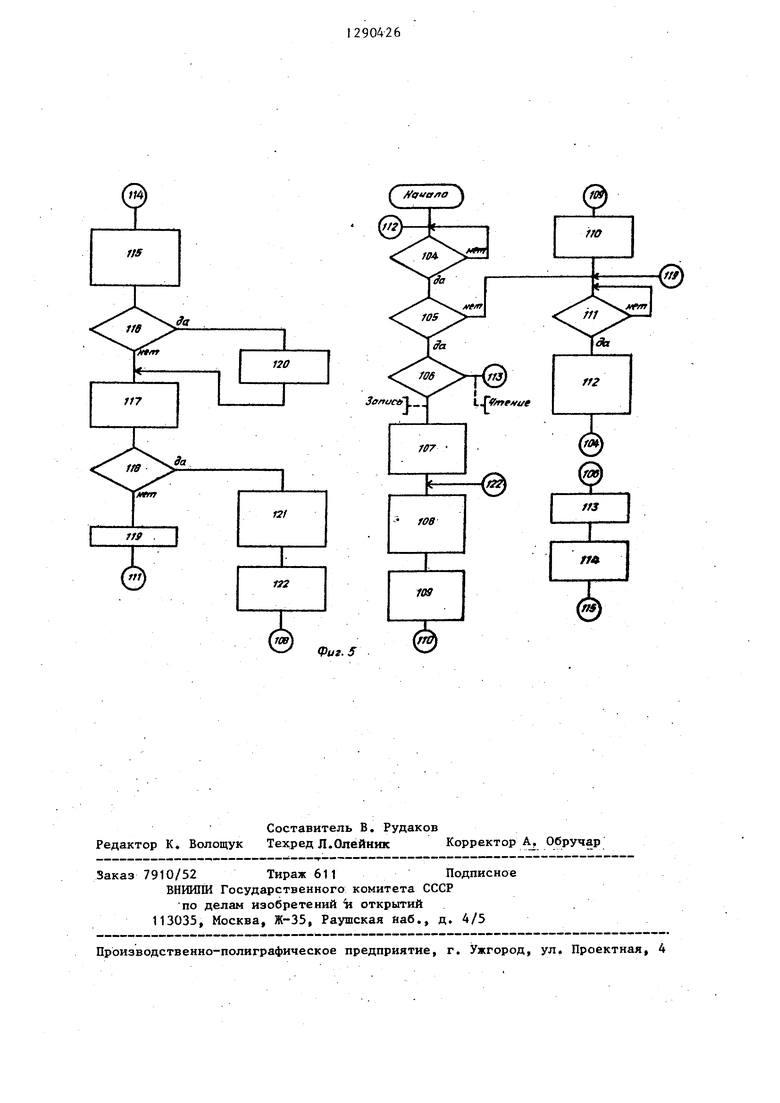

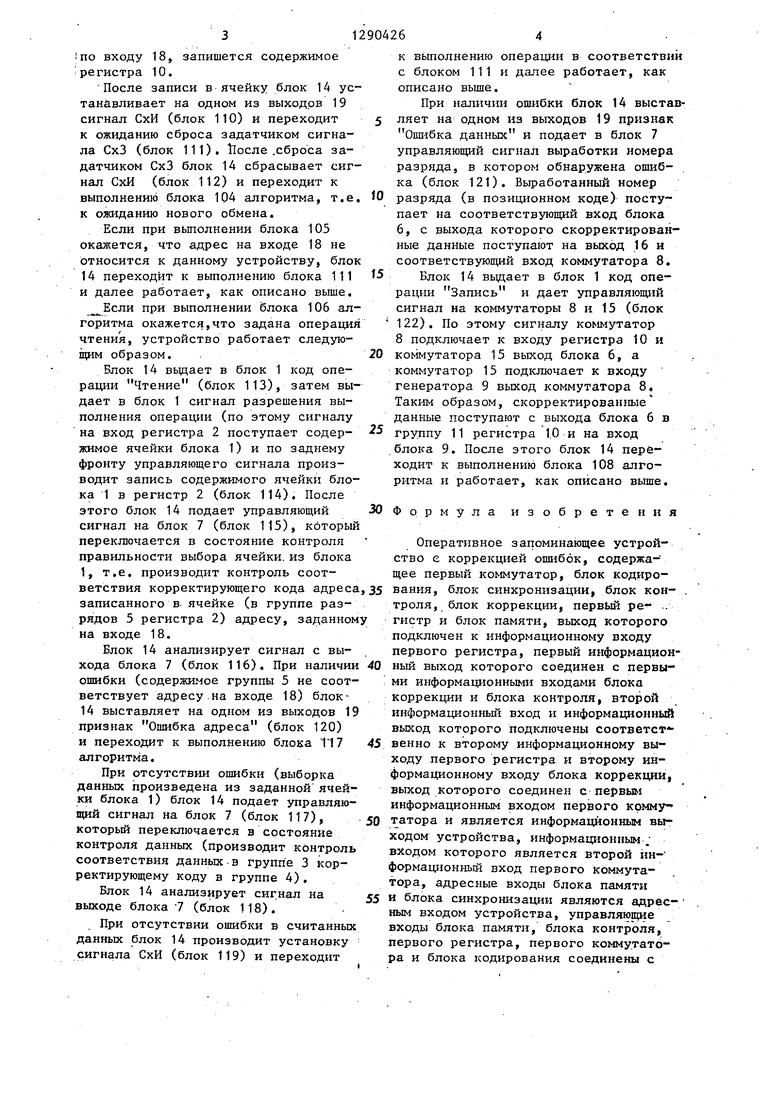

На фиг. 1 приведена функциональная схема устройства} на фиг. 2 - функциональная схема блока памяти, (вариант построения); на фиг. 3 - функциональная схема блока контроля (вариант построения); на фиг. 4 - то же, блока синхронизации; на фиг.5 - алгоритм работы устройства.

Устройство содержит (фиг. 1) блок 1 памяти, первый регистр 2 с группами разрядов 3-5 для хранения соответственно данных, корректирующего кода данных и корректирующего кода адреса, блок 6 коррекции, блок 7 контроля, первый коммутатор 8, блок 9 кодирования, второй регистр 10 данных с группами разрядов 11-13 для хранения соответственно данных, корректирующего кода данных и корректирующего кода адреса, блок 14 синхронизации, второй коммутатор 15, информационные выход 16 и вход 17, адресньй вход 18, управляющие выход 19 и вход 20.

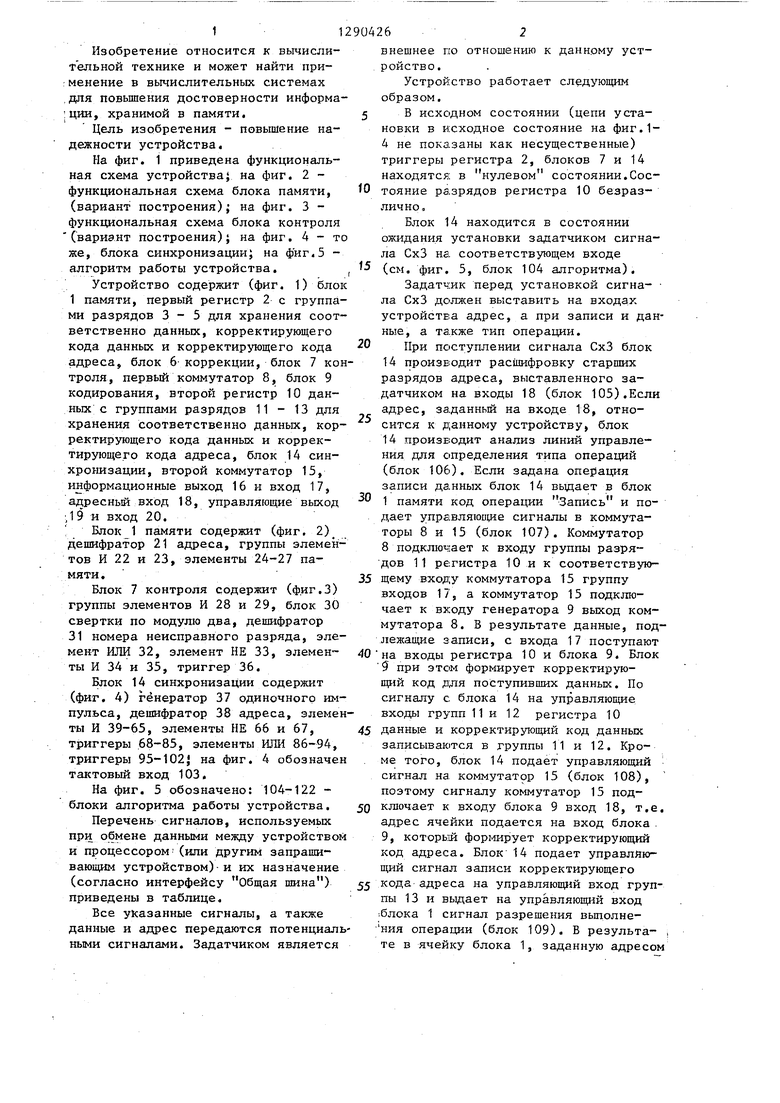

Блок 1 памяти содержит (фиг, 2) дешифратор 21 адреса, группы элементов Е 22 к 23, элементы 24-27 памяти.

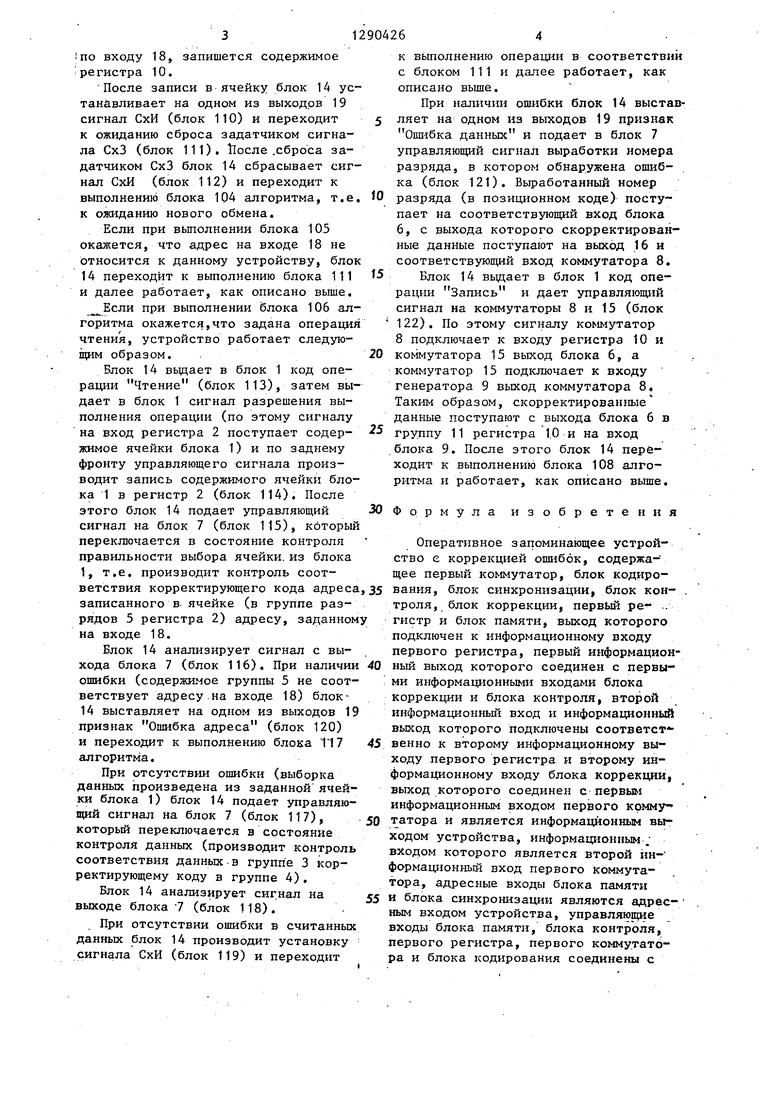

Блок 7 контроля содержит (ф.иг.З) группы элементов И 28 и 29, блок 30 свертки по модулю два, дешифратор 31 номера неисправного разряда, элемент ИЛИ 32, элемент НЕ 33, элементы И 34 и 35, триггер 36.

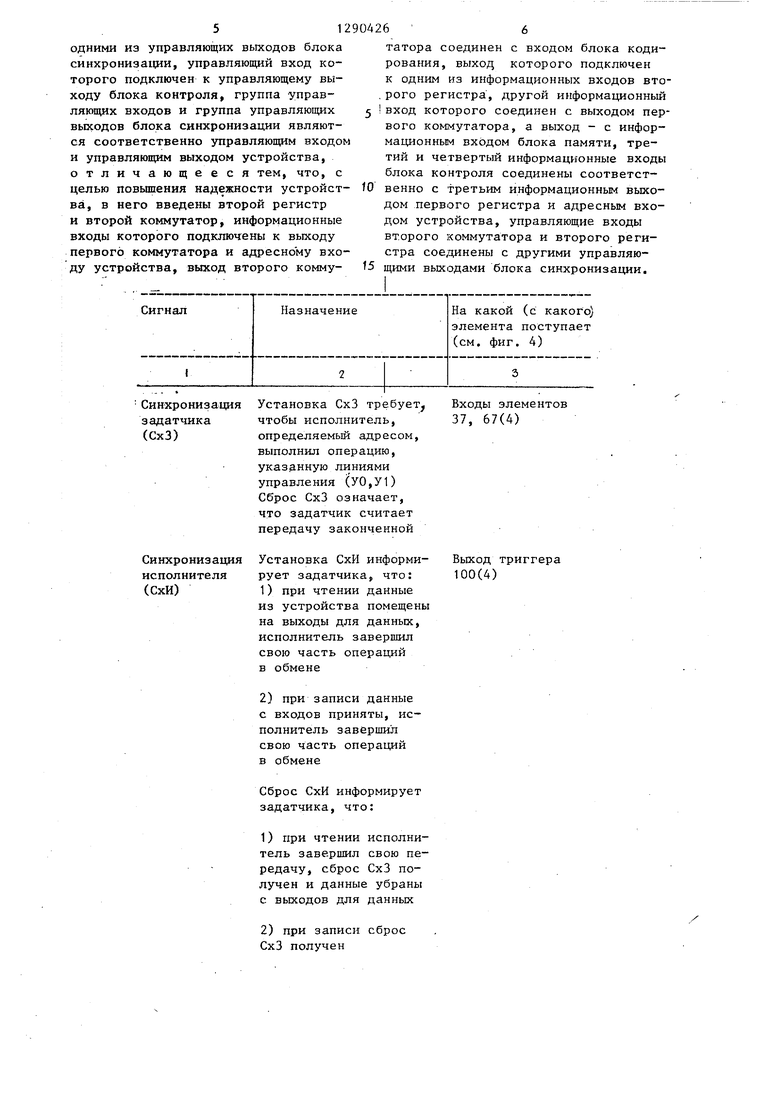

Блок 14 синхронизации содержит (фиг. 4) генератор 37 одиночного импульса, дешифратор 38 адреса, элементы И 39-65, элементы НЕ 66 и 67, триггеры 68-85, элементы ИЛИ 86-94, триггеры 95-1023 на фиг. 4 обозначен тактовый вход 103.

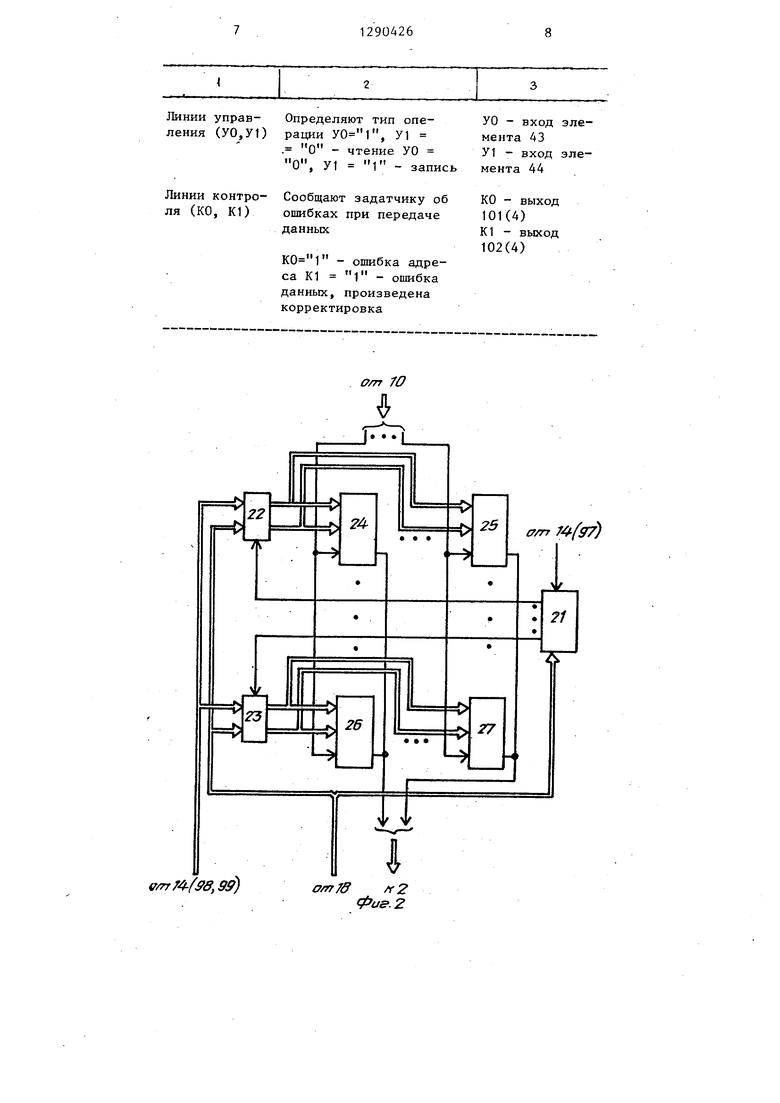

На фиг. 5 обозначено: 104-122 - блоки алгоритма работы устройства.

Перечень сигналов, используемьк при обмене данными между устройством и процессором (или другим запрашивающим устройством)-и их назначение (согласно интерфейсу Общая шина) приведены в таблице.

Все указанные сигналы, а также данные и адрес передаются потенциальными сигналами. Задатчиком является

15

20

25

12904262

внешнее по отношению к данному устройство.

Устройство работает следующим образом.

5 В исходном состоянии (цепи установки в исходное состояние на фиг.1- 4 не показаны как несущественные) триггеры регистра 2, блоков 7 и 14 находятся в нулевом состоянии.СосtO тояние разрядов регистра 10 безразлично.

Блок 14 находится в состоянии ожидания установки задатчиком сигнала СхЗ не. соответствующем входе (см. фиг. 5, блок 104 алгоритма).

Задатчик перед установкой сигна- ла СхЗ должен выставить на входах устройства адрес, а при записи и данные, а та,кже тип операции.

При поступлении сигнала СхЗ блок 14 производит расшифровку старших разрядов адреса, выставленного задатчиком на входы 18 (блок 105).Если адрес, заданный на входе 18, относится к данному устройству, блок 14 производит анализ линий управления для определения типа операций (блок 106). Если задана операция записи данных блок 14 выдает в блок

1 памяти код операции Запись и подает управляюирге сигналы в коммутаторы 8 и 15 (блок 107). Коммутатор 8 подключает к входу группы разрядов 11 регистра 10 и к соответствую35 щему входу коммутатора 15 группу входов 17, а коммутатор 15 подключает к входу генератора 9 выход коммутатора 8. В результате данные, подлежащие записи, с входа 17 поступают

40 на входы регистра 10 и блока 9. Блок 9 при этом формирует корректирующий код для поступивших данных. По сигналу с блока 14 на управляющие входы групп 11 и 12 регистра 10

45 данные и корректирующий код данных записываются в группы 11 и 12. Кроме того, блок 14 подает управляющий сигнал на коммутатор 15 (блок 108), поэтому сигналу коммутатор 15 под50 ключает к входу блока 9 вход 18, т.е. адрес ячейки подается на вход блока . 9, которьш формирует корректирующий код адреса. Блок 14 подает управляющий сигнал записи корректирующего

55 кода адреса на управляющий вход группы 13 и вьздает на yпpaвляющliй вход :блока 1 сигнал разрешения выполне- ния операции (блок 109). В результа- , те в ячейку блока 1, заданную адресом

I по входу 18, запишется содержимое регистра 10.

После записи в ячейку блок 14 устанавливает на одном из выходов 19 сигнал СхИ (блок 110) и переходит к ожиданию сброса задатчиком сигнала СхЗ (блок 111). 11осле .сброса задатчиком СхЗ блок 14 сбрасывает сигнал СхИ (блок 112) и переходит к выполнению блока 104 алгоритма, т.е. к ожиданию нового обмена.

Если при вьшолнении блока 105 окажется, что адрес на входе 18 не относится к данному устройству, блок 14 переходит к выполнению блока 111 и далее работает, как описано вьше.

Если при выполнении блока 106 алгоритма окажется,что задана операция чтения, устройство работает следующим образом. .

Блок 14 вьщает в блок 1 код операции Чтение (блок 113), затем выдает в блок 1 сигнал разрешения выполнения операции (по этому сигналу на вход регистра 2 поступает содер- жимое ячейки блока 1) и по заднему фронту управляющего сигнала производит запись содержимого ячейки блока 1 в регистр 2 (блок 114). После этого блок 14 подает управляющий сигнал на блок 7 (блок 115), который переключается в состояние контроля правильности выбора ячейки, из блока 1, т.е. производит контроль соответствия корректирующего кода адреса записанного в ячейке (в группе разрядов 5 регистра 2) адресу, заданном на входе 18.

Блок 14 анализирует сигнал с выхода блока 7 (блок 116). При наличии ошибки (содержимое группы 5 не соответствует адресу.на входе 18) блок- 14 выставляет на одном из выходов 19 признак Ошибка адреса (блок 120) и переходит к выполнению блока Т17 алгоритма.

При отсутствии ошибки (выборка данных произведена из заданной ячейки блока 1) блок 14 подает управляющий сигнал на блок 7 (блок 117), который переключается в состояние контроля данных (производит контроль соответствия данных.в группе 3 корректирующему коду в группе 4).

Блок 14 анализирует сиг.нал на выходе блока 7 (блок 118).

, При отсутствии ошибки в считанных данных блок 14 производит установку сигнала СхИ (блок 119) и переходит

к выполнению операции в соответствии с блоком 111 и далее работает, как описано выше.

При наличии ошибки блок 14 выставляет на одном из выходов 19 признак Ошибка данных и подает в блок 7 управляющий сигнал выработки номера разряда, в котором обнаружена ошибка (блок 121). Вьфаботанный номер разряда (в позиционном коде) поступает на соответствующий вход блока 6, с выхода которого скорректированные данные поступают на выход 16 и соответствующий вход коммутатора 8. Блок 14 выдает в блок 1 код операции Запись и дает управляющий сигнал на коммутаторы 8 и 15 (блок 122). По этому сигналу коммутатор 8 подключает к входу регистра 10 и коммутатора 15 выход блока б, а коммутатор 15 подключает к входу генератора 9 выход коммутатора 8. Таким образом, скорректированные данные поступают с выхода блока 6 в группу 11 регистра 1.0 и на вход блока 9. После этого блок 14 переходит к выполнению блока 108 алгоритма и работает, как описано выше.

Формула изобретения

Оперативное запоминающее устройство е коррекцией ошибок, содержа- щее первый коммутатор, блок кодирования, блок синхронизации, блок кон- . троля, блок коррекции, первый ре- .. гистр и блок памяти, выход которого подключен к информационному входу первого регистра, первый информационный выход которого соединен с первы- ми информационными входами блока коррекции и блока контроля, второй информационньпЧ вход и информационный выход которого подключены соответст - венно к второму информационному выходу первого регистра и второму информационному входу блока коррекции, выход которого соединен с первым информационным входом первого комму татора и является информационным выходом устройства, информационным J входом которого является второй нн- ормационный вход первого коммутаора, адресные входы блока памяти блока синхронизации являются адрес- ым входом устройства, управляющие ходы блока памяти, блока контроля, ервого регистра, первого коммутатоа и блока кодирования соединены с

одними из управляющих выходов блока синхронизации, управляющий вход которого подключен к управляющему выходу блока контроля, группа управляющих входов и группа управляющих выходов блока синхронизации являются соответственно управляющим входом и управляющим выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй регистр и второй коммутатор, информационные входы которого подключены к выходу первого коммутатора и адресному входу устройства, выход второго коммуизация

ка

изация

теля

Установка СхЗ требует, чтобы исполнитель, определяемый адресом, выполнил операцию, указанную линиями управления (УО,У1) Сброс СхЗ означает, что задатчик считает передачу законченной

Установка СхИ информирует задатчика, что:

1)при чтении данные из устройства помещены на выходы для данных, исполнитель завершил свою часть операций

в обмене

2)при записи данные с входов приняты, исполнитель завершил свою часть операций

в обмене

Сброс СхИ информирует задатчика, что:

1)при чтении исполнитель завершил свою передачу, сброс СхЗ получен и данные убраны с выходов для данных

2)при записи сброс СхЗ получен

татора соединен с входом блока кодирования, выход которого подключен к одним из информационных входов вто- .рого регистра, другой информационный

вход которого соединен с выходом первого ком)мутатора, а выход - с инфор- мационньву входом блока памяти, третий и четвертый информационные входы блока контроля соединены соответственно с третьим информационным выходом первого регистра и адресным входом устройства, управляющие входы второго коммутатора и второго регистра соединены с другими управляющими выходами блока синхронизации.

Входы элементов 37, 67(4)

Выход триггера 100(4)

X

управ- Определяют тип опе- (УО,У1) рации , У1 . О - чтение УО

О, У1

1 - запи

Сообщают задатчику об ошибках при передаче данных

- ошибка адреса К1 1 - ошибка данных, произведена корректировка

ь

УО - вход элемента 43 У1 - вход элемента 44

КО - выход

101(4)

К1 - выход

102(4)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Устройство для преобразования гистограмм яркостей | 1987 |

|

SU1548799A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для управления обменом процессора с памятью | 1988 |

|

SU1667087A1 |

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

Изобретение относится к вычислительной технике и может найти применение в вычислительных системах для повышения достоверности информации, хранимой в памяти. Цель изобретения - повышение надежности устройства - достигается за счет осуще- ствления контроля соответствия адреса считанной ячейки запоминаклдего устройства заданному адресу.Устройство содержит блок 1 памяти, два регистра 2 и 10 с группами разрядов для хранения данных, корректи- .рующего кода данньк и корректирующего кода адреса, коммутаторы 8 и 15, блок 9 кодирования, блок 7 контроля, блок 6 коррекции и блок 14 синхронизации. 5 ил., 1 табл. -(8 79 20 (Л

ff/7r74-fffff, 99)

о/гт7& ff2 фиа.2

)

ff/ггУ ff/rr4- от 5 /7/77 Л

l U

1

фие. J

ч a /,7f3),f игт, fcf

Фиг. 5

3fffe/e,

Составитель В. Рудаков Редактор К. Волощук Техред Л.Олейник Корректор А Обручар

Заказ 7910/52 Тираж 611Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений открытий 113035, Москва, Ж-35, Раушская йаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для тестовой проверки памяти | 1978 |

|

SU744577A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-09-05—Подача