Изобретение относится к цифровой вычислительной технике, в частности к устройствам для сопряжения с памятью.

Целью изобретения является расширение функциональных возможностей устройства за счет автоматической настройки устройства на формат информационной посылки.

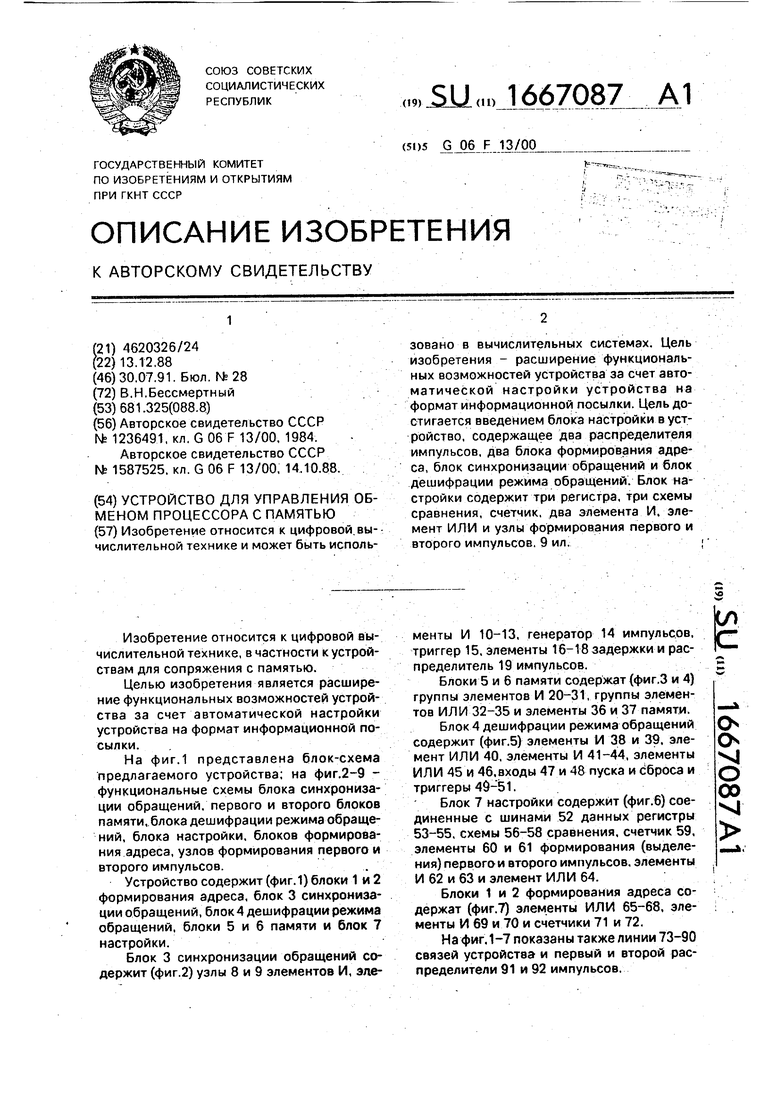

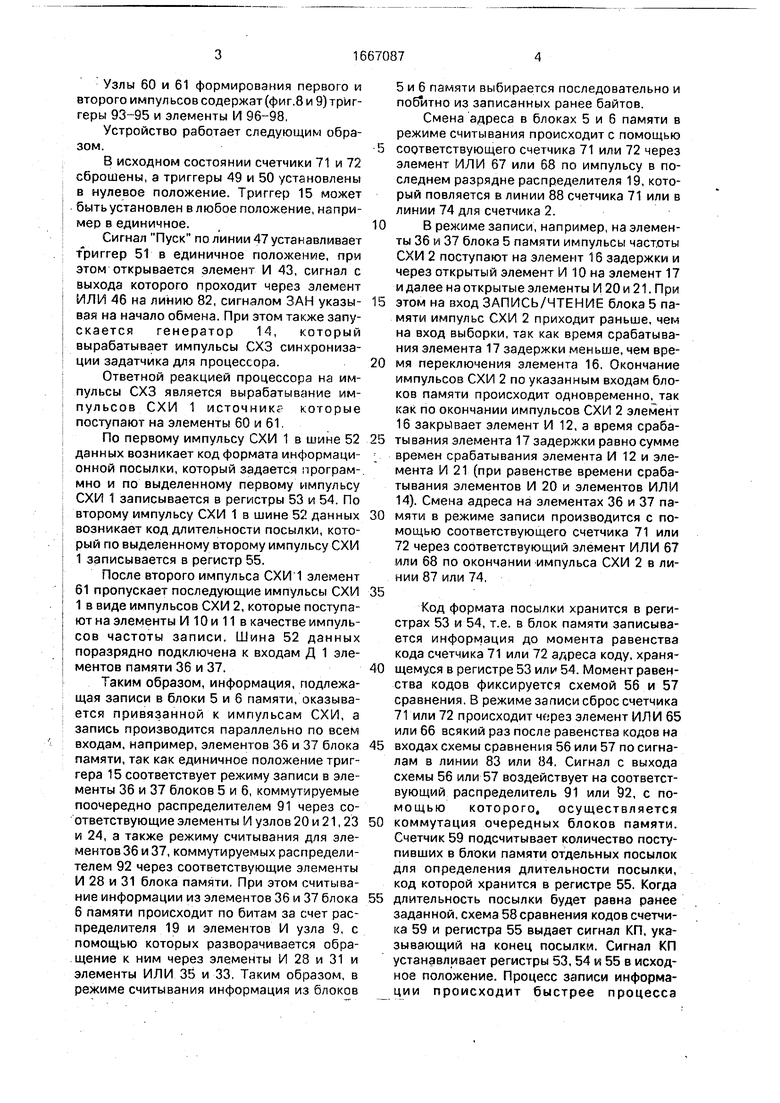

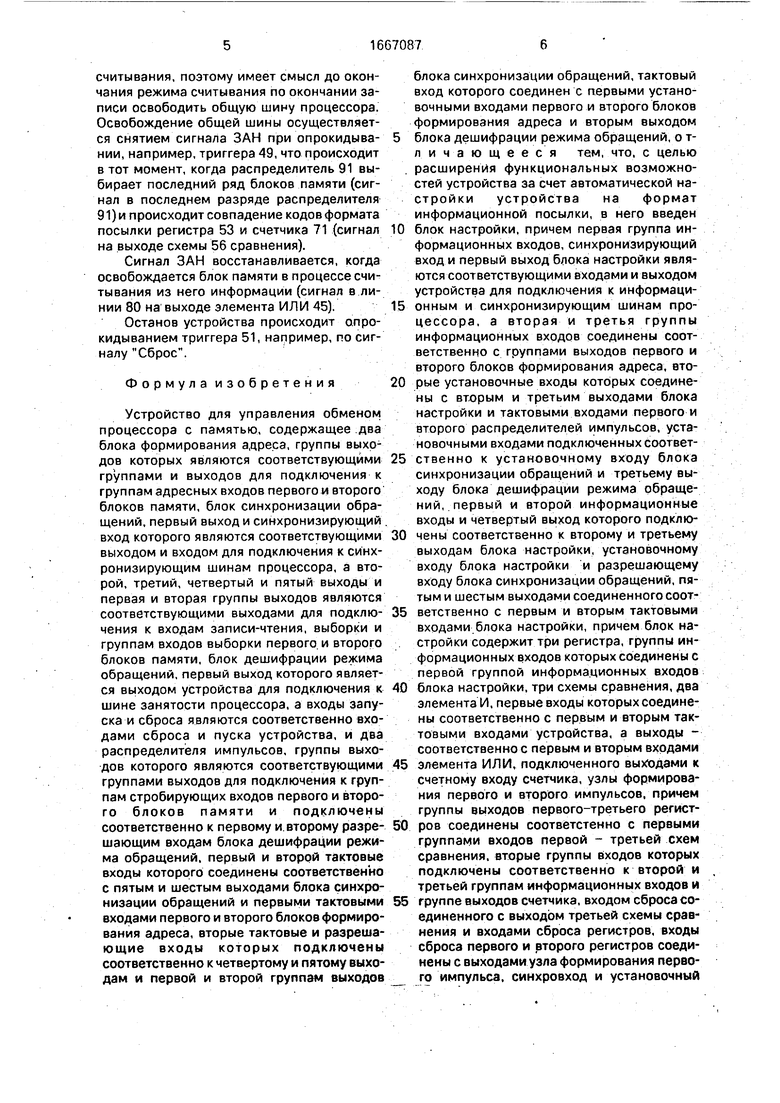

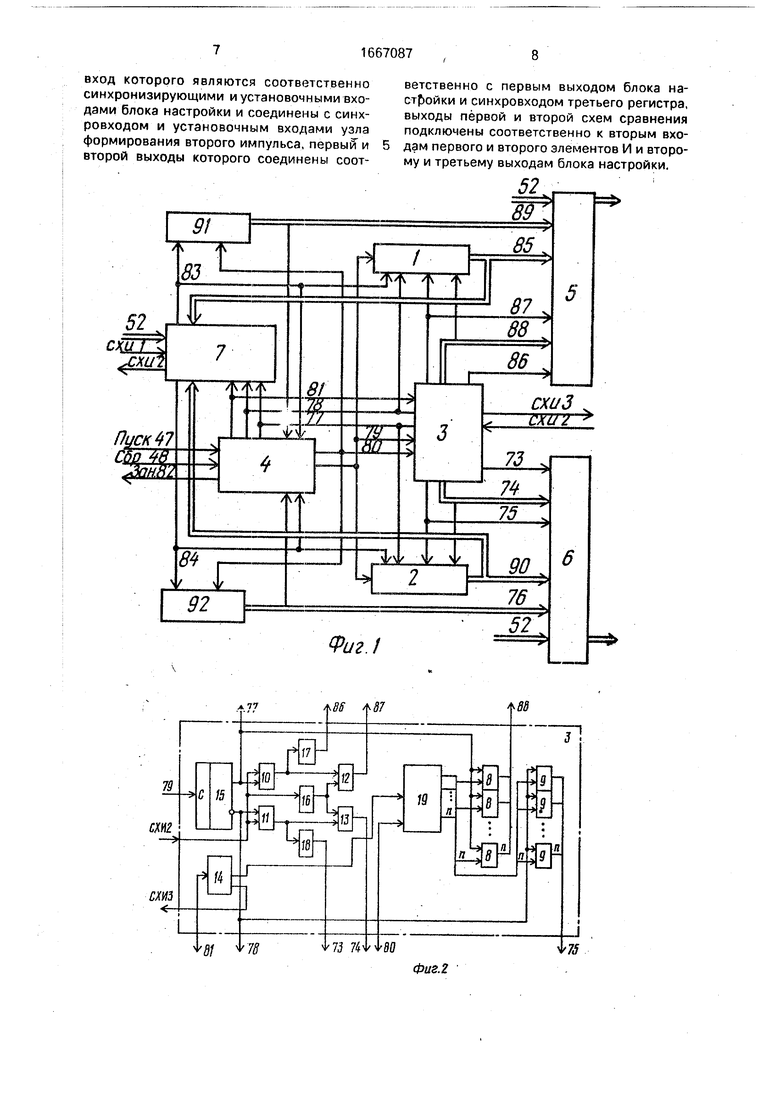

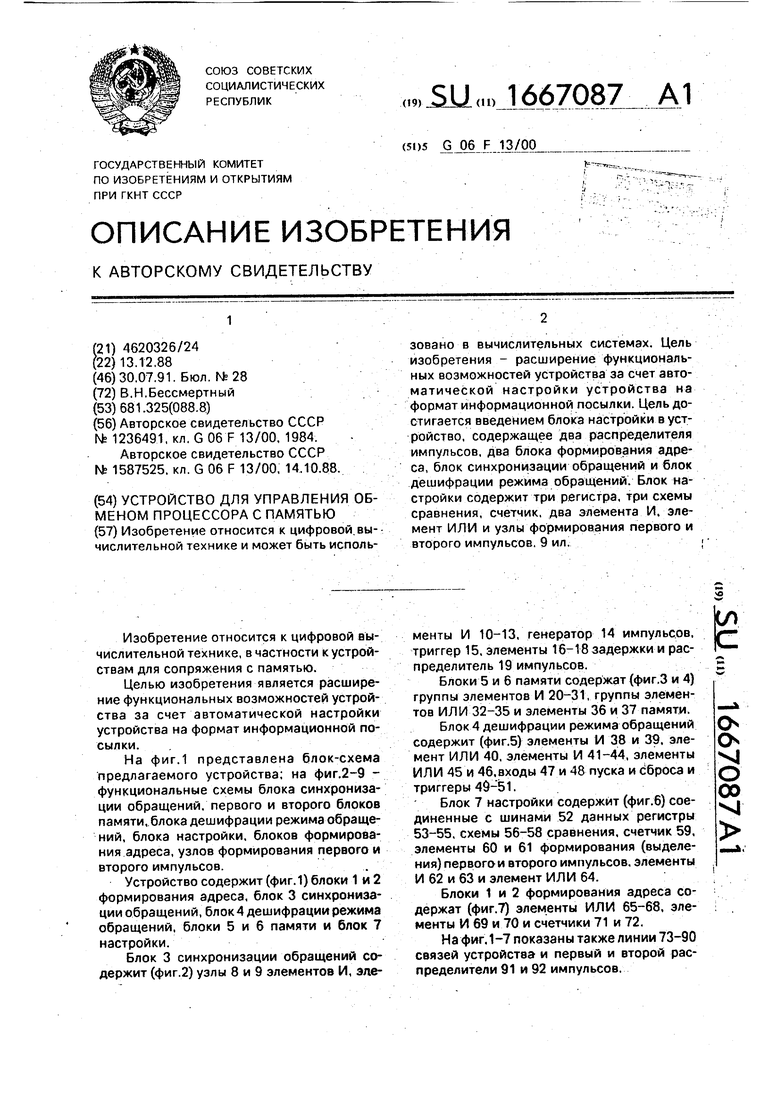

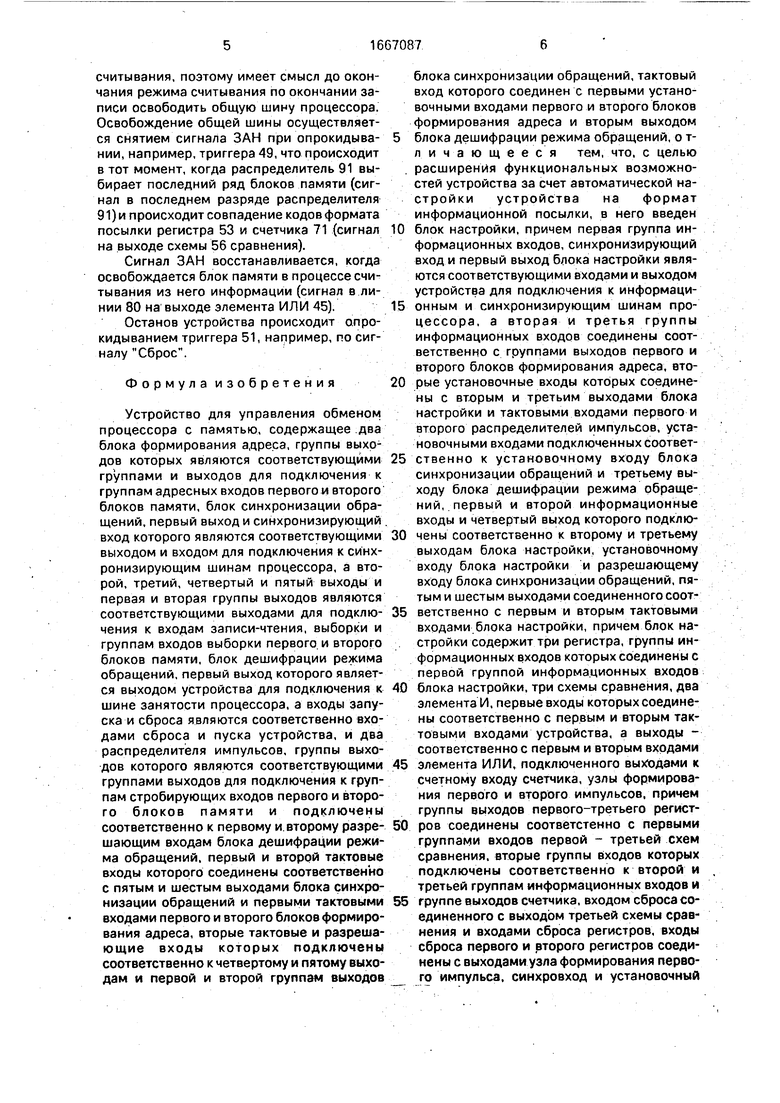

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2-9 - функциональные схемы блока синхронизации обращений, первого и второго блоков памяти, блока дешифрации режима обращений, блока настройки, блоков формирования адреса, узлов формирования первого и второго импульсов.

Устройство содержит (фиг.1) блоки 1 и 2 формирования адреса, блок 3 синхронизации обращений, блок 4 дешифрации режима обращений, блоки 5 и 6 памяти и блок 7 настройки.

Блок 3 синхронизации обращений содержит (фиг.2) узлы 8 и 9 элементов И, элементы И 10-13, генератор 14 импульсов, триггер 15. элементы 16-18 задержки и распределитель 19 импульсов.

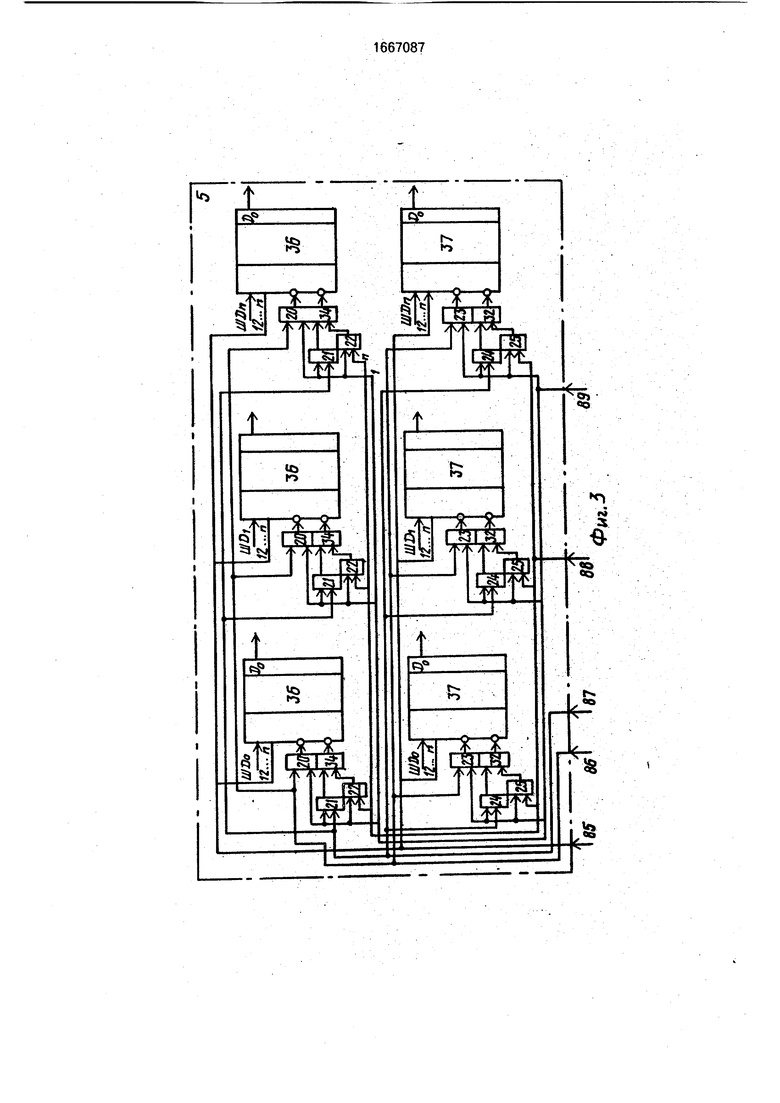

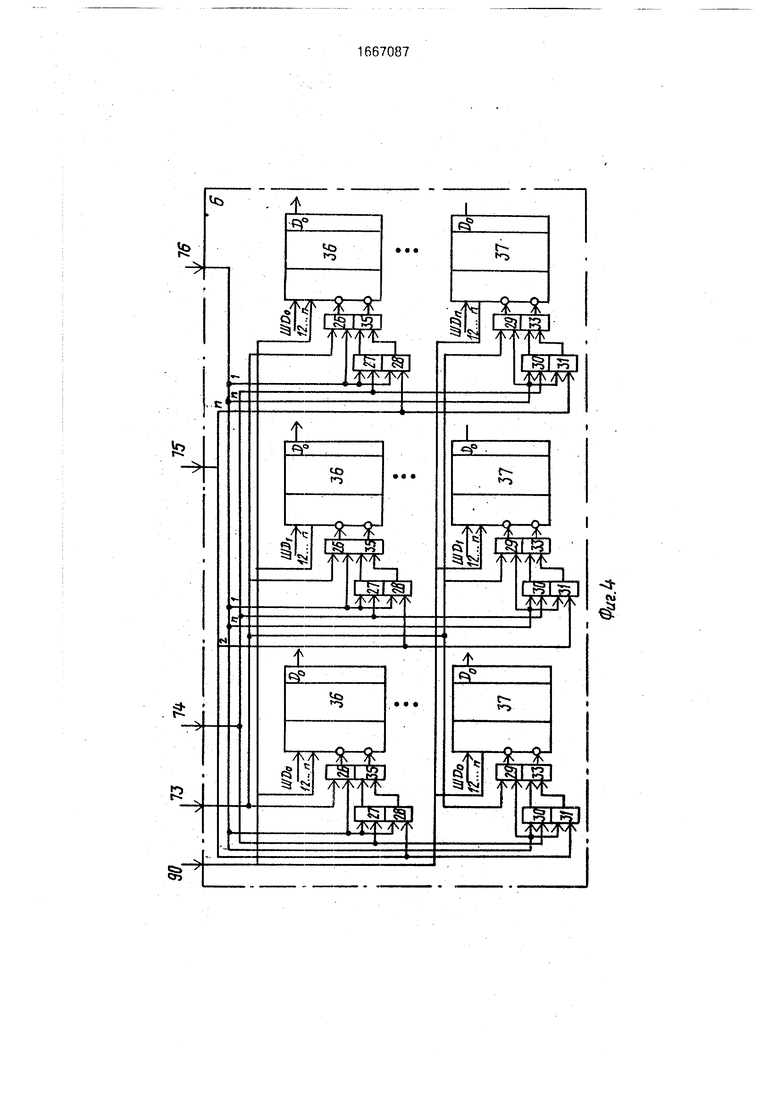

Блоки 5 и 6 памяти содержат (фиг.З и 4) группы элементов И 20-31, группы элементов ИЛИ 32-35 и элементы 36 и 37 памяти.

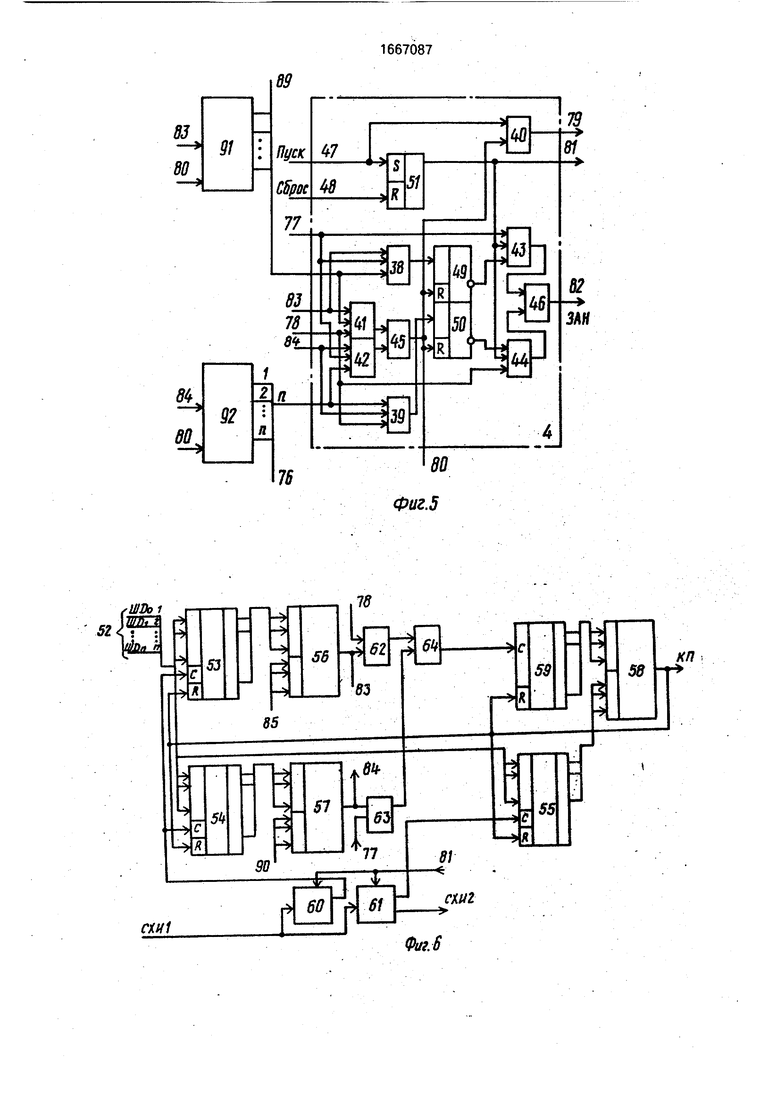

Блок 4 дешифрации режима обращений содержит (фиг.5) элементы И 38 и 39, элемент ИЛИ 40, элементы И 41-44, элементы ИЛИ 45 и 46,входы 47 и 48 пуска и сброса и триггеры 49-51.

Блок 7 настройки содержит (фиг.6) соединенные с шинами 52 данных регистры 53-55, схемы 56-58 сравнения, счетчик 59. элементы 60 и 61 формирования (выделения) первого и второго импульсов, элементы И 62 и 63 и элемент ИЛИ 64.

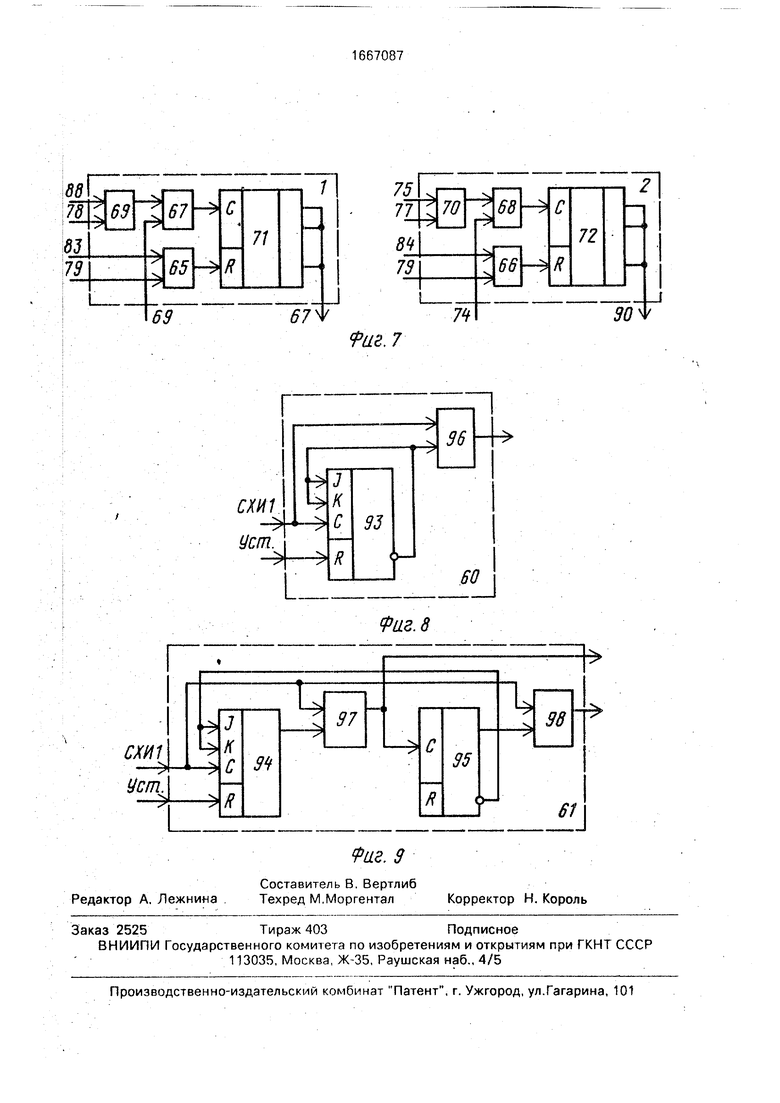

Блоки 1 и 2 формирования адреса содержат (фиг.7) элементы ИЛИ 65-68, элементы И 69 и 70 и счетчики 71 и 72.

На фиг. 1 -7 показаны также линии 73-90 связей устройства и первый и второй распределители 91 и 92 импульсов.

Ё

О

о

VI

О 00 VI

Узлы 60 и 61 формирования первого и второго импульсов содержат (фиг.8 и 9) триггеры 93-95 и элементы И 96-98.

Устройство работает следующим образом.

В исходном состоянии счетчики 71 и 72 сброшены, а триггеры 49 и 50 установлены в нулевое положение. Триггер 15 может быть установлен в любое положение, например в единичное.

Сигнал Пуск по линии 47 устанавливает триггер 51 в единичное положение, при этом открывается элемент И 43, сигнал с выхода которого проходит через элемент ИЛИ 46 на линию 82, сигналом ЗАН указывая на начало обмена. При этом также запу- скается генератор 14, который вырабатывает импульсы СХЗ синхронизации задатчика для процессора.

Ответной реакцией процессора на импульсы СХЗ является вырабатывание импульсов СХИ 1 источник; которые поступают на элементы 60 и 61

По первому импульсу СХИ 1 в шине 52 данных возникает код формата информационной посылки, который задается программно и по выделенному первому импульсу СХИ 1 записывается в регистры 53 и 54. По второму импульсу СХИ 1 в шине 52 данных возникает код длительности посылки, который по выделенному второму импульсу СХИ 1 записывается в регистр 55.

После второго импульса СХИ 1 элемент 61 пропускает последующие импульсы СХИ 1 в виде импульсов СХИ 2, которые поступают на элементы И 10 и 11 в качестве импульсов частоты записи. Шина 52 данных поразрядно подключена к входам Д 1 элементов памяти 36 и 37.

Таким образом, информация, подлежащая записи в блоки 5 и 6 памяти, оказывается привязанной к импульсам СХИ, а запись производится параллельно по всем входам, например, элементов 36 и 37 блока памяти, так как единичное положение триггера 15 соответствует режиму записи в элементы 36 и 37 блоков 5 и 6, коммутируемые поочередно распределителем 91 через соответствующие элементы И узлов 20 и 21,23 и 24, а также режиму считывания для элементов 36 и 37, коммутируемых распределителем 92 через соответствующие элементы И 28 и 31 блока памяти. При этом считывание информации из элементов 36 и 37 блока 6 памяти происходит по битам за счет распределителя 19 и элементов И узла 9, с помощью которых разворачивается обращение к ним через элементы И 28 и 31 и элементы ИЛИ 35 и 33. Таким образом, в режиме считывания информация из блоков

5 и 6 памяти выбирается последовательно и побитно из записанных ранее байтов.

Смена адреса в блоках 5 и 6 памяти в режиме считывания происходит с помощью соответствующего счетчика 71 или 72 через элемент ИЛИ 67 или 68 по импульсу в последнем разрядне распределителя 19, который повляется в линии 88 счетчика 71 или в линии 74 для счетчика 2.

0В режиме записи, например, на элементы 36 и 37 блока 5 памяти импульсы частоты СХИ 2 поступают на элемент 16 задержки и через открытый элемент И 10 на элемент 17 и далее на открытые элементы И 20 и 21. При

5 этом на вход ЗАПИСЬ/ЧТЕНИЕ блока 5 памяти импульс СХИ 2 приходит раньше, чем на вход выборки, так как время срабатывания элемента 17 задержки меньше, чем вре0 мя переключения элемента 16. Окончание импульсов СХИ 2 по указанным входам блоков памяти происходит одновременно, так как по окончании импульсов СХИ 2 элемент 16 закрывает элемент И 12, а время сраба5 тывания элемента 17 задержки равно сумме времен срабатывания элемента И 12 и элемента И 21 (при равенстве времени срабатывания элементов И 20 и элементов ИЛИ 14). Смена адреса на элементах 36 и 37 па0 мяти в режиме записи производится с помощью соответствующего счетчика 71 или 72 через соответствующий элемент ИЛИ 67 или 68 по окончании импульса СХИ 2 в линии 87 или 74.

5

Код формата посылки хранится в регистрах 53 и 54, т.е. в блок памяти записывается информация до момента равенства кода счетчика 71 или 72 адреса коду, храня0 щемуся в регистре 53 или 54. Момент равенства кодов фиксируется схемой 56 и 57 сравнения. В режиме записи сброс счетчика 71 или 72 происходит чорез элемент ИЛИ 65 или 66 всякий раз после равенства кодов на

5 входах схемы сравнения 56 или 57 по сигналам в линии 83 или 84. Сигнал с выхода схемы 56 или 57 воздействует на соответствующий распределитель 91 или 92, с помощью которого, осуществляется

0 коммутация очередных блоков памяти. Счетчик 59 подсчитывает количество поступивших в блоки памяти отдельных посылок для определения длительности посылки, код которой хранится в регистре 55. Когда

5 длительность посылки будет равна ранее заданной, схема 58 сравнения кодов счетчика 59 и регистра 55 выдает сигнал КП, указывающий на конец посылки. Сигнал КП устанавливает регистры 53, 54 и 55 в исходное положение. Процесс записи информации происходит быстрее процесса

считывания, поэтому имеет смысл до окончания режима считывания по окончании записи освободить общую шину процессора. Освобождение общей шины осуществляется снятием сигнала ЗАН при опрокидывании, например, триггера 49, что происходит в тот момент, когда распределитель 91 выбирает последний ряд блоков памяти (сигнал в последнем разряде распределителя 91) и происходит совпадение кодов формата посылки регистра 53 и счетчика 71 (сигнал на выходе схемы 56 сравнения).

Сигнал ЗАН восстанавливается, когда освобождается блок памяти в процессе считывания из него информации (сигнал в линии 80 на выходе элемента ИЛИ 45).

Останов устройства происходит опрокидыванием триггера 51, например, го сигналу Сброс.

Формула изобретения

Устройство для управления обменом процессора с памятью, содержащее два блока формирования адреса, группы выходов которых являются соответствующими группами и выходов для подключения к группам адресных входов первого и второго блоков памяти, блок синхронизации обращений, первый выход и синхронизирующий вход которого являются соответствующими выходом и входом для подключения к синхронизирующим шинам процессора, а второй, третий, четвертый и пятый выходы и первая и вторая группы выходов являются соответствующими выходами для подключения к входам записи-чтения, выборки и группам входов выборки первого и второго блоков памяти, блок дешифрации режима обращений, первый выход которого является выходом устройства для подключения к шине занятости процессора, а входы запуска и сброса являются соответственно входами сброса и пуска устройства, и два распределителя импульсов, группы выходов которого являются соответствующими группами выходов для подключения к группам стробирующих входов первого и второго блоков памяти и подключены соответственно к первому и второму разрешающим входам блока дешифрации режима обращений, первый и второй тактовые входы которого соединены соответственно с пятым и шестым выходами блока синхронизации обращений и первыми тактовыми входами первого и второго блоков формирования адреса, вторые тактовые и разрешающие входы которых подключены соответственно к четвертому и пятому выходам и первой и второй группам выходов

блока синхронизации обращений, тактовый вход которого соединен с первыми установочными входами первого и второго блоков формирования адреса и вторым выходом

блока дешифрации режима обращений, о т- личающееся тем, что, с целью расширения функциональных возможностей устройства за счет автоматической настройки устройства на формат информационной посылки, в него введен

0 блок настройки, причем первая группа информационных входов, синхронизирующий вход и первый выход блока настройки являются соответствующими входами и выходом устройства для подключения к информаци5 онным и синхронизирующим шинам процессора, а вторая и третья группы информационных входов соединены соответственно с группами выходов первого и второго блоков формирования адреса, вто0 рые установочные входы которых соединены с вторым и третьим выходами блока настройки и тактовыми входами первого и второго распределителей импульсов, установочными входами подключенных соответ5 ственно к установочному входу блока синхронизации обращений и третьему выходу блока дешифрации режима обращений, первый и второй информационные входы и четвертый выход которого подклю0 чены соответственно к второму и третьему выходам блока настройки, установочному входу блока настройки и разрешающему входу блока синхронизации обращений, пятым и шестым выходами соединенногосоот5 ветственно с первым и вторым тактовыми входами блока настройки, причем блок настройки содержит три регистра, группы информационных входов которых соединены с первой группой информационных входов

0 блока настройки, три схемы сравнения, два элемента И, первые входы которых соединены соответственно с первым и вторым тактовыми входами устройства, а выходы - соответственное первым и вторым входами

5 элемента ИЛИ, подключенного выходами к счетному входу счетчика, узлы формирования первого и второго импульсов, причем группы выходов первого-третьего регист0 ров соединены соответстенно с первыми группами входов первой - третьей схем сравнения, вторые группы входов которых подключены соответственно к второй и третьей группам информационных входов и

5 группе выходов счетчика, входом сброса соединенного с выходом третьей схемы сравнения и входами сброса регистров, входы сброса первого и второго регистров соединены с выходами узла формирования первого импульса, синхровход и установочный

вход которого являются соответственно синхронизирующими и установочными входами блока настройки и соединены с синх- ровходом и установочным входами узла формирования второго импульса, первый и второй выходы которого соединены соответственно с первым выходом блока настройки и синхровходом третьего регистра, выходы первой и второй схем сравнения подключены соответственно к вторым вхо- дам первого и второго элементов И и второму и третьему выходам блока настройки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Устройство для сопряжения процессора с памятью | 1990 |

|

SU1798788A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для управления обменом процессора с памятью | 1989 |

|

SU1603393A2 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах. Цель изобретения - расширение функциональных возможностей устройства за счет автоматической настройки устройства на формат информационной посылки. Цель достигается введением блока настройки в устройство, содержащее два распределителя импульсов, два блока формирования адреса, блока синхронизации обращений и блока дешифрации режима обращений. Блок настройки содержит три регистра, три схемы сравнения, счетчик, два элемента И, элемент ИЛИ и узлы формирования первого и второго импульсов. 9 ил.

Фиг.1

А 77

Фиг. 2

Ши991

if

-4

Z.80Z.99L

дЗ 80

Л,

во.

Фиг.5

fas. 8

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1991-07-30—Публикация

1988-12-13—Подача