Изобретение относится к измерительной технике и может быть использовано в радиоэлектронных системах регистрации и обработки сигналов быстропротекающих процессов.

Цель изобретения - повышение точности измерения путем многократного интегрирования измеряемого и опорного напряжения.

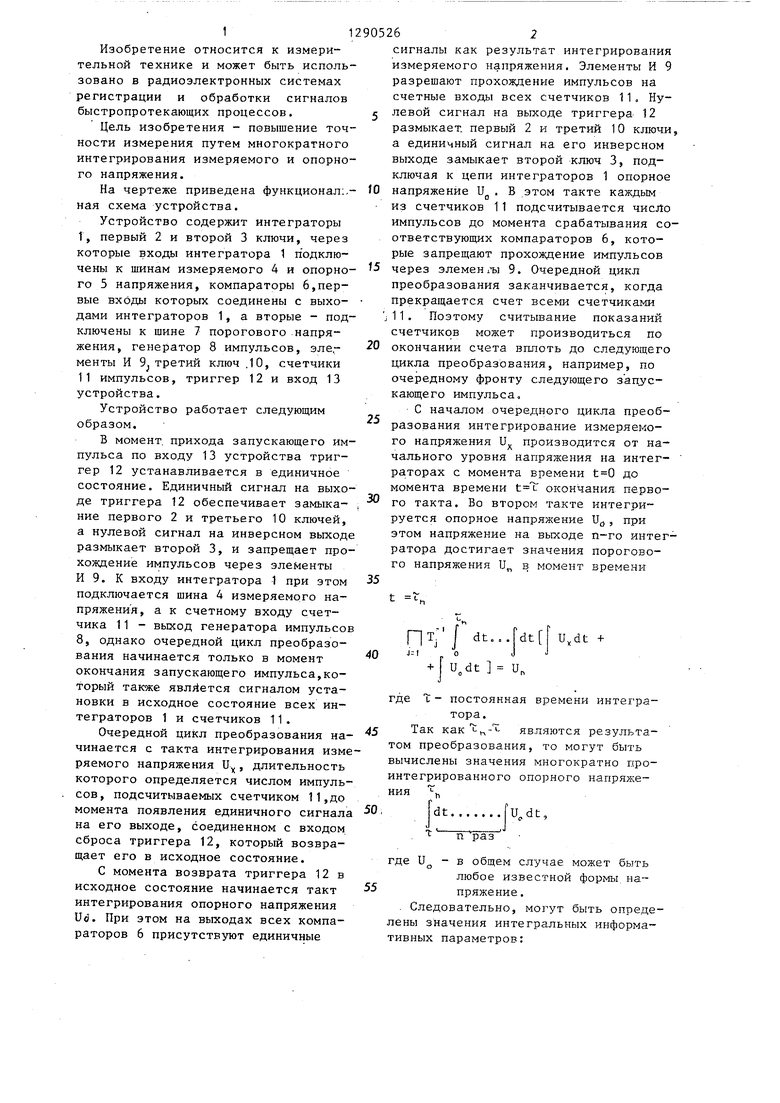

На чертеже приведена функциональная схема устройства.

Устройство содержит интеграторы 1, первый 2 и второй 3 ключи, через которые входы интегратора 1 подключены к шинам измеряемого 4 и опорного 5 напряжения, компараторы 6,первые входы которых соединены с выхо- дами интеграторов 1, а вторые - подключены к шине 7 порогового напряжения, генератор 8 импульсов, элементы И 9. третий ключ .10, счетчики 11 импульсов, триггер 12 и вход 13 устройства.

Устройство работает следующим образом,

В момент, прихода запускающего импульса по входу 13 устройства триггер 12 устанавливается в единичное состояние. Единичный сигнал на выходе триггера 12 обеспечивает замыка- кие первого 2 и третьего 10 ключей, а нулевой сигнал на инверсном выход размыкает второй 3, и запрещает прохождение импульсов через элементы И 9. К входу интегратора 1 при этом подключается шина 4 измеряемого напряжения, а к счетному входу счетчика 11 - выход генератора импульсо 8, однако очередной цикл преобразования начинается только в момент окончания запускающего импульса,который также является сигналом установки в исходное состояние всех интеграторов 1 и счетчиков 11.

Очередной цикл преобразования начинается с такта интегрирования измряемого напряжения U, длительность которого определяется числом импульсов, подсчитываемых счетчиком 11,до момента появления единичного сигнал на его выходе, соединенном с входом сброса триггера 12, который возвращает его в исходное состояние.

С момента возврата триггера 12 в исходное состояние начинается такт интегрирования опорного напряжения . При этом на выходах всех компараторов 6 присутствуют единичные

сигналы как результат интегрирования измеряемого напряжения. Элементы И 9 разрешают прохождение импульсов на счетные входы всех счетчиков 11. Нулевой сигнал на выходе триггера 12 размыкает, первый 2 и третий 10 ключи, а единичный сигнал на его инверсном выходе замыкает второй ключ 3, подключая к цепи интеграторов 1 опорное

напряжение U . Б .этом такте каждым из счетчиков 11 подсчитывается чисЛо импульсов до момента срабатывания соответствующих компараторов 6, которые запрещают прохождение импульсов

через элемен Ъ 9. Очередной цикл преобразования заканчивается, когда прекращается счет всеми счетчиками 11. Поэтому считывание показаний счетчиков может производиться по

окончании счета вплоть до следующего цикла преобразования, например, по очередному фронту следующего кающего импульса,

С началом очередного цикла преобразования интегрирование измеряемого напряжения U производится от начального уровня напряжения на раторах с момента времени до момента времени окончания первого такта. Во втором такте интегрируется опорное напряжение U, при этом напряжение на выходе п-го интегратора достигает значения порогового напряжения и„ в момент времени

t t.

Пт; / dt...dt u,dt 4Jrl оJ J

+ и dt и.

40

где t- постоянная времени интегратора.

Так как являются результатом преобразования, то могут быть вычислены значения многократно проинтегрированного опорного напряжения

fdt.fu.dt,

. t п paз

где и - в общем случае может быть любое известной формы,на- пряжение.

. Следовательно, могут быть определены значения интегральных информативных параметров:

dtJU,dt.

. n раз

Если пороговое напряжение выбирается соответствующим начальным уров ням напряжения на интеграторах , а опорное напряжение обратного знака ло отношению к измеряемому Sign U -Sign Ug, то при идеализации выполнения операций интегрирования и сравнения

dtIdttjU dt-lu dt О

° (п-1). раз

осуществляется компенсация аппаратурной составляющей погрешности от изменения постоянных времени интегрирования. -1

При аналитическом описании исследуемого сигнала системой приближаюп-1

5 которого соединены соответственно с выходами третьего ключа и элемента И, выходы счетчика импульсов яв- ляются первыми выходами устройства, выход интегратора соединен с первым

20 входом компаратора, второй вход ко- торого является шиной порогового напряжения, а выход соединен с третьим входом элемента И, о т л и ч а ющих функции f(t) 111 а. -т-г- весовые Щ и и с я тем, что, с целью повыше1 О

1

ния. точности измерения путем многократного интегрирования измеряемого и опорного напряжений, введены дополнительные интеграторы, компараторы, элементы И и счетчики импульсов, счетные входы которых соединены с выходами соответствующих дополнительных элементов И, выходы дополнительных счетчиков импульсов являются дополнительными выходами устройства, а

коэффициенты а/, определяются из системы уравнений:

и...,, -ffa, 0

о , 0 так как восстанавливается функция

реального времени, те измерение интервалов времени , C должно обеспечиваться с требуемой точностью в отличии от измерения постоянного напряжения. Если исследуемый сигнал по отношению к длительности интервала преобразования описывается монотонной непрерывной функцией, которая может быть представлена конечным рядом Тейлора, то может быть обеспечено его восстановление с нулевой методической погрешностью апрокси- мации.

Формула изобретения

45 нительного компаратора, вторые входы которых объединены и являются шиной порогового напряжения, выход каждого i-ro дополнительного компаратора соединен с первым вхоИнтегрирующий двухтактный аналого-цифровой преобразователь, содержащий интегратор, первый и второй вхо-50дом i-ro дополнительного элемен- ды которого соединены соответственно та И, вторые входы которых объеди- с выходами первого и второго ключей, нены и подключены к инверсному вы- входы которых являются соответствен- ходу триггера, а третьи входы объе- но шинами входного и опорного напря- динены и подключены к выходу гене- жений, управляющий вход первого клю-55 ратора импульсов.

ВНИИПИ Заказ 7916/57

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

905264

ча объединен с управляющим входом третьего ключа и соединен с прямым выходом триггера, инверсный выход которого соединен с управляющим входом

5 второго ключа и первым входом элемента И, информационный вход третьего ключа и второй вход элемента И объединены и соединены с выходом генератора импульсов, вход установки

to триггера объединен с входом установки счетчика импульсов и является шиной Пуск, а вход сброса триггера соединен с выходом переполнения счетчика .импульсов, счетные входы

5 которого соединены соответственно с выходами третьего ключа и элемента И, выходы счетчика импульсов яв- ляются первыми выходами устройства, выход интегратора соединен с первым

20 входом компаратора, второй вход ко- торого является шиной порогового напряжения, а выход соединен с третьим входом элемента И, о т л и ч а юЩ и и с я тем, что, с целью повыше

ния. точности измерения путем многократного интегрирования измеряемого и опорного напряжений, введены дополнительные интеграторы, компараторы, элементы И и счетчики импульсов, счетные входы которых соединены с выходами соответствующих дополнительных элементов И, выходы дополнительных счетчиков импульсов являются дополнительными выходами устройства, а

входы установки счетчика импульсов и дополнительных счетчиков импульсов объединены с входами установки интегратора и дополнительных интеграторов, выход интегратора соединен с входом первого дополнительного интегратора, выход i-ro дополнительного интегратора соединен с входом (i+1)-ro дополнительного интегратора и первым входом i-ro дополнительного компаратора, вторые входы которых объединены и являются шиной порогового напряжения, выход каждого i-ro дополнительного компаратора соединен с первым входом i-ro дополнительного элемен- та И, вторые входы которых объеди- нены и подключены к инверсному вы- ходу триггера, а третьи входы объе- динены и подключены к выходу гене- ратора импульсов.

Тираж ,92 2

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Измеритель среднеквадратического значения напряжения одиночного импульса случайной формы и длительности | 1987 |

|

SU1429054A1 |

| Устройство для измерения сопротивления | 1988 |

|

SU1649468A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1525915A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Аналого-цифровой интегрирующий преобразователь с автоматическим выбором диапазона преобразования | 1985 |

|

SU1251324A1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

Изобретение относится к измерительной технике и может быть и споль- зовано в радиоэлектронных системах регистрации и обработки сигналов бы- стропротекающих процессов. Изобретение позволяет повысить точность измерения. Это достигается путем многократного интегрирования измеряемого и опорного напряжений, которые через ключи 2,3 подключаются к интегратору 1, выход которого соединен с последовательно соединенными дополнительными интеграторами, выходы которых через компараторы 6, элементы И 9 Соединены со счетчиками 11. 1 ил. а % сл Ьэ со О сл tc Од i т IT

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| - М.: Энергия, 1975, с | |||

| Приспособление для подъема падающих гребней в машинах льнопрядильного, джутового и т.п. производств | 1913 |

|

SU396A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Шляндин В.М | |||

| Цифровые измерительные устройства | |||

| - М.: Высшая школа, 1981, с | |||

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| О rjo | |||

Авторы

Даты

1987-02-15—Публикация

1983-09-01—Подача