1

Изобретение относится к вычисли- тельной технике, а более точно к цифровым параллельным сдвигателям, используемым в процессорах малых, средних ЭВМ,.

Цель изобретения - сокращение аппаратурных затрат.

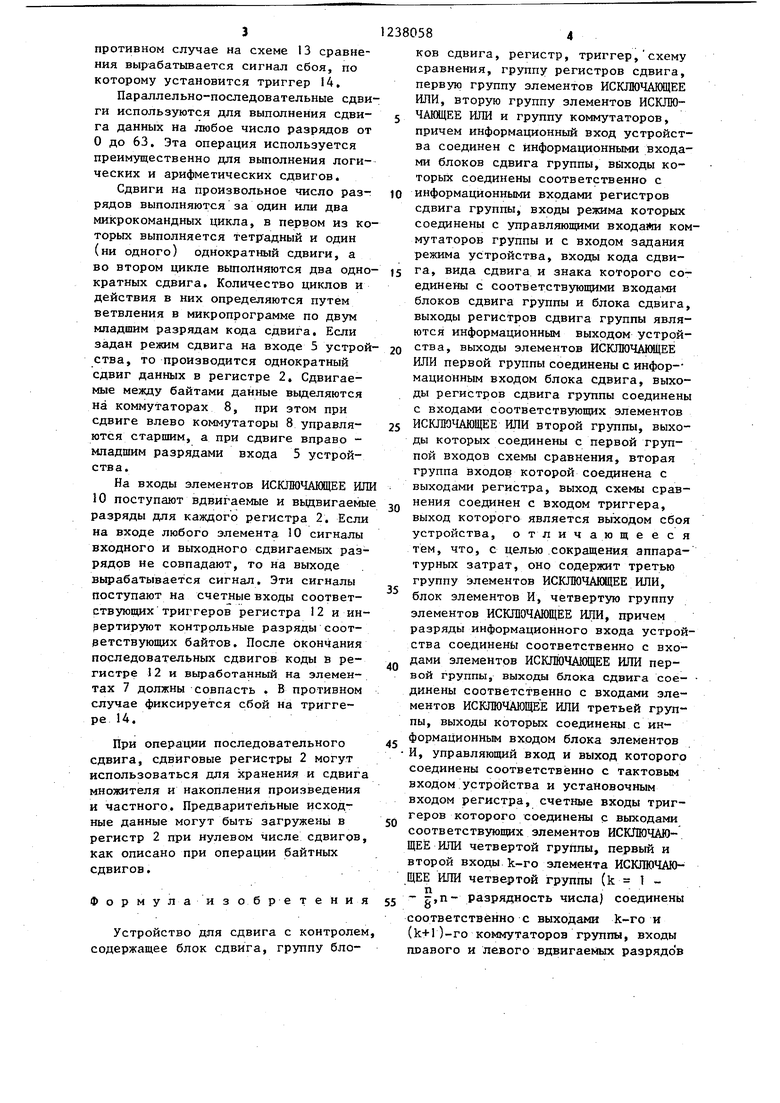

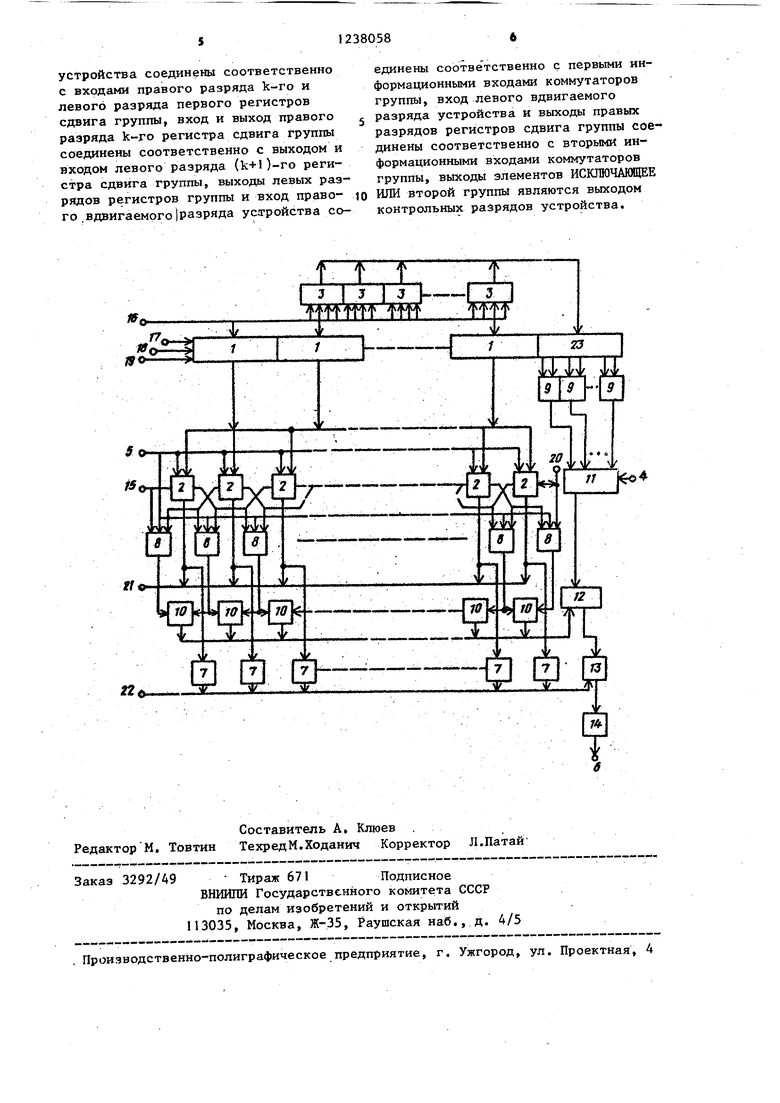

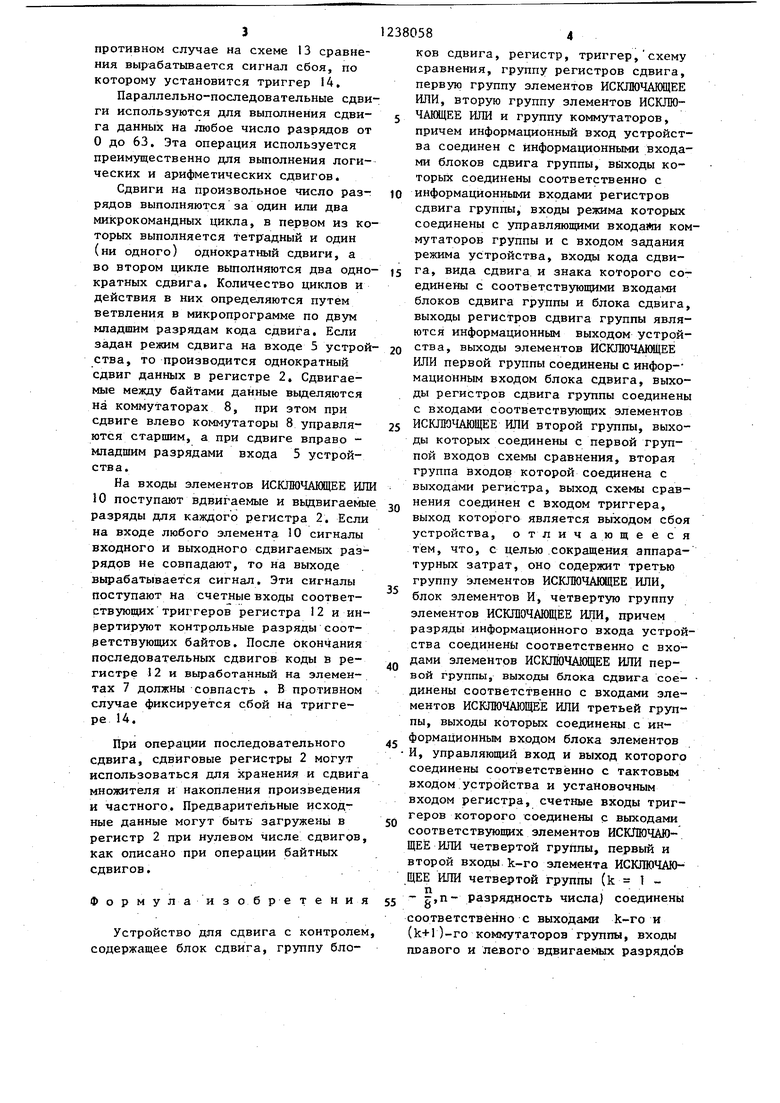

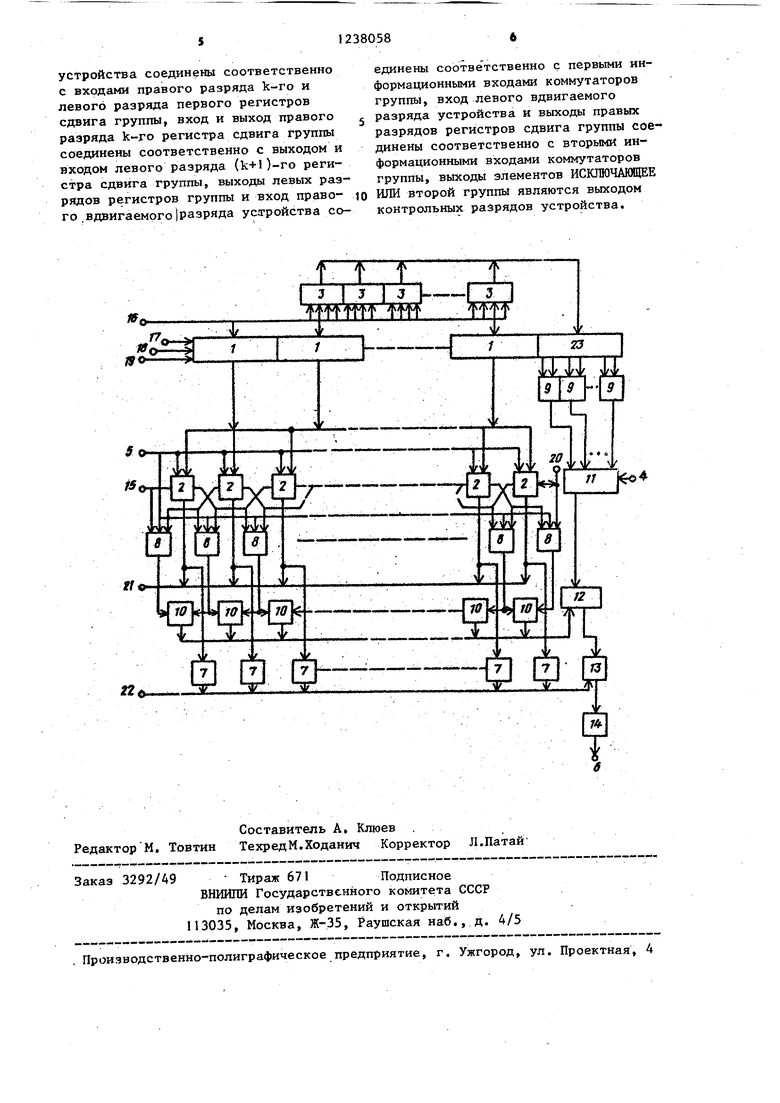

На ч ертеже представлена схема устройства для сдвига с контролем.

Устройство для сдвига с контролем содержит группу блоков 1 сдвига, группу регистров 2 сдвига, группу 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, тактовый вход 4 устройства, вход 5 задания режима устройства, выход 6 сбоя уст- ройства, группу 7 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу коммутаторов 8, группы 9, 10 элементов ИСКЛЮЧАЩЕЕ ИЛИ, блок 11 элементов И, регистр 12, схему 13 сравнения, триггер 14, вход 15 левого вдвигаемого разряда устройства, информационньй вход 16 устройства, вход J7 кода сдвига устройства, вход 18 вида сдвига устройства, вход 19 знака устройства, вход 20 правого вдвигаемого разряда устройства, информационный выход 21 устройства, выход-22 контрольных разрядов устройства, блок 23 сдвига.

Устройство для сдвига с контролем работает с широко распространенным 64-разрядным форматом данных, имеющи байтную структуру с одним контрольны разрядом на байт.

Блок 1 сдвига зьтолняет набор one раций согласно следующей таблице:

сдвига О

I

Вьтолняемая функция

Распространение всем выходам

знака по

О

о

о

о

I

Блокировка выходов (заполнение единицами) Сдвиг влево в дополнительном коде

Сдвиг вправо в дополнительном коде

Сдвиг циклический вправо Сдвиг циклический влево

Сдвиг арифметический вправо

Сдвиг арифметический влево

5

1238058J

Блок 1 сдвига вьшолняет сдвиги на количество разрядов кратное четырем и реализован аналогично прототипу.

Регистр 2 сдвига выполняет сдвиги 5 на один разряд за такт следующим образом:

Код управления Режим

Хранение Сдвиг вправо Сдвиг влево Прием данньпс

Устройство для сдвига с контролем может выполнять следующие операции: тетрадный или байтный сдвиг; параллельно-последовательный сдвиг; последовательный сдвиг.

В начале временного цикла работы на входе 18 устанавливается код требуемой операи 1И, на входе 17 - код числа сдвигов, на входе 19 - знак числа. На входе 5 устанавливается режим приема. На входе 16 устанавливаются входные данные, которые поступают на входы блоков 1 сдвига группы, где сдвигаются на заданное количество разрядов в соответствии со знаком и видом сдвига. Входные данные с входа 16 устройства поступают также на группу 3 элементов ИСКЛЮЧАЩЕЕ ИЛИ, где сворачиваются потетрадно и поступают на вход блока 23 сдвига, где сдвигаются на то же число разрядов, что и входные данные. Сдвинутые входные данные в соответствии со значением входа 5 устройства принимаются в регистры 2 сдвига. С выхода блока 23 сдвига значения поступают на группу 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, где формируются значения контрольных разрядов байтов, которые по импульсу с входа 4 устройства проходят через блок II элементов И и заносятся через установочные входы в триггеры регистра 12.

Сдвинутые данные поступают на выход 21. данных, а контрольные разряды для них, вырабатываемые на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 7, поступают на выход 22.

При правильной работе устройства сформированньй код на элементах 7 и код, полученный в результате сдвига в регистре 12, должны совпадать. В

противном случае на схеме 13 сравнения вырабатьтается сигнал сбоя, по которому установится триггер 14.

Параллельно-последовательные сдвиги используются для выполнения сдви- га данных на любое число разрядов от О до 63. Эта операция используется преимущественно для вьтолнения логических и арифметических сдвигов.

Сдвиги на произвольное число раз- рядов выполняются за один или два микрокомандных цикла, в первом из которых выполняется тетр адный и один (ни одного) однократный сдвиги, а во втором цикле выполняются два одно- кратных сдвига. Количество циклов и действия в них определяются путем ветвления в микропрограмме по двум младшим разрядам кода сдвига. Если задан режим сдвига на входе 5 устрой- ства, то производится однократный сдвиг данных в регистре 2. Сдвигаемые между байтами данные выделяются на коммутаторах 8, при этом при сдвиге влево коммутаторы 8 управля- ются старшим, а при сдвиге вправо - младшим разрядами входа 5 устройства.

На входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 поступают вдвигаемые и вьщвигаемые разряды для каждого регистра 2. Если на входе любого элемента 10 сигналы входного и выходного сдвигаемых разрядов не совпадают, то на выходе вьфабатывается сигнал. Эти сигналы поступают на счетные входы соответствующих триггеров регистра 12 и ин- рертируют контрольные разряды соответствующих байтов. После окончания последовательных сдвигов коды в регистре 12 и выработанный на элементах 7 должны совпасть . В противном случае фиксируется сбой на триггере 14.

При операции последовательного сдвига, сдвиговые регистры 2 могут использоваться для хранения и сдвига множителя и накопления произведения и частного. Предварительные исходные данные могут быть загружены в регистр 2 при нулевом числе сдвигов, как описано при операции байтных сдвигов.

Формулаизобретения

Устройство для сдвига с контролем содержащее блок сдвига, группу бло

5 0 5

5 0

5

0

5

0

ков сдвига, регистр, триггер, схему сравнения, группу регистров сдвига, первую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и группу коммутаторов, причем информационный вход устройства соединен с Информационными входами блоков сдвига группы, выходы которых соединены соответственно с информационными входами регистров сдвига группы, входы режима которых соединены с управляющими входали коммутаторов группы и с входом задания режима устройства, входы кода сдвига, вида сдвига и знака которого соединены с соответствующими входами блоков сдвига группы и блока сдвига, выходы регистров сдвига группы являются информационным выходом устройства, выходы элементов ИСКЛЮЧАКНЦЕЕ ИЛИ первой группы соединены с инфор- мационным входом блока сдвига, выходы регистров сдвига группы соединены с входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы которых соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами регистра, выход схемы сравнения соединен с входом триггера, выход которого является выходом сбоя устройства, отличающееся тем, что, с целью .сокращения аппаратурных затрат, оно содержит третью группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок элементов И, четвертую группу элементов ИСКЛЮЧАЩЕЕ ИЛИ, причем разряды информационного входа устройства соединены соответственно с входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выходы блока сдвига сое- динены соответственно с входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы, выходы которых соединены с информационным входом блока элементов И, управляющий вход и выход которого соединены соответственно с тактовым входом устройства и установочным входом регистра, счетные входы триггеров которого соединеш 1 с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ четвертой группы, первый и второй входы k-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ четвертой группы (k 1 г,п- разрядность числа) соединены о

соответственно С выходами k-ro и (k+l)-ro коммутаторов группы, входы шэавого и левого вдвигаемых разрядо в

устройства соединены соответственно с входами правого разряда k-ro и левого разряда первого регистров сдвига группы, вход и выход правого разряда k-ro регистра сдвига группы соединены соответственно с выходом и входом левого разряда (k+1)-го регистра сдвига группы, выходы левых разрядов регистров группы и вход право- го.вдвигаемого|разряда устройства соединены соответственно с первыми информационными входами коммутаторов группы, вход левого вдвигаемого разряда устройства и выходы правых разрядов регистров сдвига группы соединены соответственно с вторыми информационными входами коммутаторов группы, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы являются выходом контрольных разрядов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Генератор случайных чисел | 1984 |

|

SU1310813A1 |

Изобретение относится к области вычислительной техники, в частности к цифровым параллельным сдвигателям, используемым в процессорах малых и средних ЭВМ. Целью изобретения является сокращение аппаратурных затрат. Для достижения зтоЙ цели устройство, содержащее блок сдвига, группу блоков, сдвига, регистр, триггер, схему сравнения, группу регистров сдвига, первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и группу коммутаторов, содержит третью и четвертую группы элементов ИСКЛЮЧАЩЕЕ ИЛИ и блок элементов И. 1 ил. с S ьр ОО оо сд 00

ff

23

Л

п k«

Составитель А, Клюев , Редактор М. Товтин ТехредМ.Ходанич Корректор Л.Патай

Заказ 3292/49 Тираж 671 Подписное

ВНИИПИ Государственного комите:та СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения мыла | 1920 |

|

SU364A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-01-09—Подача