10

f5

Изобретение относится к вычислительной технике и может быть использовано для тестового контроля БИС памяти и оперативных запоминающих устройств (ОЗУ).

Целью изобретения является повышение быстродействия устройства.

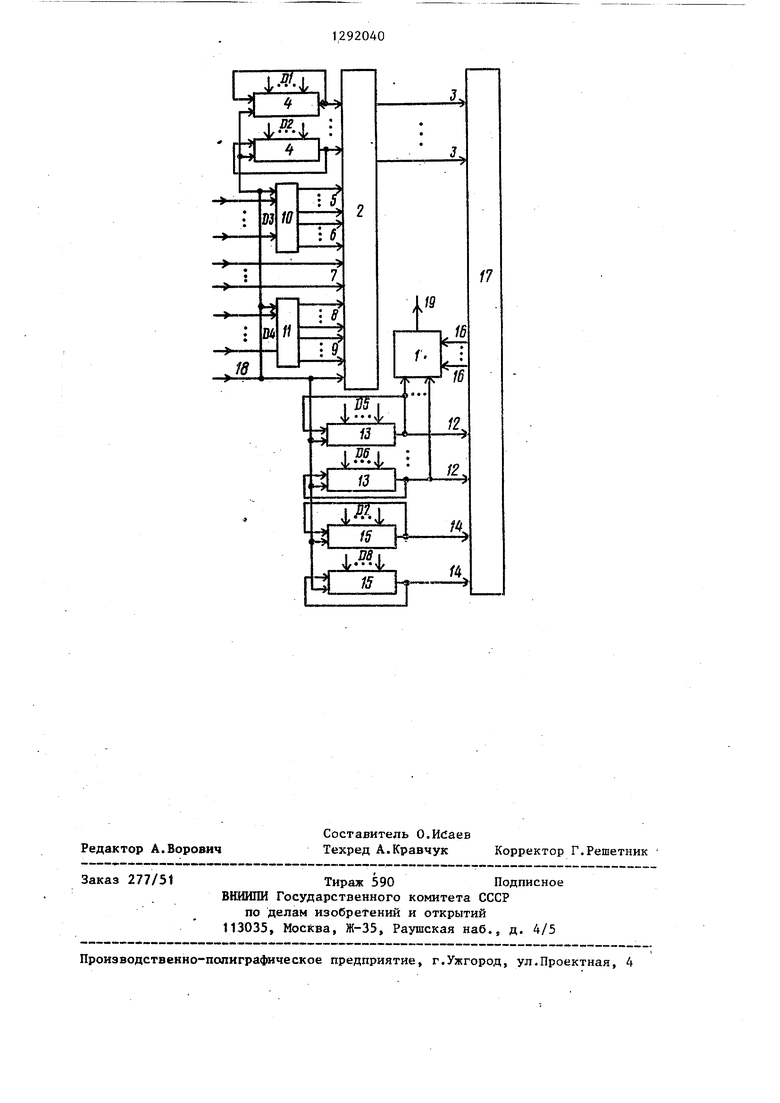

На чертеже представлена схема устройства для контроля блоков оперативной памяти.

Устройство содержит блок 1 срав- нения, третий счетчик 2, выходы 3 которого являются адресными выходами устройства, одни входы соединены с выходами кольцевых регистров 4 сдвига первой группы, входы 5, 6, 8 и 9 подключены к выходам первого и второго счетчиков 10 и 11, а другие входы 7 являются входами устройства, выходы 12 кольцевых регистров 13 сдвига второй группы и выходы 14 кольцевых регистров 15 сдвига третьей группы. На чертеже также показаны информационные входы 16 устройства, контролируемое ОЗУ 17, вход 18 синхронизации и выход 19 ошибки.

Осуществляют контроль ОЗУ согласно тестам, в которых повторяются несколько раз определенные последовательности (циклы) обращений к ОЗУ. Например, при шахматном тесте повторяются последовательности записи О и 1, а затем их считывания. При других тестах возможны и более сложные циклы.

Записывают информацию о первом цикле обращений к ОЗУ 17 в регистры 4, 13, 15, а начальньй адрес контроля - в счетчик 2. Эта информация 0 представляет собой цоследовательнос- ти логических состояний, которые необходимо устанавливать на соответствующих входах ОЗУ 17 и счетчика 2, чтобы произошла предусмотренная 5 тестом последовательность обращений к ОЗУ 17 в пределах цикла. Какие логические состояния необходимо установить на входах ОЗУ 17, чтобы

35

20

25

30

произощло обращение к нему, предусмот- 0 команды счет вперед, счет назад, заренное тестом, известны из описания принципа работы конкретного контролируемого ОЗУ 17, а логические состояния, которые необходимо установить на входах счетчика 2, чтобы произошло установленное тестом изменение адреса, известны из описания принципа работы используемого конк- .ретного счетчика 2.

5

0 5

Таким образом, информация, необходимая для записи в элементы 2, 4, 13, 15, известна из описания принципа работы конкретных ОЗУ и счетчика 2 и описания (алгоритма) выбранного теста контроля.

Регистры 4, управляющие работой счетчика 2, нужны лишь в том случае, если цикл обращений к ОЗУ 17 предусматривает не только счет счетчика 2 вперед, но и его другие операции, например счет назад или запись информации с параллельных входов 5, или 6, или 8, или 9. Сигналы с этих регистров,и осуществляют соответствующие управления счетчиком 2.

Если указанный цикл обращений к ОЗУ. включает резкие переходы адресов, например возвращения адреса на несколько ячеек памяти назад или вперед (например, тест Дополнительная адресация), можно использовать счетчики типа 10 и 11, подключенные к параллельньм входам счетчика 2, в которые предварительно также записывают информацию. В процессе работы устройства происходит счет в этих счетчиках и перепись информации с их выходов в счетчик 2, управляемая . сигналами с регистров 4.

Информацию в элементы 2, 4, 10, 11,-13, 15 записывают параллельно (т.е. практически одновременно) через их входы Д 7 с параллельных ре- 5 гистров, в частности выходных портов управляющей ЭВМ, например, Электра- , ника К1-20. Осуществляют это любыми известны ш путями.

После записи информации в элементы 2, 4, 10, 11, 13, 15 подают тактовые импульсы на шину 18.По переднему фронту тактового импульса происходит сдвиг информации в .регистрах 4 и счет в счетчиках 10 и 11, По его заднему фронту происходит исполнение счетчиком 2 команды, код которой установлен на его управляющих входах, т.е. на выходах регистров 4, например.

0

5

0

пись с параллельных входов 5, или 6, или 8, или 9. По заднему фронту тактового импульса происходит сдвиг информации в регистрах 13 и 15. На вхо- 55 дах 12 ОЗУ 17 устанавливается информация, подлежащая записи в ОЗУ 17 или ожидаемая при считывании с ОЗУ 17. На управляющих входах 14 ОЗУ 17 устанавливается код команды записи в ОЗУ

17 или считывании с ОЗУ 17 или регенерации и т.п. в зависимости от содержания цикла. Если есть необходимость в стробирующем сигнале в ОЗУ 17 (сигнале, по которому ОЗУ 17 выполняет 5 команды, на схеме шина этого сигнала условно не показана), его можно подавать в ОЗУ 17 после сдвига информации в регистрах 15. Если на входах 14 усФормула изобретения

f5

до очередной записи информации в указанные элементы. При длительных интервалах времени между двумя запися- .ми информации в указанные элементы можно успеть подготовить информацию , для нескольких последующих записей,- . чтобы потом, при коротких интервалах времени между двумя записями информации в указанные элементы, свести до

танавливается код команды считывания, fO минимума задержку устройства контна выходах 16 появляется считанная роля подготовкой информации.

с ОЗУ 17 информация, которая блоком 1

сравнивается с ожидаемой информацией,

установленной в это время на выходах

регистров 13. При неисправности ОЗУ

17 появляется сигнал несравнения на

выходе 19 блока 1. В это время на

входах 3 ОЗУ 17 присутствует адрес

ячейки памяти, с которой произошло

считывание неправильной информации.

Подачу тактовых импульсов на шину 18

осуществляют до тех пор, пока соглас-

но тесту осуществляют одинаковые циклы обращений к ОЗУ 17. В течение всего этого времени в регистрах 4, 13,

15 инфо{ мация циркулирует по кольцу

(т.е. с последовательного выхода на

последовательный вход). Как только

на входах 3 ОЗУ 17 устанавливается

адрес, после которого согласно тесту

необходимо осуществлять другие циклы

обращений к ОЗУ 17 (например, в простейшем случае, после циклов записей

20

30

Устройство для контроля оперативной памяти, содержащее блок сравнения, входы первой группы которого являются информационными входами устройства, первый и второй счетчики, отличающееся тем, что, с целью повьппения быстродействия, в него введены третий счетчик и кольцевые регистры сдвига, причем установочные входы кольцевых регистров сдвига, первого и второго счетчиков и установочные входы первой группы третьего счетчика являются установочными входами устройства, управляющие входы третьего счетчика соединены с выходами кольцевых регистров сдвига первой группы, .установочные входы второй и TpeTbeii групп третьего счетчика подключены соответственно к выходам первого и

О необходимо записать 1 или осуществить считывание), осуществляют запись в элементы 4,10, 11, 13, 15 другой информации - о новых циклах обращений к ОЗУ 17. Затем вновь подают тактовые импульсы на шину 18, осуществляющие обращения к ОЗУ 17. И так далее пока не будет закончен тест контроля ОЗУ.

Для экономии времени есть возможность сразу после записи информации в элементы 4, 10, 11, 13, 15 приступить к подготовке в портах ЭВМ информации об очередных циклах обращений к ОЗУ 17 и успеть ее подготовить

Формула изобретения

Устройство для контроля оперативной памяти, содержащее блок сравнения, входы первой группы которого являются информационными входами устройства, первый и второй счетчики, отличающееся тем, что, с целью повьппения быстродействия, в него введены третий счетчик и кольцевые регистры сдвига, причем установочные входы кольцевых регистров сдвига, первого и второго счетчиков и установочные входы первой группы третьего счетчика являются установочными входами устройства, управляющие входы третьего счетчика соединены с выходами кольцевых регистров сдвига первой группы, .установочные входы второй и TpeTbeii групп третьего счетчика подключены соответственно к выходам первого и

второго счетчиков, а выходы являются адрес11ьп ш выходами устройства, входы второй группы блока сравнения соединены с выходами кольцевых регистров сдвига второй группы и являются информационными выходами устройства, выход блока сравнения и выходы кольцевых регистров сдвига третьей группы являются соответственно выходом ошибки и управляющими выходами устройства, сиихровходы первого, второго, третьего счетчиков и кольцевых регистров сдвига объединены и являются входом синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1985 |

|

SU1302325A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

Изобретение относится к вычислительной технике и может быть использовано для тестового контроля БИС памяти и оперативных запоминающих устройств (ОЗУ). Целью изобретения является повьшение быстродействия устройства. Устройство содержит пер- вьй, второй и третий счетчики адреса, кольцевые регистры сдвига и блок сравнения. Повьпцение быстродействия устройства достигается за счет формирования тестовых воздействий кольцевьп ш peгиcтpa п с:дпига в каждом такте синхронизации устройства. 1 ил. ISD р N3

Редактор А.Ворович

Составитель О.Исаев Техред А.Кравчук

Заказ 277/5t

Тираж 590Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор Г.Решетник

| Основы эксплуатащга ЭВМ./Под ред | |||

| Б.П.Кагана | |||

| М.: Энергоатоьшздат, 1983,- с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-02-23—Публикация

1985-06-21—Подача