(5) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ПОЛУПРОВОДНИКОВОЙ ОПЕРАТИВНОЙ

1

Изобретение относится к запоми нающим устройствам.

Известны устройства для контроля полупроводниковой оперативной памяти, одно из которых содержит счетчик адреса, схемы сравнения и счетный триггер, а второе - счетчик адреса, счетчик циклов, элементы импликации и элемент И Cl ...

Недостатками этих устройств являются низкие надежность и быстродействие.

Наиболее близким к изобретению является устройство для контроля полупроводниковой оперативной памяти, содержащее внутренний и внешний счетчики адреса, триггеры X, У и О, два блока вентилей, блок управления, компаратор ошибок, компаратор адресов, триггер ошибки, два буфера и интерфейс проверяемого оперативного запоминающего устройства (ОЗУ) 23..

Недостатками известного устройства являются низкое быстродействие. ПАМЯТИ

так как в нем используются тесты, имекхцие продолжительность выполнения (Вы +2N) обращений (где N - число ячеек памяти проверяемого ОЗУ), и низкая надежность, так как оно не обеспечивает проверку таких неисправностей БНС ОЗУ, как чувствительность ячеек памяти к многократной записи информации в соседние ячейки, потеря чувствительности усилителя считывания

to и проверку времени хранения информа.ции в ячейках БИС ОЗУ динамического , типа.

Целью изобретения является повышение бь1стро деист ВИЯ и надежности

5 устройства.

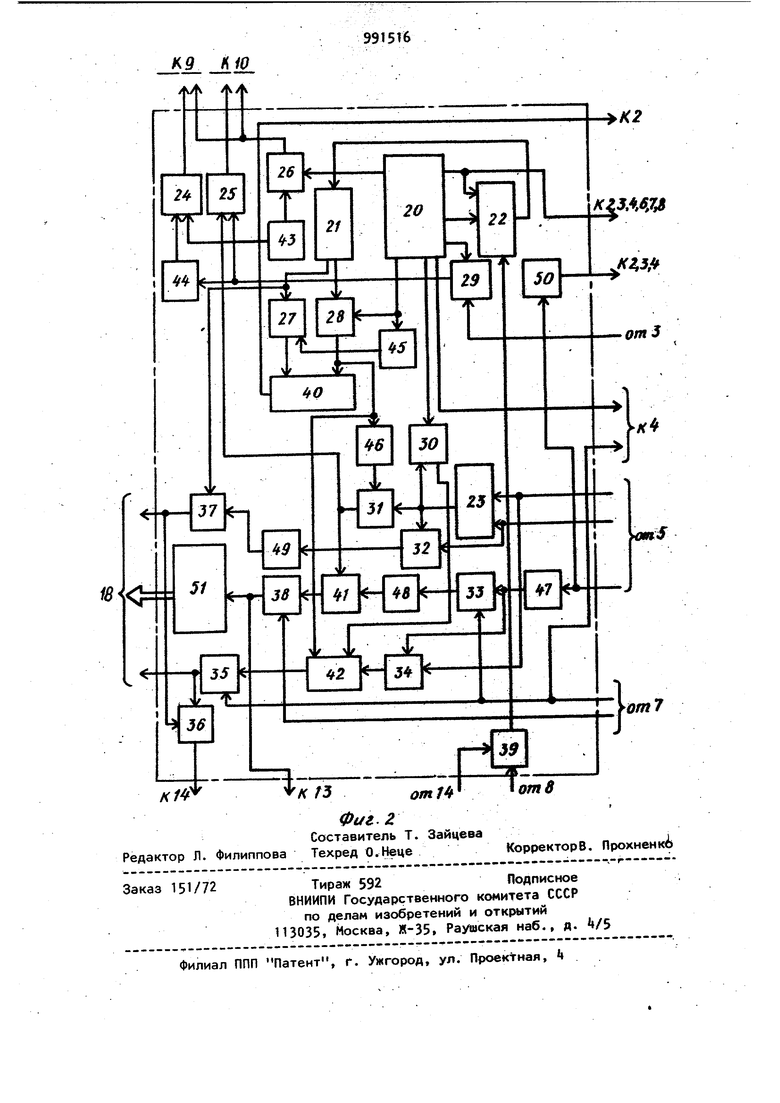

Поставленная цель достигается тем, что в устройство для контроля полупроводниковой оперативной памяти, содержащее блок управления, счетчики,

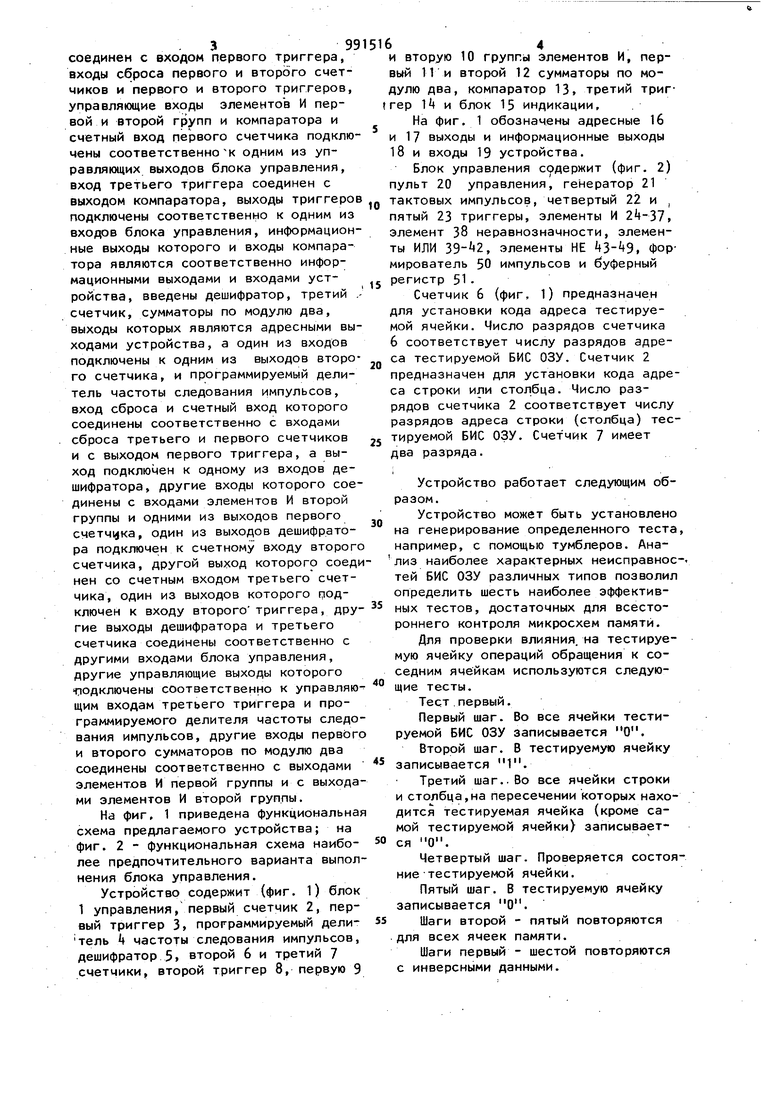

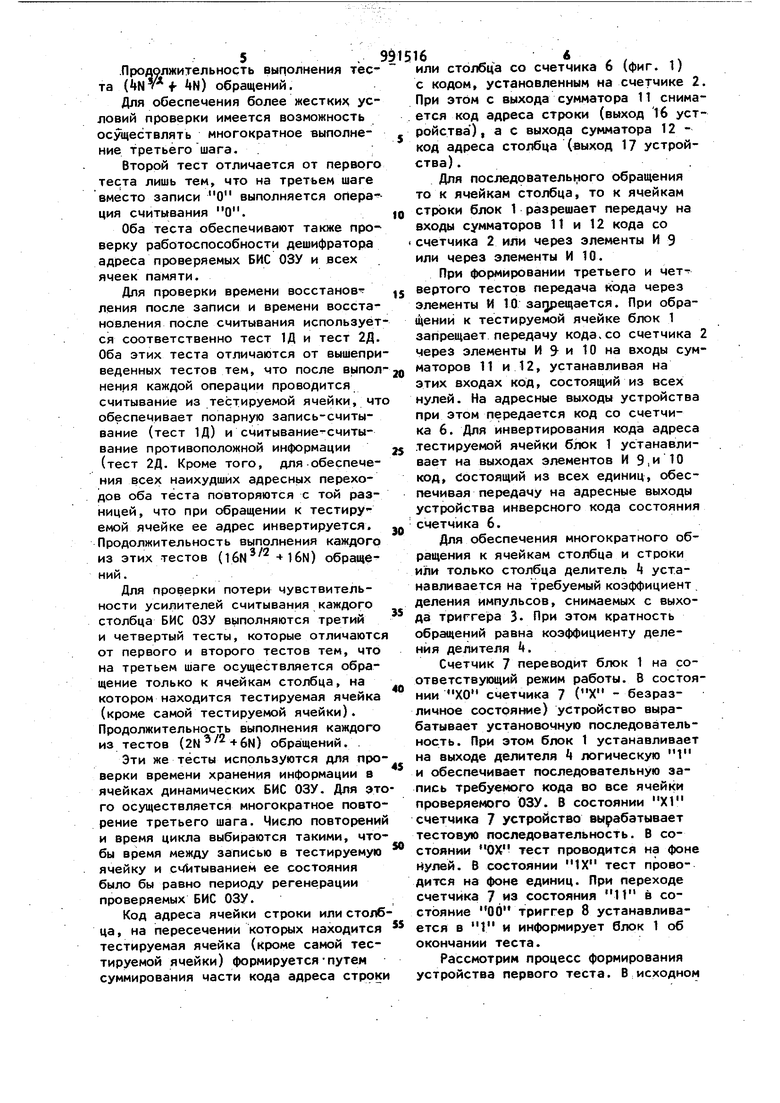

)триггеры, группы элементов И и компаратор, причем одни из выходов первого счетчика подключены к входам элементов И первой группы, а другой выход соединен с входом первого триггера, входы сброса первого и второго счетчиков и первого и второго триггеров, управляющие входы элементов И первой и второй групп и компаратора и счетный вход первого сметчика подклю чены соответственно К одним из управляющих выходов блока управления, вход третьего триггера соединен с выходом компаратора, выходы триггеро подключены соответственно к одним из входов блока управления, информацион ные выходы которого и входы компаратора являются соответственно информационными выходами и входами устройства, введены дешифратор, третий счетчик, сумматоры по модулю два, выходы которых являются адресными вы ходами устройства, а один из входов подключены к одним из выходов второ го счетчика, и программируемый делитель частоты следования импульсов, вход сброса и счетный вход которого соединены соответственно с входами сброса третьего и первого счетчиков и с выходом первого триггера, а выход подключен к одному из входов дешифратора, другие входы которого сое динены с входами элементов И второй группы и одними из выходов первого счетчука, один из выходов дешифратора подключен к счетному входу второг счетчика, другой выход которого соед нен со счетным входом третьего счетчика, один из выходов которого П1ОДклгочен к входу второго триггера, дру гие выходы дешифратора и третьего счетчика соединены соответственно с другими входами блока управления, другие управляющие выходы которого подключены соответственно к управляю щим входам третьего триггера и программируемого делителя частоты следо вания импульсов, другие входы первог и второго сумматоров по модулю два соединены соответственно с выходами элементов И первой группы и с выхода ми элементов И второй группы. На фиг, 1 приведена функциональна схема предлагаемого устройства; на фиг. 2 - функциональная схема наиболее предпочтительного варианта выпол нения блока управления. Устройство содержит (фиг. 1) блок 1 управления, первый счетчик 2, первый триггер 3 программируемый делитель k частоты следования импульсов, дешифратор 5 второй 6 и третий 7 счетчики, второй триггер 8, первую 9 9 и вторую 10 группы элементов И, первый 11 и второй 12 сумматоры по модулю два, компаратор 13, третий тригrep Ik и блок 15 индикации. На фиг. 1 обозначены адресные 16 и 17 выходы и информационные выходы 18 и входы 19 устройства. Блок управления содержит (фиг. 2) пульт 20 управления, генератор 21 тактовых импульсов, четвертый 22 и пятый 23 триггеры, элементы И 24-37, элемент 38 неравнозначности, элементы ИЛИ , элементы НЕ , формирователь 50 импульсов и буферный регистр 51. Счетчик 6 (фиг, 1) предназначен для установки кода адреса тестируемой ячейки. Число разрядов счетчика 6 соответствует числу разрядов адреса тестируемой БИС ОЗУ. Счетчик 2 предназначен для установки кода адреса строки или столбца. Число разрядов счетчика 2 соответствует числу разрядов адреса строки (столбца) тестируемой БИС ОЗУ. Счетчик 7 имеет два разряда. Устройство работает следующим образом. Устройство может быть установлено на генерирование определенного теста, например, с помощью тумблеров. АнаЛИЗ наиболее характерных неисправноетей БИС ОЗУ различных типов позволил определить шесть наиболее эффективных тестов, достаточных для всестороннего контроля микрюсхем памяти. Для проверки влияния, на тестируемую ячейку операций обращения к соседним ячейкам используются следующие тесты. Тест первый. Первый шаг. Во все ячейки тестируемой БИС ОЗУ записывается О. Второй шаг. В тестируемую ячейку записывается 1. Третий шаг.. Во все ячейки строки и столбца,на пересечении которых находится тестируемая ячейка (кроме самой тестируемой ячейки) записывается О. Четвертый шаг. Проверяется состояние тестируемой ячейки. Пятый шаг. В тестируемую ячейку записывается О. Шаги второй - пятый повторяются для всех ячеек памяти. Шаги первый - шестой повторяются с инверсными данными. .Продолжительность выполнения тес та 4N) обращений. Для обеспечения более жестки условий проверки имеется возможность осуществлять многократное выполнение третьего шага. . Второй тест отличается от первого теста лишь тем, что на третьем шаге вместо записи О выполняется оПерация считывания О. Оба теста обеспечивают также проверку работоспособности дешифратора адреса проверяемых БИС ОЗУ и всех ячеек памяти. Для проверки времени восстановит ления после записи и времени восстановления после считывания использует ся соответственно тест 1Д и тест 2Д. Оба этих теста отличаются от вышепри веденных тестов тем, что после выпол нения каждой операции проводится считывание из тестируемой ячейки, чт обеспечивает попарную запись-считывание (тест 1Д) и считывание-считывание противоположной информации (тест 2Д. Кроме того, для обеспечения всех наихудших адресных переходов оба теста повторяются с той разницей, что при обращении к тестируемой ячейке ее адрес инвертируется. Продолжительность выполнения каждого из этих тестов ( ) обращений. Для проверки потери чувствительности усилителей считывания каждого столбца БИС ОЗУ выполняются третий и четвертый тесты, которые отличаются от первого и второго тестов тем, что на третьем шаге осуществляется обращение только к ячейкам столбца, на котором находится тестируемая ячейка (кроме самой тестируемой ячейки). Продолжительность выполнения каждого из тестов (2ы -«-6М) обращений. . Эти же тесты используются для проверки времени хранения информации в ячейках динамических БИС ОЗУ. Для это го осуществляется многократное повторение третьего шага. Число повтор ений и время цикла выбираются такими, чтобы время между записью в тестируемую ячейку и с41тыванием ее состояния было бы равно периоду регенерации проверяемых БИС ОЗУ. Код адреса ячейки строки или столб ца , на пересечении которых находится тестируемая ячейка (кроме самой тестируемой ячейки) формируется-путем суммирования части кода адреса стррки 164 . или столбца со счетчика 6 (фиг. 1) с кодом, установленным на счетчике 2. При этом с выхода сумматора 11 снима. ется код адреса строки (выход 16 устройства) , а с выхода cyhwiaTopa 12 код адреса столбца (выход 17 устройства) .. Для последовательного обращения то к ячейкам столбца, то к ячейкам строки блок 1 разрешает передачу на входы сумматоров 11 и 12 кода со счетчика 2 или через элементы И 9 или через элементы И 10. При формировании третьего и четвертого тестов передача кода через элементы И 10 заф ещается. При обращений к тестируемой ячейке блок 1 запрещает передачу кода,со счетчика 2 через элементы И 9- и 10 на входы сумматоров 11 и 12, устанавливая на этих входах код, состоящий из всех нулей. На адресные выходы устройства при этом передается код со счетчика 6. Для инвертирования кода адреса тестируемой ячейки блок 1 устанавливает на выходах элементов И 9,и 10 код, Состоящий из всех единиц, обеспечивая передачу на адресные выходы устройства инверсного кода состояния счетчика 6. Для обеспечения многократного обращения к ячейкам столбца и строки или только столбца делитель k устанавливается на требуемый коэффициент деления импульсов, снимаемых с выхода тригге ра 3- При этом кратность обращений равна коэффициенту деления делителя k. Счетчик 7 переводит блок 1 на соответствующий режим работы. В состояНИИ ХО счетчика 7 (X - безразличное состояние) устройство вырабатывает установочную последовательность. При этом блок 1 устанавливает на выходе делителя логическую 1 и обеспечивает последовательную запись требуемого кода во все ячейки проверяемого ОЗУ. В состоянии XI счетчика 7 устройство вырабатывает тестовую последовательность. В состоян и ОХ тест проводится на фоне нулей. В состоянии IX тест проводится на фоне единиц. При переходе счетчика 7 из состояния 11 в состояние 00 триггер 8 устанавливается в 1 и информирует блок 1 об окончании теста. Рассмотрим процесс формирования устройства первого теста. В исходном состоянии счетчики 2, 6 и 7, триггеры 3 и 8 и делитель сброшены. Счет чик 7 находится в состоянии 00, из чего следует, что устройство вырабатывает установочную последовательность - запись О во все ячейки про веряемого ОЗУ (первый шаг теста). При этом блок 1 запрещает передачу кода со счетчика 2 через элементы И 9 и 10 и поддерживает выход делителя k в состоянии 1, благодаря чему дешифратор 5 дешифрует состояни первых двух разрядов счетчика 2. При запуске устройства блок 1 формирует тактовые импульсы, поступакицие на вход счетчика 2 и изменяющие его состояние. В состояниях 00 и 01 счетчика 2 блок 1 вырабатывает код записи О, снимаемого с выхода 18 устройства. На выходах 16 и 18 устройства в течение всего первого шага теста установлен код, поступающий со счетчика 6. При переходе счетчика 2 в следующее состояние блок 1 сбрасывает счетчик 2, триггер 3 и де литель k и состояние счетчика 6 измен ется. Процесс повторяется для всех состояний счетчика 6. При переходе счетчика 6 в нулевое состояние счетчик 7 переключается в состояние 01 и устройство переходи на режим генерирования непосредствен но заданной тестовой последовательт ности. При этом блок 1 разрешает работу делителя 4. При нулевом состоянии счетчика 2 блок 1 выдает на выход 18 код записи 1 (второй шаг теста), а на выходах 16 и 18 устанавливается код адреса тестируемой ячейки, зафиксированный счетчиком 6. Затем счетчик 2 под действием тактовых импульсов с блока 1 последовательно изменяет свое состояние. При этом (при отсутствии нулевого состоя ния счетчика 2) блок 1 выдает на выход 18 код записи О в ячейки, расположенные на том же столбце, что и тестируемая ячейка. Адрес этих яче ек формируется путем суммирования по модулю два части кода адреса тестируемой ячейки, зафиксированного счет чиком 6, с состоянием счетчика 2, по ступающего на сумматор 11 через элементы И Э. При переходе счетчика 2 в нулевое состояние триггер 3 устанавливается в 1 и процесс повторяется. При этом обеспечивается последовательное обращение к ячейкам строки (третий шаг теста). Адрес эти 9 6 ячеек формируется на выходах сумматоров 11 и 12, причем при нахождении триггера 3 в состоянии 1 блок 1 разрешает передачу кода со счетчика 2 на входы сумматора 12, запрещая передачу кода через элементы И 9. Сум матор 11 передает при этом часть кода адреса со счетчика 6 без изменения. При переходе счетчика 2 в нулевое состояние триггер 3 переключается в состояние О и на выходе,делителя k появляется логическая 1, которая разрешает дешифрование дешифратором 5 первых двух разрядов счетчика 2. В состоянии 00 счетчика 2 блок 1 формирует на выходе 18 код считывания (четвертый шаг теста) , а в состоянии 01 - код записи О (пятый шаг теста). При этом блок 1 запрещает передачу кода через элементы И 9 и 10, вызывая передачу на выходы 16 и 17 кода со счетчика 6. При переходе счетчика 2 в следующее состояние блок 1 сбрасывает счетчик 2, три|- гер 3, делитель k и счетчик 6 переходит в следующее состояние. Процесс повторяется для всех состояний счетчика 6. При формировании нд выходе 18 блоком 1 кода считывания, он формирует также код требуемой реакции, поступающий на вход компаратора 13, который сравнивает требуемую реакцию с реакцией проверяемого ОЗУ. Блок 1 стробирует запись результата сравнения в тиггер 1. При обнаружении ошибки устройство прекращает генерирование теста и блок 15 индуцирует результат контроля. При переходе счетчика 6 в нулевое состояние изменяется состояние счетчика 7 режимов. При этом старший разряд счетчика 7 переходит в состояние 1 и весь процесс повторяется с инвертированием кода данных. Работа устройства при генерировании остальных тестов отличается очень незначительно. Отличие для тестов 1Д и 2Д состоит в том, что на вход счетчика 2 с блока 1 поступает каждый второй (четный) тактовый импульс, на каждый из которых блок 1 формирует код считывания состояния тестируемой ячейки, а на каждый нечетный импульс формирует код операции согласно тестовой последовательности. Устройство позволяет осуществлять параллельный контроль нескольких мик росхем памяти одновременно. Технико-экономическое преимущест.во предлагаемого устройства заключается в более высоких, по сравнению с известным устройством, быстродейст вии и надежности при контроле неисправностей и времени хранения информации в БИС ОЗУ динамического и статического типа. Формула изобретения Устройство для контроля полупроводниковой оперативной , со- . держащее блок управления, счетчики, триггеры, группы элементов И и КОМ паратор, примем одни из выходов первого счетчика подключены к входам элементов И первой группы, а другой выход соединен с входом первого триг гера, входы сброса первого и второго счетчиков и первого и второго триггеров, управляющие входы элементов И первой и второй групп и компаратора и счетный вход первого счетчика подключены соответственно к одним из управляющих выходов блока управления,30 по

вход третьего триггера соединен с выходом компаратора, выходы триггеров подключены соответственно к одним из входов блока управления, информационные выходы которого и входы компаратора являются соответственно информационными выходами и входами устройства, отличающееся тем, что, с целью повышения быстродействия и надежности, устройства, в

венно с выходами элементов И, первой группы и с выходами элементов И второй группы.

Источники информации, принятые во вйимание при экспертизе

1.Авторское свидетельство СССР If 62217t, кл. 6 11 С 29/00, 1976.

2.Патент США ff 3805243,

кл. З«0- Й6.1, опублик. 1976 (про тотип). него введены дешифратор, третий счетчик, сумматоры по модулю два, выходы которых являются адресными выходами устройства, а одни из входов подключены к одним из выходов второго счетчика, и программируемый делитель частоты следования импульсов, вход сброса и счетный вход которого соединены соответственно с входами сброса третьего и первого счётчиков и с выходом первого триггера, а выход подключен к одному из входов дешифратора, другие входы которого соединены с входами элементов И второй группы и одними из выходов первого счетчика, один из выходов дешифратора подключен к счетному входу второго счетчика, другой выход которого соединен Ъо счетным входом третьего счетчика, один из выходов которого подключен к входу второго триггера, другие выходы дешифратора и третьего счетчика соединены соответственно с другими входами блока управления, другие управляющие выходы которого подключены соответственно к управляющим входам третьего триггера и программируемого делителя частоты следования импульсов, другие входы первого и второго сумматоров модулю два соединены соответстфиг.1

К9 К 10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

Авторы

Даты

1983-01-23—Публикация

1981-06-11—Подача