Изобретение относктся к электро- радиоиэмерительной технике и может быть использовано для измерения частоты и периода исследуемого сигнала,

Цель изобретения - повьппение точности и помехоустойчивости измерения частоты и периода исследуемых сигналов без увеличения времени измерения и частоты генератора эталонной частоты.

Цель достигается введением в известное устройство блока управления арифметического блока и блока нормировки и индикации, позволяющих изменить алгоритм обработки подсчитываемых импульсов генератора эталонной частоты и тем самым уменьшить . дисперсию случайной погрешности.

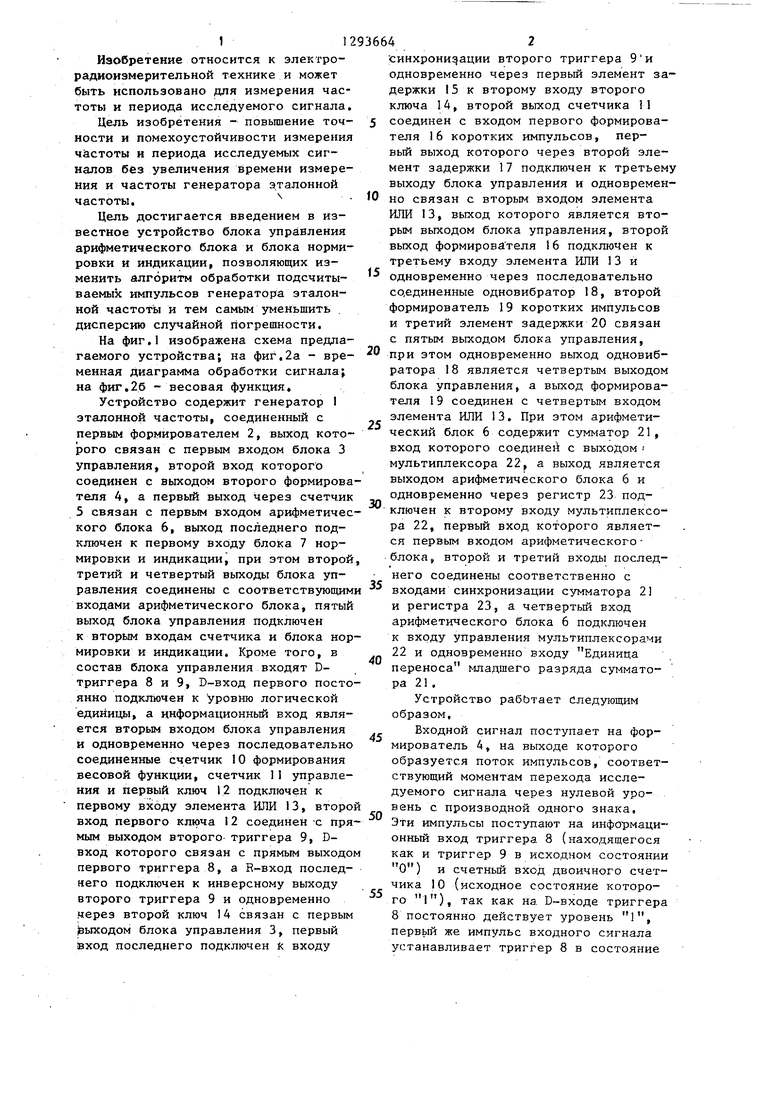

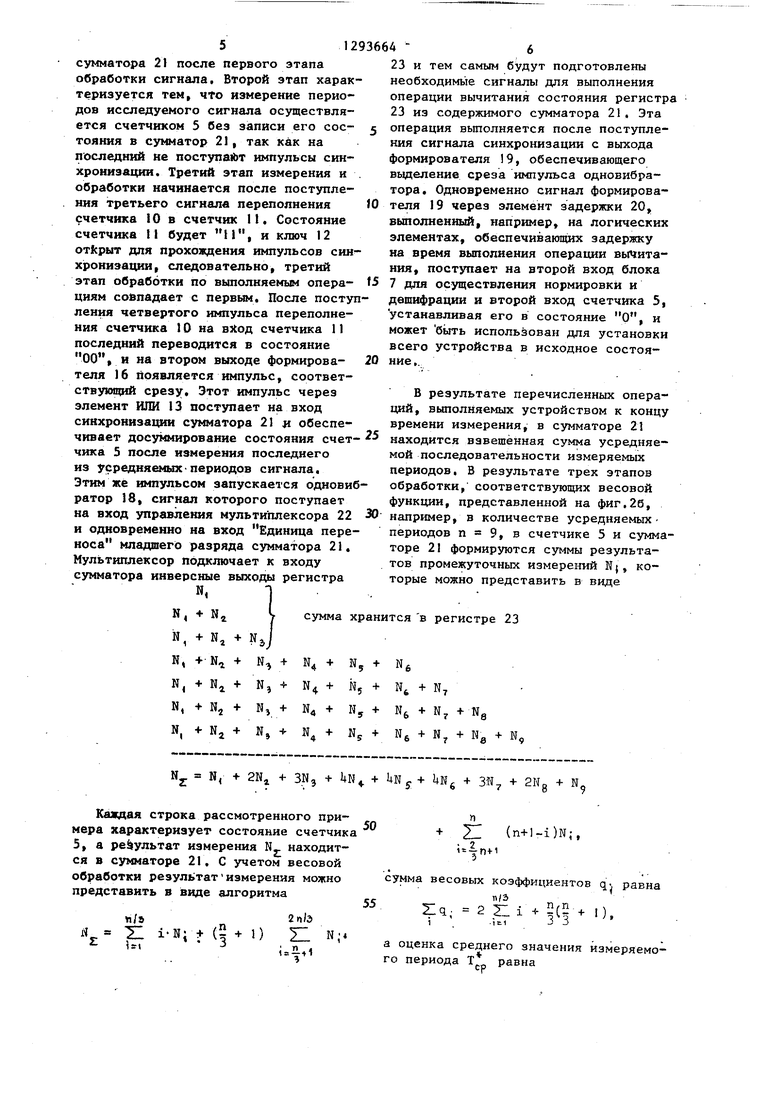

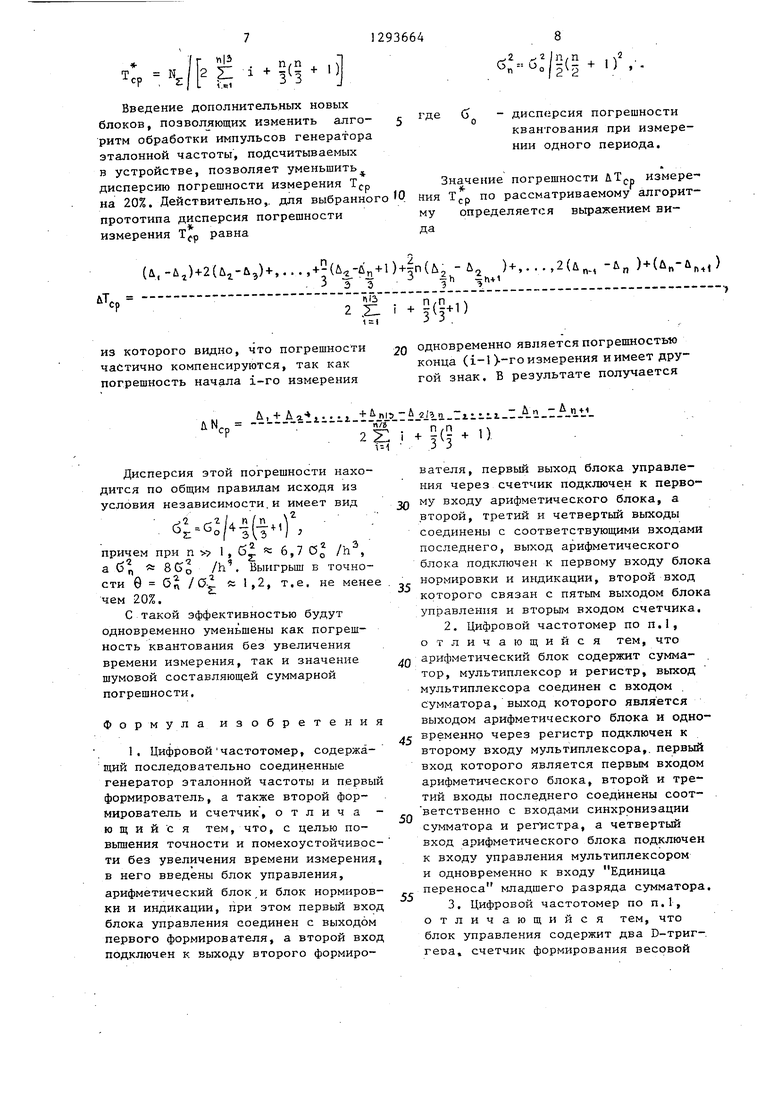

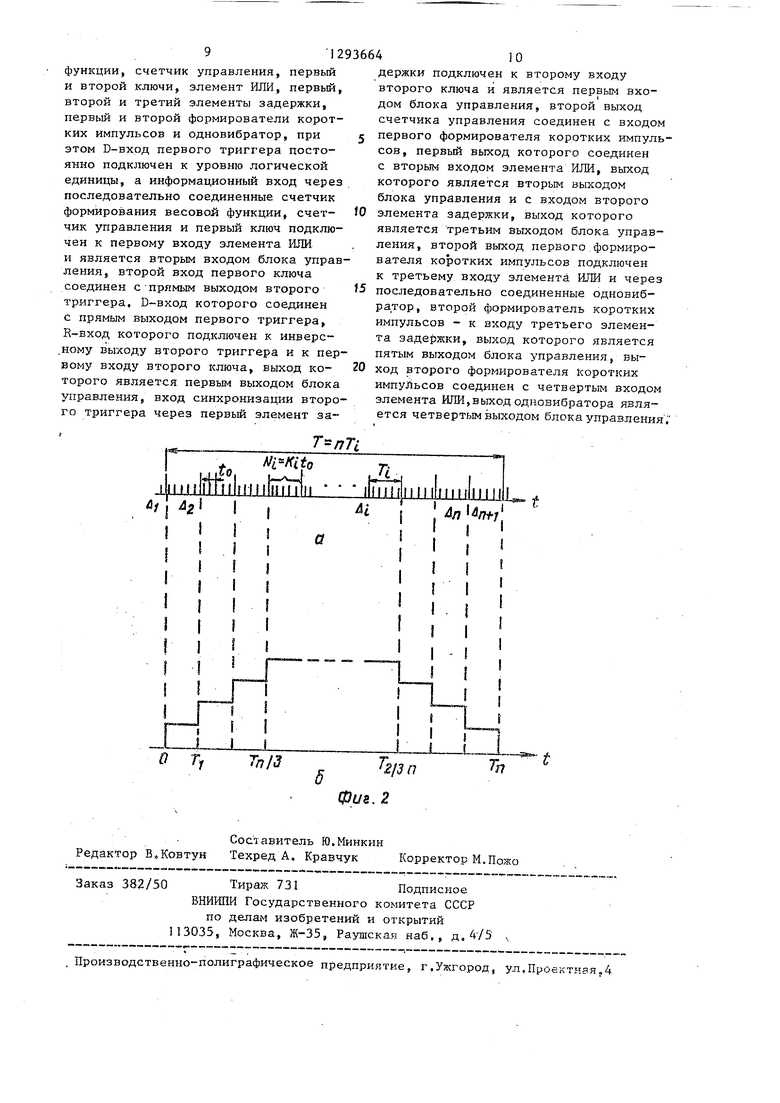

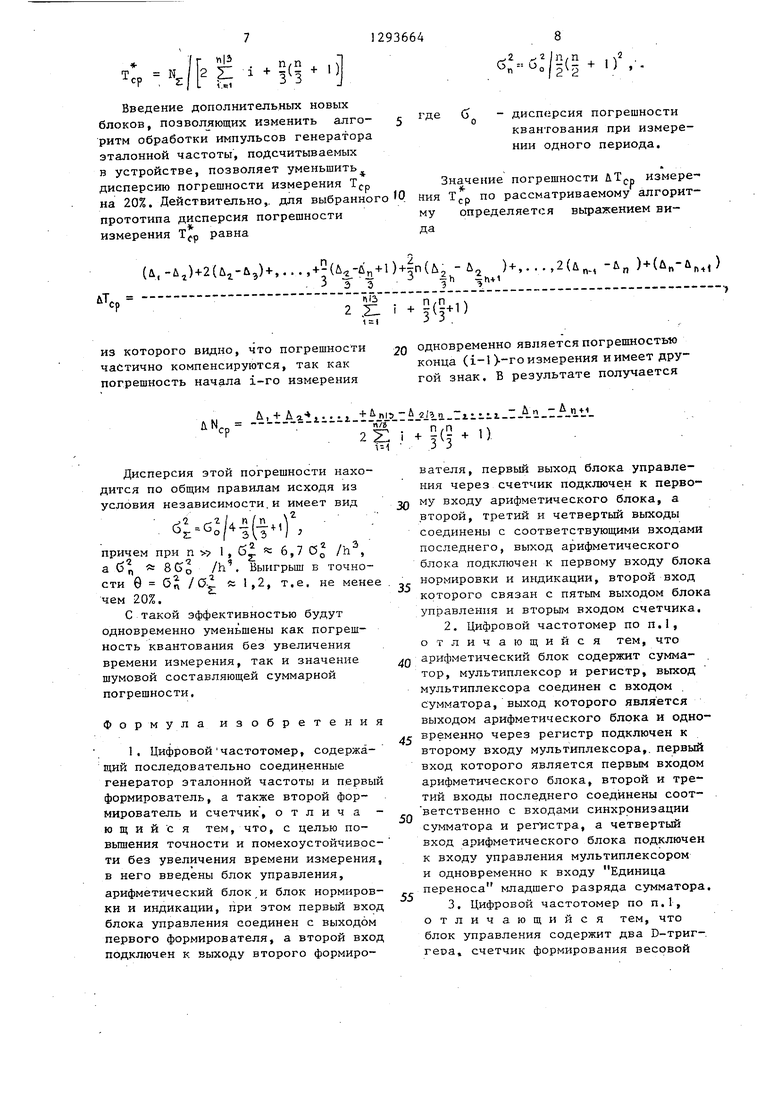

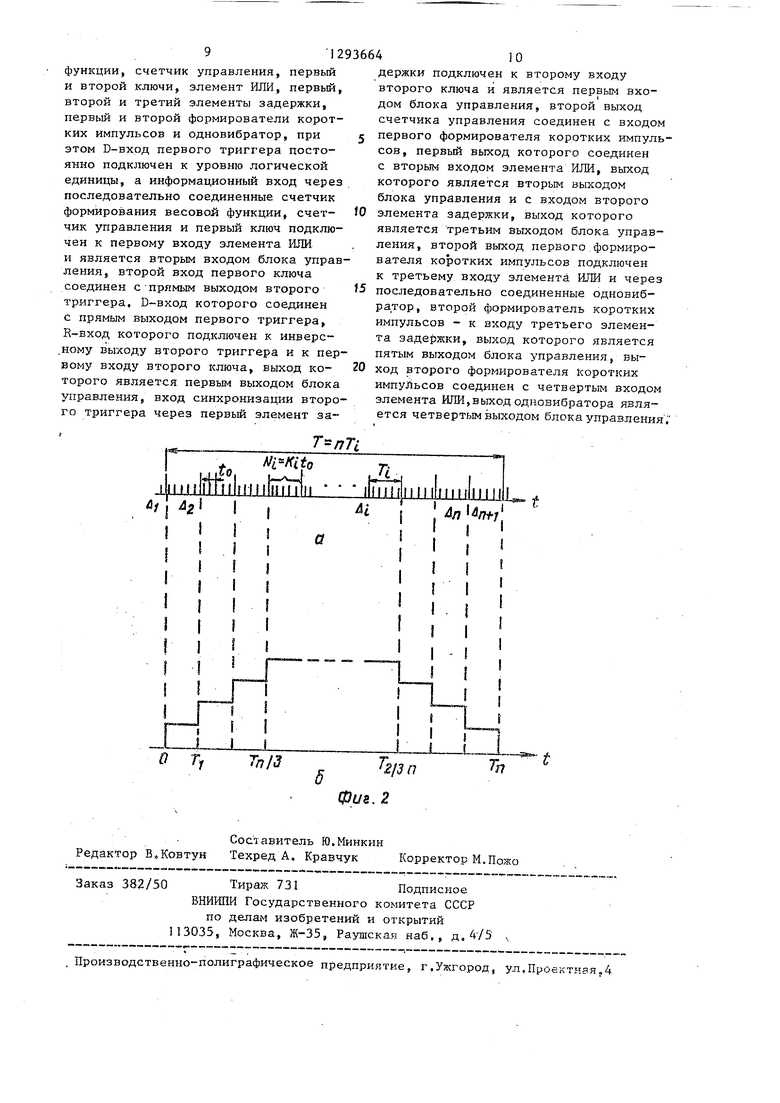

На фиг,1 изображена схема предлагаемого устройства; на фиг.2а - временная диаграмма обработки сигнала на фиг.2б - весовая функция,

Устройство содержит генератор I эталонной частоты, соединенный с первым формирователем 2, выход кото- jporo связан с первым входом блока 3 управления, второй вход которого соединен с выходом второго формирователя 4, а первый выход через счетчик 5 связан с первым входом арифметического блока 6, выход последнего подключен к первому входу блока 7 нормировки и индикации при этом второй третий и четвертый выходы блока управления соединены с соответствующими входами арифметического блока, пятый выход блока управления подключен к вторым входам счетчика и блока нормировки и индикации. Кроме того, в состав блока управления входят D- триггера 8 и 9, D-вход первого постоянно подключен к Уровню логической единигды, а информационный вход является вторым входом блока управления и одновременно через последовательно соединенные счетчик 10 формирования весовой функции, счетчик 1I управления и первый ключ 12 подключен к первому входу элемента ИЛИ 13, второй вход первого ключа 12 соединен -с прямым выходом второго триггера 9, D- вход которого связан с прямым выходом первого триггера 8, а R-вход последнего подключен к инверсному выходу второго триггера 9 и одновременно нерез второй ключ 14 связан с первым рыходом блока управления 3, первый вхоя последнего подключен к входу

5

0

5

0

5

0

5

0

5

синхронизации второго триггера 9 и одновременно через первый элемент задержки 15 к второму входу второго ключа 14, второй выход счетчика 11 соединен с входом первого формирователя 16 коротких импульсов, первый выход которого через второй элемент задержки 17 подключен к третьему выходу блока управления и одновременно связан с вторым входом элемента ИЛИ 13, выход которого является вторым выходом блока управления, второй выход формирователя 16 подключен к третьему входу элемента ИЛИ 13 и одновременно через последовательно соединенные одновибратор 18, второй формирователь 19 коротких импульсов и третий элемент задержки 20 связан с пятым выходом блока управления, при этом одновременно выход одновиб- ратора 18 является четвертым выходом блока управления, а выход формирователя 19 соединен с четвертым входом элемента ИЛИ 13. При этом арифметический блок 6 содержит сумматор 21, вход которого соединей с выходом мультиплексора 22, а выход является выходом арифметического блока 6 и одновременно через регистр 23 подключен к второму входу мультиплексора 22, первый вход которого является первым входом арифметического блока, второй и третий входы последнего соединены соответственно с входами синхронизации сумматора 21 и регистра 23, а четвертый вход арифметического блока 6 подключен к входу управления мультиплексорами 22 и одновременно входу Единица переноса младшего разряда сумматора 21 .

Устройство рабЬтает Следующим образом.

Входной сигнал поступает на формирователь 4, на выходе которого образуется поток импульсов, соответствующий моментам перехода исследуемого сигнала через нулевой уровень с производной одного знака. ЭТи импульсы поступают на информационный вход триггера 8 (находящегося как и триггер 9 в исходном состоянии О) и счетный вход двоичного счетчика 10 (исходное состояние которого 1), так как на D-входе триггера 8 постоянно действует уровень 1, первьй же импульс входного сигнала устанавливает триггер 8 в состояние

Ч, которое действует на D-входе

триггера 9, На вход синхронизации триггера 9 поступают импульсы эталонной частоты от формирователя 2, которые одновременно через элемент задержки 15 и ключ 14 поступают на счетный вход счетчика 5, Первый же импульс эталонной частоты, следующий за поступившим импульсом сигнала от формирователя 4, переводит триггер 9 в состояние 1, и на инверсном выходе триггера 9 устанавливается уровень О, который, воздейст- вуя на второй вход ключа 14, запрещающей прохождение импульсов эталонной частоты на счетчик 5, следовательно, первый импульс эталонной частоты, проходя через элемент задерки 15 (выполненный, например, на логических элементах, обеспечивающих задержку на время переключения триггера 9) не поступает на вход счетчика 5. Одновременно уровень О с инверсного выхода триггера 9, воздействуя на R-вход триггера 8 переводит его в исходное состояние и на D- входе триггера 9 устанавливается уровень О, а второй импульс эталонной частоты переводит триггер 9 в исходное состояние. На инверсном выходе триггера 9 устанавливается уровень 1 и последующие импульсы образцовой частоты (начиная со второго) поступает на вход счетчика 5 (находящегося в исходном состоянии О) и обеспечивают измерение первого периода исследуемого сигнала на . первом этапе измерения и обработки. Исключение по одному импульсу эталонной частоты в каждом измеряемом периоде сигнала выполняется за все время измерения, что создает необходимый запас для записи состояния счетчика 5 через мультиплексор 22 в сумматор 2I. Недостающее количество импульсов эталонной частоты в конечном результате измерения при известном количестве усредняемых периодов учитывается в блоке 7 при нормировке и дешифрации. После первого измерения первого периода сигнала его числовой код N, находится а счетчике 5 и с приходом второго импульса от формирователя 4 вновь триггер 8 переводится в состояние 1, которое по Очередному импульсу эталонной частот устанавливается на прямом выходе триггера 9. Импульсы, сформированные

10

15

20

293664 .

на прямом выходе триггера 9+ поступа-- ют на вход ключа 12, на другом входе которого действует уровень 1 от триггера младшего разряда двоичного счетчика управления 1I (двухразрядный, а исходное состояние - О), считающего импульсы переполнения счетчика 10, Емкость счетчика 10 выбирается равной п/3 и после поступления первого импульса сигнала от формирователя 4 он переполняется, и сигнал переполнения переводит -триггер младшего разряда счетчика I1 в состояние 1, которое устанавливается на управляющем входе ключа 12. Второй сигнал переполнения счетчика 10 поступает после .измерения и обработки Г/З усредняемых, периодов исследуемого сигнала, следовательно, в течение первого этапа измерения на управляющем входе ключа 12 поддерживается уровень 1 и импульсы, формируемые на прямом выходе триггера 9, после каждого импульса исследуемого сигнала поступают через ключ 12 и элемент ИЛИ 13 на вход синхронизации сумматора 21 и обеспечивают запись состояния счетчика 5 после каждого промежуточного измерения,

IВторой сигнал переполнения счетчика 10 является сигналом окончания первого этапа измерения и обработки. Триггер младшего разряда счетчика

I1переводится в состояние О и

35 ключ 12 будет закрыт на время, равное второй 1/3 части усредняемых периодов -сигнала, и импульсы синхронизации не поступают на сумматор 21, Одновременно с триггером младшего разряда счетчика 11 триггер старше- го разряда переводится в состояние

25

30

40

1 и на первом выходе формирователя 16 j выполненного, например, на логических элементах, обеспечивающих

45 выделение фронта и среза, появляется импульс, соответствующий фронту входного сигнала, который через элемент . ИЛИ 13 поступает на вход синхронизации сумматора 21 и обеспечивает до50 суммирование последнего состояния

счетчика 5 на первом этапе обработки. Этот же импульс с формирователя 16 через элемент задержки 17 (выполненный, например, на логических элемен55 тах, обеспечивающих задержку на время досуммирования) поступает на вход синхронизации регистра 23, и в регистр 23 будет переписано состояние

сумматора 21 после первого этапа обработки сигнала. Второй этап характеризуется тем, что измерение периодов исследуемого сигнала осуществляется счетчиком 5 без записи его состояния в сумматор 21, так как на последний не nocTynaibr импульсы синхронизации. Третий этап измерения и . обработки начинается после поступления третьего сигнала переполнения счетчика 10 в счетчик П. Состояние счетчика II будет II, и ключ 12 oTJkpbiT для прохождения импульсов син1293664 -6

23 и тем самым будут подготовлены необходимьте сигналы для выполнения операции вычитания состояния регистра 23 из содержимого сумматора 21, Эта 5 операция вьшолняется после поступления сигнала синхронизации с выхода формирователя 9, обеспечивающего выделение среза импульса одновибра- тора. Одновременно сигнал формирова- 10 теля 19 через элемент задержки 20, выполненный, например, на логических элементах, обеспечивающих задержку на время выполнения операции вычитания, поступает на второй вход блока

хронизации, следовательно, третий этап обработки по выполняемым опера- 5 7 для осуществления нормировки и циям совпадает с первым. После поступ- дешифрации и второй вход счетчика 5, ления четвертого импульса переполнения счетчика 10 на вход счетчика 11 последний переводится в состояние 00, и на втором выходе формирова- 20 теля 16 появляется импульс, соответствующий срезу. Этот импульс через элемент ИЛИ 13 поступает на вход синхронизаирии сумматора 2 л обеспе устанавливая его в состояние О, и может быть использован для установки всего устройства в исходное состояние,.

чивает досуммироваиие состояния счет чика 5 после измерения последнего из усредняемыхпериодов сигнала. Этим же импульсом запускается одновиб- ратор 18, сигнал которого поступает на вход управления мультиплексора 22 30 и одновременно на вход Единица переноса младшего разряда сумматора 21. Мультиплексор подключает к входу сумматора инверсные выходы регистра

В результате перечисленных операций, выполняемых устройством к концу времени измерения, в сумматоре 21 находится взвешенная сумма усредняемой последовательности измеряемых периодов, В результате трех этапов обработки, соответствующих весовой функции, представленной на фиг,2б, например, в количестве усредняемых- периодов п 9, в счетчике 5 и сумматоре 21 формируются суммы результатов промежуточных измерений N , которые можно представить в виде

Nj. Ы, + 2N4 + SNj + 1+N + UN J + UNg + + 2Ng + N Каждая строка рассмотренного при50

+ 21 (n+l-i)Nj,

50

+ 21 (n+l-i)Nj,

мера характеризует состояние счетчика 5, а результат измерения N, находится в сумматоре 21. С учетом весовой обработки результат измерения можно сумма весовых коэффициентов q. равна представить в виде алгоритма ,„/з

rq,. 2 r.i(2 I),

«/9гп/з

й- JL i-H; (2+1) г: N,4

Ui

UJ2-t1

7 для осуществления нормировки и дешифрации и второй вход счетчика 5,

устанавливая его в состояние О, и может быть использован для установки всего устройства в исходное состояние,.

7 для осуществления нормировки и ешифрации и второй вход счетчика 5,

В результате перечисленных операций, выполняемых устройством к концу времени измерения, в сумматоре 21 находится взвешенная сумма усредняемой последовательности измеряемых периодов, В результате трех этапов обработки, соответствующих весовой функции, представленной на фиг,2б, например, в количестве усредняемых- периодов п 9, в счетчике 5 и сумматоре 21 формируются суммы результатов промежуточных измерений N , которые можно представить в виде

UNg + + 2Ng + N

+ 21 (n+l-i)Nj,

весовых коэффициенто „/з

сумма весовых коэффициентов q. равна ,„/з

rq,. 2 r.i(2 I),

1 -1 1 -3 -

a оценка среднего значения измеряемого периода Т равна

ср

.4Ks-§ §-

Введение дополнительных новых блоков, позволяющих изменить алгоритм обработки импульсов генератора эталонной частоты, подсчитываемых в устройстве, позволяет уменьшить . дисперсию погрешности измерения Tj.p

где

- дисперсия погрешности квантования при измерении одного периода.

Значение погрешности измерена 20%. Действительно,, для выбранного Q Нин по рассматриваемому алгоритпрототипа дисперсия погрешности измерения равна

(Л,(Л1-Л,) + ,..., + + 1)+5п(Л2 -U2 ) + ,....2(Л„., -Л„ ) + (й„-й,,)

5 сц -1

Тс,из которого видно, что погрешности 20 одновременно является погрепшостыо частично компенсируются, так как конца (i-1 -го измерения и имеет дру погрешность начала i-ro измерения гой знак. Б результате получается

, А a iiiiii-t J i -3- iltL- Iii

tl/5 р. .- « -л , П / П .

2 Z1 I + 0(7 + П 1И 33

Дисперсия этой погрешности находится по общим правилам исходя из условия независимости и имеет вид

п / п

lU

) .

причем при п 1 , б. « 6,7 DO /h , а б,, «: 8Go /h . Выигрьш в точности О Gn /(3. , т.е. не менее чем 20%.

С такой эффективностью будут одновременно уменьшены как погрешность квантования без увеличения времени измерения, так и значение шумовой составляющей суммарной погрешности.

Формула изобретения

1, Цифровой частотомер, содержащий последовательно соединенные генератор эталонной частоты и первый формирователь, а также второй формирователь и счетчик , о т л и ч а ю щ и и с я тем, что, с целью по- вьш1ения точности и помехоустойчивости без увеличения времени измерения, в него введены блок управления, арифметический блок,и блок нормировки и индикации, при этом первый вход блока управления соединен с выходом первого формирователя, а второй вход подключен к выходу второго формиро.2 г 1п,п , ч2 °|2 2 + 1) .

где

- дисперсия погрешности квантования при измерении одного периода.

Значение погрешности измере по рассматриваемому алгоритНин по рассматриваемому алгори

му да

определяется выражением

2 .Ц i + 1 1J - .

.4t

5

0

вателя, первый выход блока управления через счетчик подключен к перво- Q му входу арифметического блока, а второй, третий н четверТЕДн выходы соединены с соответствующими входами последнего, выход арифметического блока подключен к первому входу блока нормировки и индикации, второй вход которого связан с пятым выходом блока управления и вторым входом счетчика.

2.Цифровой частотомер по п.1, отличающийся тем, что арифметический блок содержит сумматор, мультиплексор и регистр, выход мультиплексора соединен с входом сумматора, выход которого является выходом арифметического блока и одног временно через регистр подключен к второму входу мультиплексора,, первый вход которого является первым входом арифметического блока, второй и третий входы последнего соединены соответственно с входами синхронизации сумматора и регистра, а четвертый вход арифметического блока подключен к входу управления мультиплексором и одновременно к входу Единица переноса младшего разряда сумматора.

3.Цифровой частотомер по п.1, отличающийся тем, что блок управления содержит два Б-три:-. гера. счетчик формирования весовой

0

5

функции, счетчик управления, первый и второй ключи, элемент ИЛИ, первый, второй и третий элементы задержки, первый и второй формирователи коротких импульсов и одновибратор, при этом D-вход первого триггера постоянно подключен к уровню логической единицы, а информационный вход через последовательно соединенные счетчик формирования весовой функции, счетчик управления и первый ключ подключен к первому входу элемента ИЛИ и является вторым входом блока управления, второй вход первого ключа соединен с прямым выходом второго триггера. D-вход которого соединен с прямым выходом первого триггера, R-вход которого подключен к инверс- .ному выходу второго триггера и к первому входу второго ключа, выход которого является первым выходом блока управления, вход синхронизации второго триггера через первьй элемент заТ-лП

to

|ПН}Щ Г{|НН1 И11||||

I I

I I i

II

If

Q

Фив. 2

Составитель Ю.Минкин Редактор В,Ковтун Техред А. Кравчук Корректор М.Пожо

Заказ 382/50 Тираж 731Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб., д. 4-/S ,

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная.4

держки подключен к второму входу второго ключа и является первым входом блока управления, второй выход счетчика управления соединен с входом

первого формирователя коротких импульсов, первый выход которого соединен с вторым входом элемента ИЛИ, выход которого является вторым выходом блока управления и с входом второго

элемента задержки, выход которого

является третьим выходом блока управления, второй выход первого.формирователя коротких импульсов подключен к третьему входу элемента ИЛИ и через

последовательно соединенные одновибратор, второй формирователь коротких импульсов - к входу третьего элемента задержки, выход которого является пятым выходом блока управления, выход второго формирователя Коротких импуЛьсов соединен с четвертым входом элемента ИЛИ,выход одновибратора является четвертым выходом блока управления .

iHlllMlUllllli

Ai

АЛ 4/7f./ I

I i I .1 i

I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТРАНСПОРТНОГО ЗАПАЗДЫВАНИЯ СИГНАЛА В ТЕХНОЛОГИИ И ТЕХНИКЕ СВЯЗИ | 2003 |

|

RU2258938C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1987 |

|

SU1525609A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

Изобретение относится к электро- радиоизмерительной технике. Может быть использовано для измерения частоты и периода исследуемого сигнала. Цель изобретения - повышение точности и помехоустойчивости измерения частоты и периода исрледуемых сигналов без увеличения времени измерения и частоты генератора эталонной частоты. -Для достижения поотавленной цели в устройство введены блок 3 управления, арифметический блок 6, блок 7 нормировки и индикации. Устройство также содержит генератор 1 эталонной частоты, формирователи 2,4 и счетчик 5. В состав блока 3 управления входят D-триггеры 8 и 9, счетчик 10 формирования весовой функции, счетчик 1I управления, ключи 12,14, элемент 13 ИЛИ, элементы 15,17,20 задержки, формирователи 16,19 коротких импульсов, одновибратор 18. Арифметический блок 6 содержит сумматор 21, мультиплексор 22, регистр 23. Введение данных блоков в устройство позволяет изменить алгоритм обработки подсчитываемых импульсов генератора I эталонной частоты и тем самым уменьшить дисперсию случайной погрешности. 2 3. п. ф-лы, 2 ил. (Л 40f/e. /

| Устройство для установки крепи в очистных забоях | 1983 |

|

SU1211417A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель длительности периода | 1976 |

|

SU661382A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-28—Публикация

1985-06-07—Подача