Изобретение относится к вычислительной технике и может быть использовано для создания спецвычислителей,

Цель изобретения - расширение функциональных возможностей путем вычисления первой производной по формулам аппроксимации левой, правой и цент- ральной разностями и вычисления второй производной при аппроксимации центральной разностью.

На чертеже приведена схема устройства.

Устройство содержит блок 1 памяти таблиц сложения, регистр 2 предыдущего результата, блок 3 памяти адреса регистра, блок А регистровой памяти, сумматор 5 в избыточном коде, регистр 6 промежуточной суммы, входы 7-10 задания (j-l)-ro, j-ro и (j-M)-ro значений функции и исходных констант соответственно.

Схема работает следующим образом,

В соответствии с разностными алгоритмами первой и второй производных

U;

VX

.. VX

(1)

Y Hi-i-yi-- -.

ч 2чХ

Y|

Hi±..,

где

Y К

иУ

VX2

первая правая разностная производная;

первая левая и центральная разностные производные; вторая разностная производная ,

и - исходная функция. Как следует из (1), при дифференцировании выполняют операции сложение, деление (умножение на обратную величину).

Числитель формируется в блоках

Iи 3. Величины Uj , Uj, U., поступают последовательно разряд за разрядом соответственно на входы 7-9 устройства. В зависимости от состояния входов вычисляются числители переменных: 00 - YO, 01 - YJ ,

II YI . Операции, определенные

1G - .,

Y

в

числителе, выполняются для каждой цифры чисел.. В блоке 1 записаны таблицы операций, определенных в (1). Определяют максимальное число, получающееся При сложении. Так как обратной связи нет, то максимум- достига

5

0

5

0

5

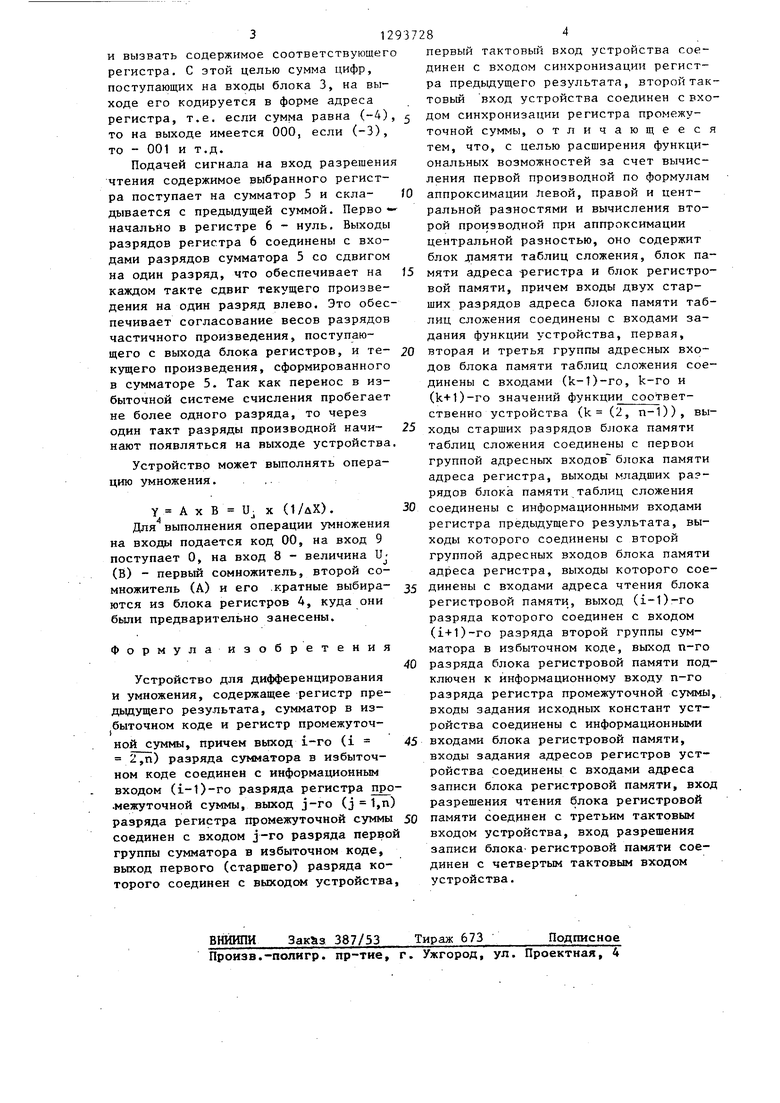

ется при сложении трех максимальных пифр. Кодирование цифр в четверичной системе следующее (О, +1, +2, -1), и для ликвидации пробела переноса бо- лее чем на два разряда допускаются цифры и -2. Поэтому положительное максимальное число получится при сложении цифр 3 - 2-(-2) + 3 22, а отрицательное число - при сложении цифр (-2) - 2- 3 + (-2) -22. Таким образом, на выходе блока 1 имеется двухразрядное число. Старший разряд поступает на блок 3 непосредственно, а младший - с задержкой на один такт. Роль задержки выполняет регистр 2, на вход синхронизации которого подается синхросерия. В результате на входы блока 3 приходят цифры одного веса. В блок 3 записана таблица сложения двух цифр. Максимальное значение суммы равно +4, минимальное равно -4. Таким образом, на выходе блока 3 должен был формироваться ряд -4, -3, -2, -1, О, +1, +2, +3, +4. На одну из цифр ряда необходимо произвести умножение числа l/vX, или 1/vX, или 1/2vX. С этой целью перед дифференцированием определяются кратные указанных величин и заносятся в блок 4 регистров. Занесение осуществляется подачей адреса на входы адреса записи, сигнала записи на вход разрешения записи и записываемой величины на вход 10. Соотношения между адресом и величиной, записанной в регистр, дано в таблице.

Примечание. А- 1/АХ .,

1/7Х, 1/2vX.

Таким образом, для умножения на 11ИФРУ необходимо сформировать адрес

и вызвать содержимое соответствующего регистра, С этой целью сумма цифр, поступающих на входы блока 3, на выходе его кодируется в форме адреса регистра, т.е. если сумма равна (-4), то на выходе имеется 000, если (-3), то - 001 и т.д.

Подачей сигнала на вход разрешения чтения содержимое выбранного регистра поступает на сумматор 5 и скла- дывается с предыдущей суммой. Перво начально в регистре 6 - нуль. Выходы разрядов регистра 6 соединены с входами разрядов сумматора 5 со сдвигом на один разряд, что обеспечивает на каждом такте сдвиг текущего произведения на один разряд влево. Это обеспечивает согласование весов разрядов частичного произведения, поступающего с выхода блока регистров, и те- кущего произведения, сформированного в сумматоре 5. Так как перенос в избыточной системе счисления пробегает не более одного разряда, то через один такт разряды производной начи- кают появляться на выходе устройства.

Устройство может выполнять операцию умножения. ,

Y А X В и X (1/дХ). Для выполнения операции умножения

на входы подается код 00, на вход 9 поступает О, на вход 8 - величина Uj (В) - первый сомножитель, второй сомножитель (А) и его .кратные выбира- ются из блока регистров 4, куда они были предварительно занесены.

Формулаизобретения

Устройство для дифференцирования И умножения, содержащее регистр предыдущего результата, сумматор в избыточном коде и регистр промежуточной суммы, причем выход i-ro (i 45 2,n) разряда сумматора в избыточном коде соединен с информационным входом (i-l)-ro разряда регистра про- межуточной суммы, выход j-ro (j 1,п) разряда регистра промежуточной суммы 50 соединен с входом j-ro разряда первой группы сумматора в избыточном коде, выход первого (старшего) разряда которого соединен с выходом устройства.

вниипи

Заказ 387/53

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Ш 15 0 5

0

5

0

5 0

первый тактовый вход устройства соединен с входом синхронизации регистра предыдущего результата, второй тактовый вход устройства соединен с входом синхронизации регистра промежуточной суммы, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления первой производной по формулам аппроксимации левой, правой и центральной разностями и вычисления второй производной при аппроксимации центральной разностью, оно содержит блок дтамяти таблиц сложения, блок памяти адреса зегистра и блок регистровой памяти, причем входы двух старших разрядов адреса блока памяти таблиц сложения соединены с входами задания функции устройства, первая, вторая и третья группы адресных входов блока памяти таблиц сложения соединены с входами (k-t)-ro, k-ro и (k-bl)-ro значений функции соответ- ственно устройства (k (2, п-1)), выходы старших разрядов блока памяти таблиц сложения соединены с первой группой адресных входов блока памяти адреса регистра, выходы младших разрядов блока памяти таблиц сложения соединены с информационными входами регистра предыдущего результата, выходы которого соединены с второй группой адресных входов блока памяти адреса регистра, выходы которого соединены с входами адреса чтения блока регистровой памяти, выход (i-l)-ro разряда которого соединен с входом (i+1)-ro разряда второй группы сумматора в избыточном коде, выход п-го разряда блока регистровой памяти подключен к информационному входу п-го разряда регистра промежуточной суммы, входы задания исходных констант устройства соединены с информационными входами блока регистровой памяти, входы задания адресов регистров устройства соединены с входами адреса записи блока регистровой памяти, вход разрешения чтения блока регистровой памяти соединен с третьим тактовым входом устройства, вход разрешения записи блока регистровой памяти соединен с четвертым тактовым входом устройства.

Тираж 673

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для обработки чисел в избыточном последовательном коде | 1985 |

|

SU1330629A1 |

| Цифровой фильтр | 1986 |

|

SU1354393A1 |

Изобретение относится к вычислительной технике и может быть использовано в спецвьгчислителях для решения задач, связанных с вычислением производной. Цель изобретения - расширение функциональных возможностей. Устройство содержит два блока 1, 3 памяти, два регистра 2, 6, блок 4 регистровой памяти и сумматор 5. Устройство функционирует в избыточном (четвертичном) коде, за счет этого достигается повышение быстродействия. 1 ил., 1 табл. iiilllm щ 4-2 Tii ю 1 - , f р-4лГ - . ,

| Устройство для дифференцирования | 1974 |

|

SU543000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-28—Публикация

1985-04-10—Подача