(ВР) 3, блок памяти (БП) 4, блоки преобразования кода 5.1 -5onij компараторы 6.1-6.т, счетчик 7, блок умножения 8, блок синхронизании 9 н инверторы 10, 11, Отсчеты входной и выходной последовательностей прсд-- ставляются т-разрядным двоичным дополнительным кодом. В каждом такте выполняются .следующие действия. Компараторы 6.1-6,m сравнивают коды с выходов блока преобразования кодов 5 с кодом счетчика 7, Результат сра

1

Изобретение относится к цифроу пй обработке сигналов и может бьт-. ic- поль-зовано в системах цифровой фильтрации в радиосвязи, радиолокации и радионавигации,

Цель изобретения - повыБ1ение -i г стродействия цифрового фильтра,

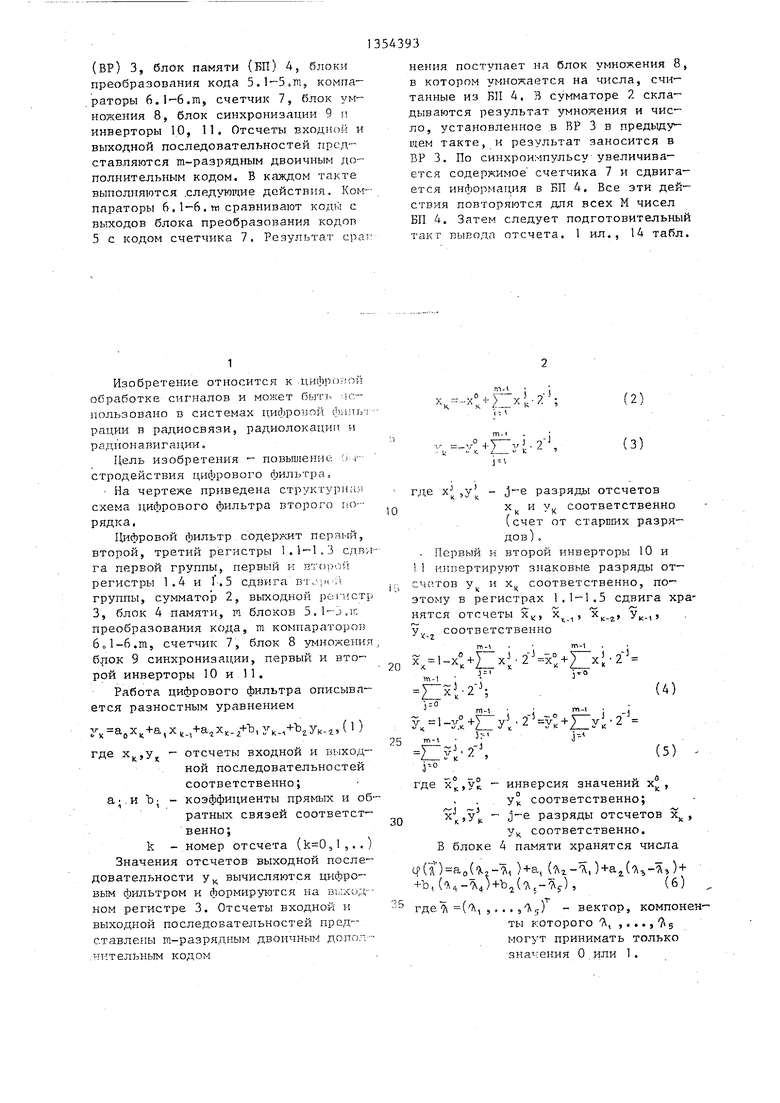

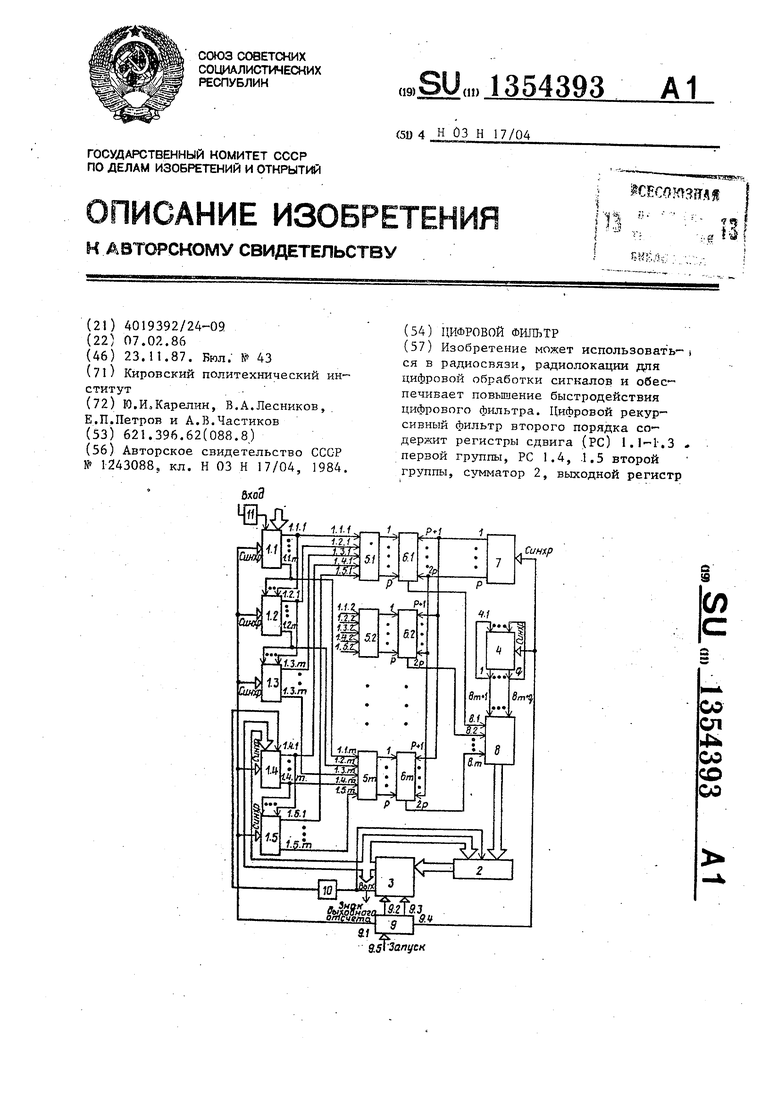

На чертеже приведена структурная схема цифрового фильтра второго порядка.

Цифровой фильтр содержит парами, второй, третий регистры 1,1-1,3 сдвига первой группы, первый и BTovjoii регистры 1.4 и 1-.5 сдвига вчч;in iv группы, сумматор 2, выходной регистр 3, блок 4 памяти, и блоков 5.1-j.in преобразования кода, m компараторов б „1-6 .т, счетчик 7, блок 8 блок 9 синхронизации, первый и второй инверторы 10 и П.

Работа цифрового фильтра описывается разностным уравнением

,х,..,у..,.,(1 )

где Х|,У| - отсчеты входной и выходной последовательностей соответственно;

а .и Ъ; - коэффициенты прямых и обратных связей соответственно;

k - номер отсчета (,l,..) Значения отсчетов выходной последовательности у вычисляются цифровым фильтром и формируются на выход-ном регистре 3. Отсчеты входной и выходной последовательностей представлены т-разрядным двоичным доппл-- .ннтельным кодом

нения поступает на блок умножения 8, в котором умножается на числа, считанные из БП 4, 3 сумматоре 2 складываются результат умножения и число, установленное .в ВР 3 в предьщу- щем такте, и результат заносится в ВР 3. По синхроимпульсу увеличивается содержимое счетчика 7 и сдвигается информация в БП 4, Все эти действия повторяются для всех М чисел БП 4, Затем следует подготовительный такт вывода отсчета. 1 ил,, 14 табл.

vi,9„ к - 5

(2) (3)

где х- svj, - j-e разряды отсчетов

X, и у,, соответственно

. k - к.

( счет от старпшх разрядов) о

- Первый и второй инверторы 10 и 11 инвертируют знаковые разряды от- у, и х, соответственно, поэтому в регистрах 1.1-1,5 сдвига хранятся отсчеты X,

к соответственно

х, их%Пх 2- х Х1х:.2-

. г ZIS1 2

(4)

V

m-i : m-i ,

-i-y.MIyt 2 -yMlyi 2-

тм . 5 j--

г:y 2r-° .

(5)

где x,y°

0

л-( j

ч У к

инверсия значении х, у° соответственно; j-e разряды отсчетов х, Уц соответственно. В блоке 4 памяти хранятся числа

Ч (я )а,и,-7 )+а, (-Лг-, }+8.(,,-7(} + +Ъ, ( X4- A4.)+b2(),(6)

где 7 ( Л, ,, . . з Х) - вектор, компоненты которого Л, ,,.., Дд могут принимать только значения О или 1.

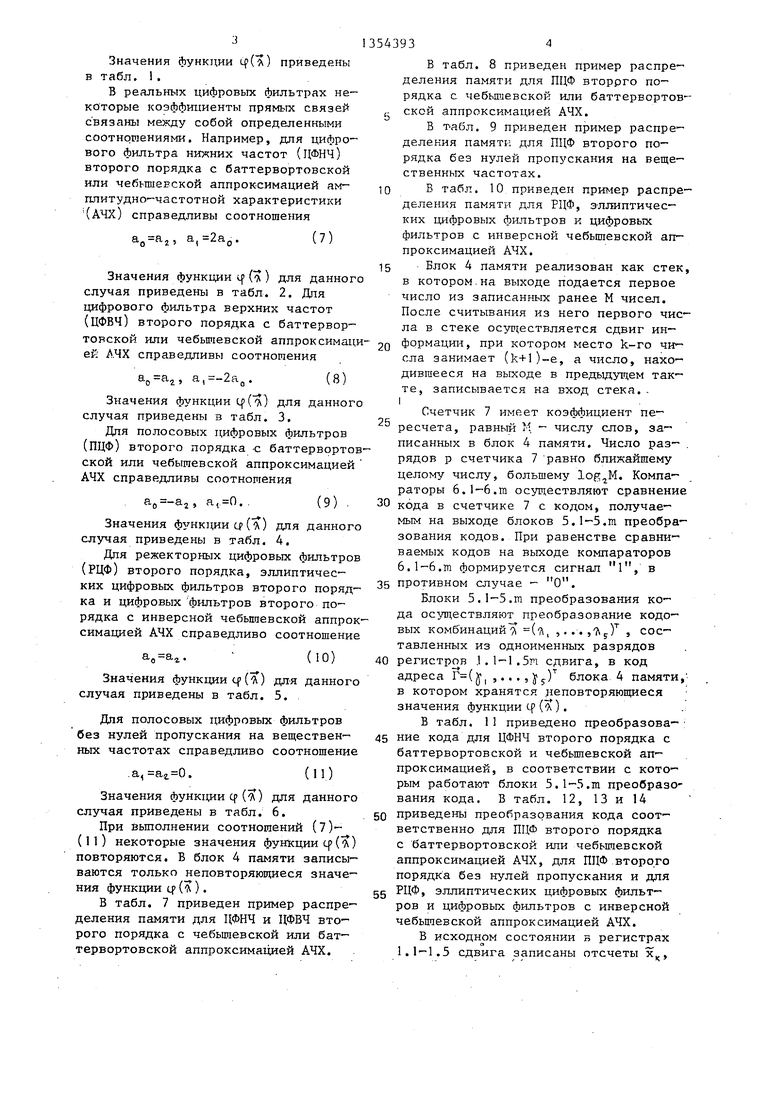

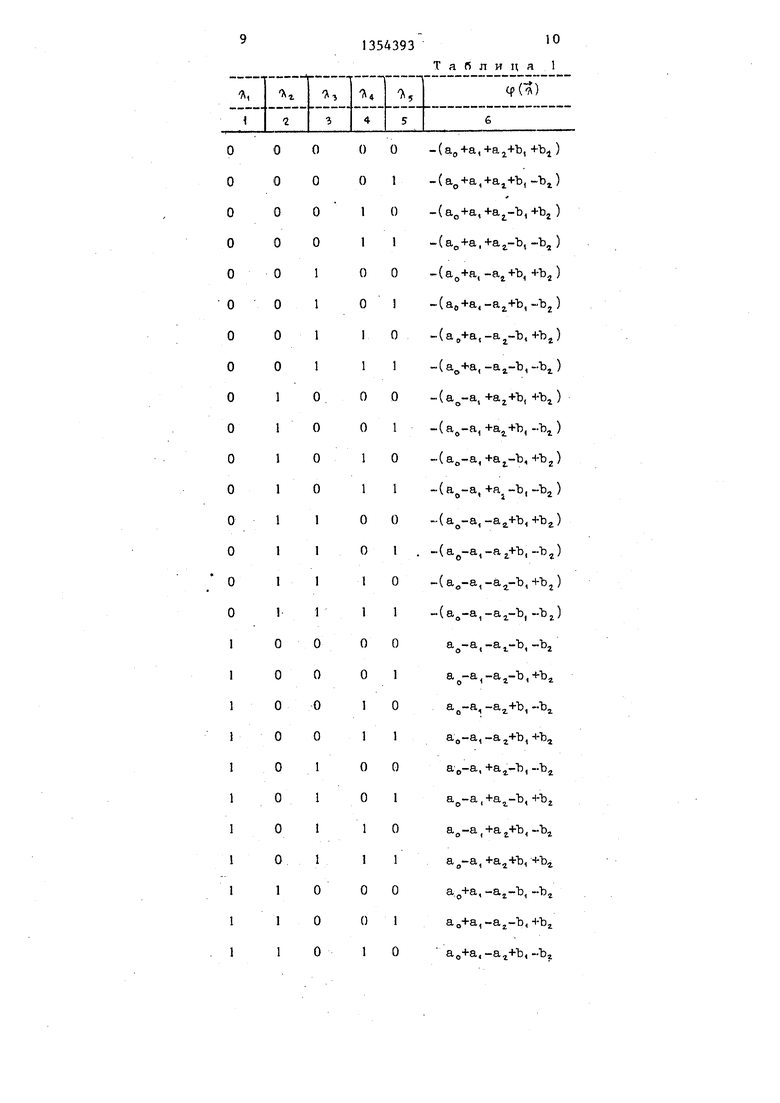

Значения функции ifC) приведены в табл. 1.

В реальных цифровых фильтрах некоторые коэффициенты прямых связей связаны между собой определенными соотноиениями. Например, для цифрового фильтра нижних частот (ЦФНЧ) второго порядка с баттервортовской или чебьшевской аппроксимацией амплитудно-частотной характеристики (АЧХ) справедливы соотношения

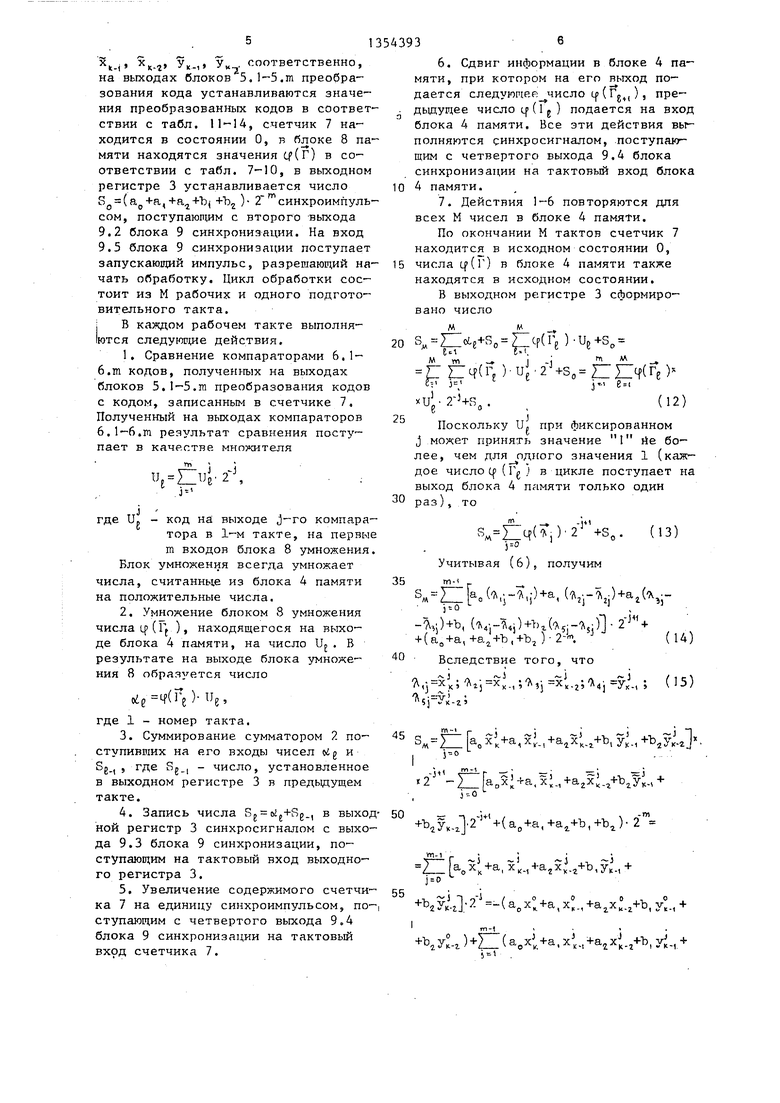

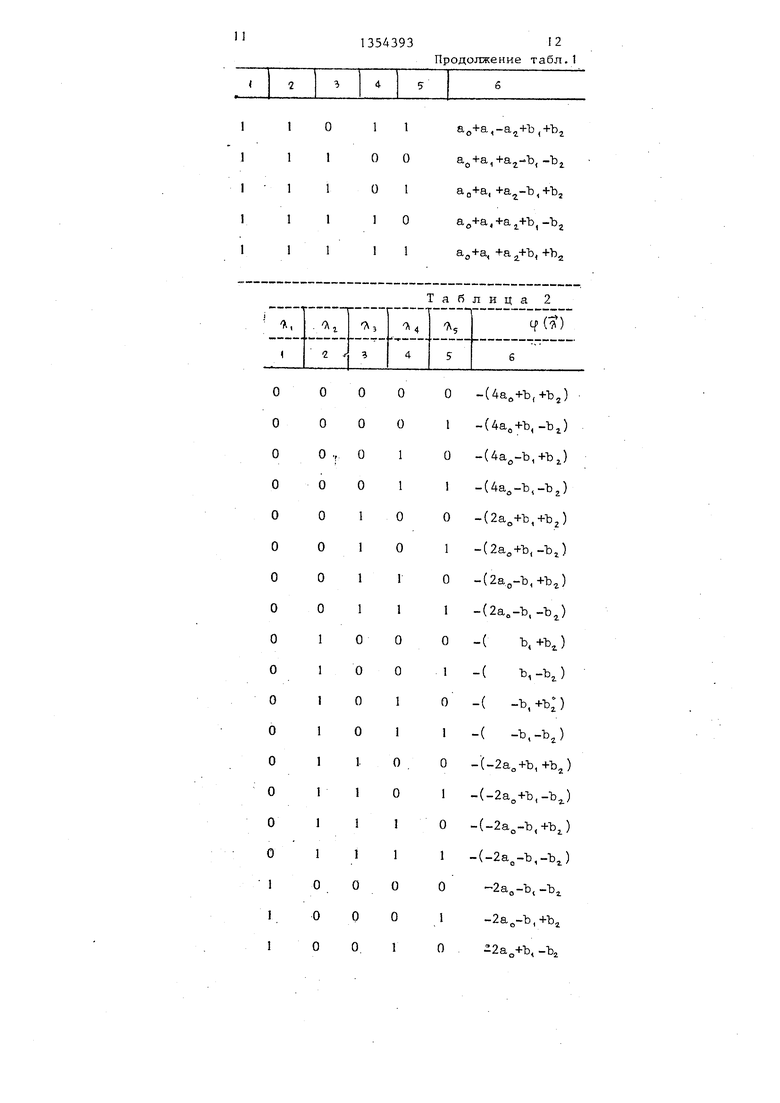

Значения функции if С ) для данного случая приведены в табл. 2. Дпя цифрового фильтра верхних частот (ЦФВЧ) второго порядка с баттервор- товской или чебьшшвской аппроксимаци ей А.ЧХ справедливы соотношения

а(,а, а,-2ад. (8)

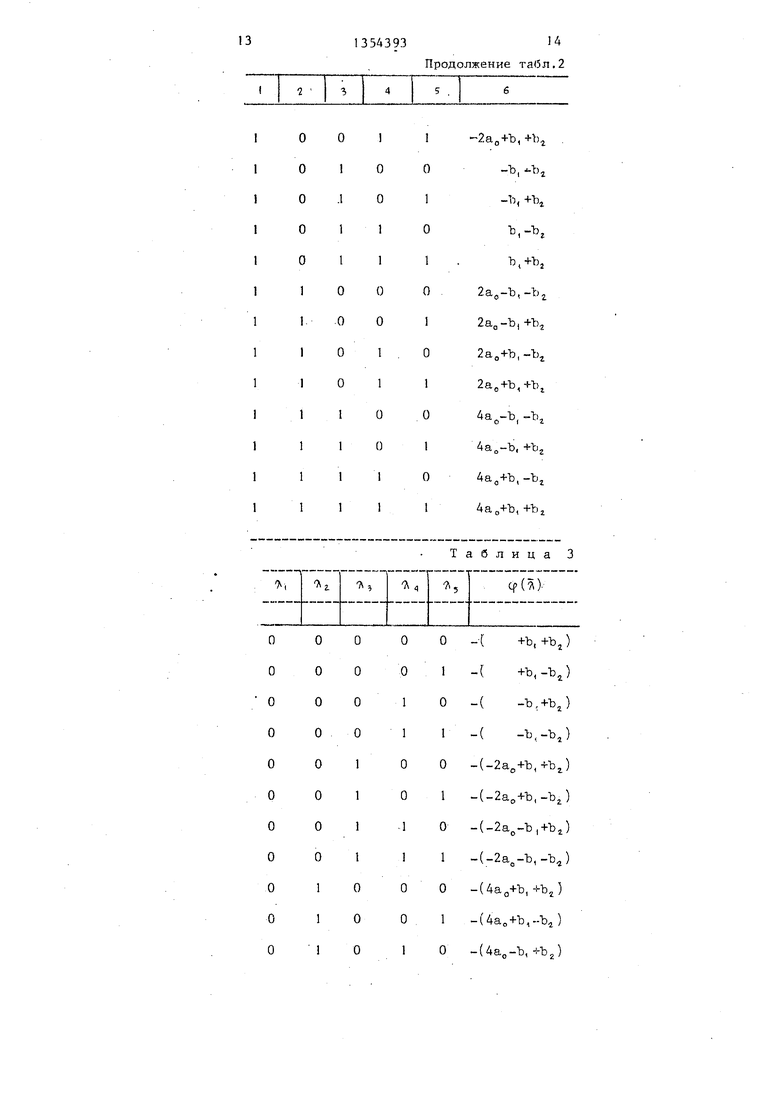

Значения функции Ц С л) для данного случая приведены в табл. 3.

Дпя полосовых цифровых фильтров (ПЦФ) второго порядка -с баттервортов ской или чебыгаевской аппроксимацией АЧХ справедливы соотноиения

(9) .

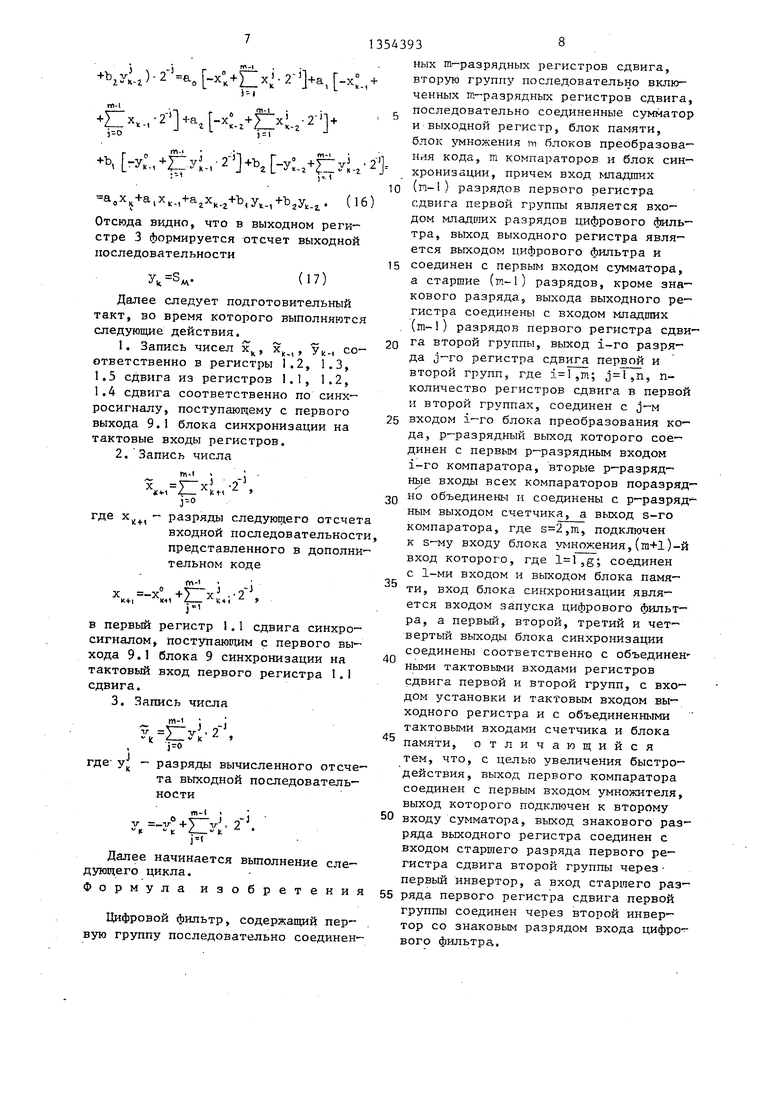

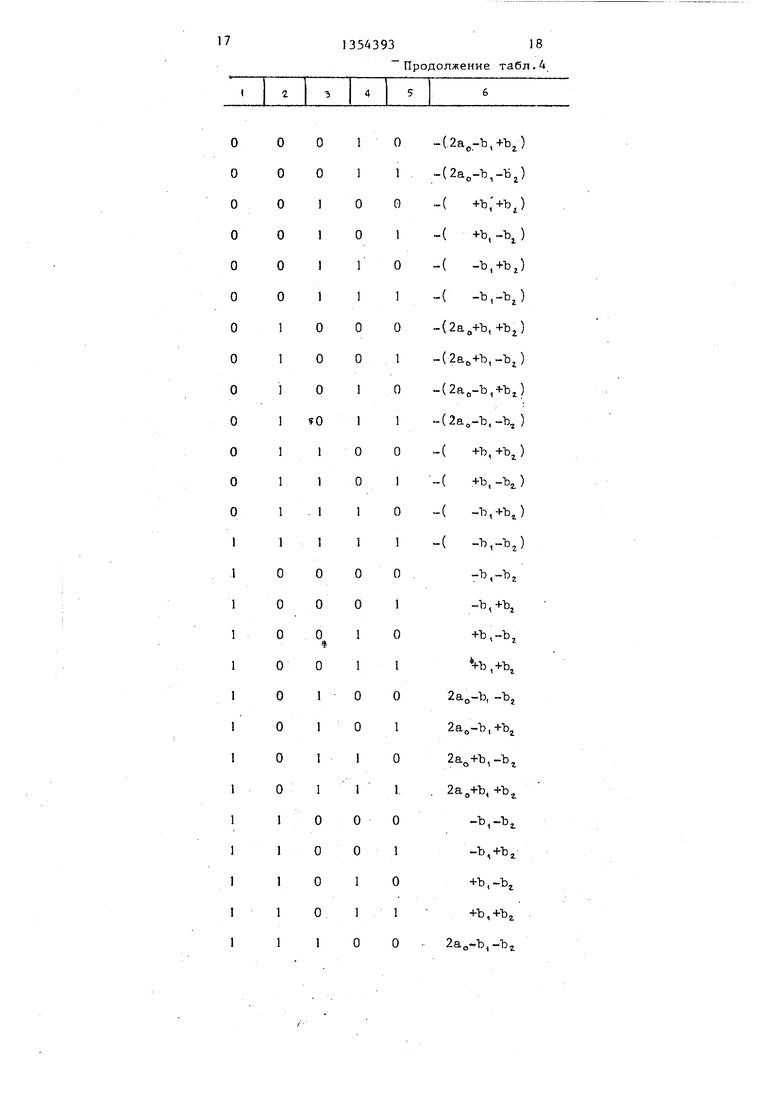

Значения функции cf С) для данного случая приведены в табл. 4.

Дпя режекторных цифровых фильтров (РЦф) второго порядка, эллиптических цифровых фильтров второго порядка и цифровых фильтров второго порядка с инверсной чебьшевской аппроксимацией АЧХ справедливо соотношение

а,а. (10)

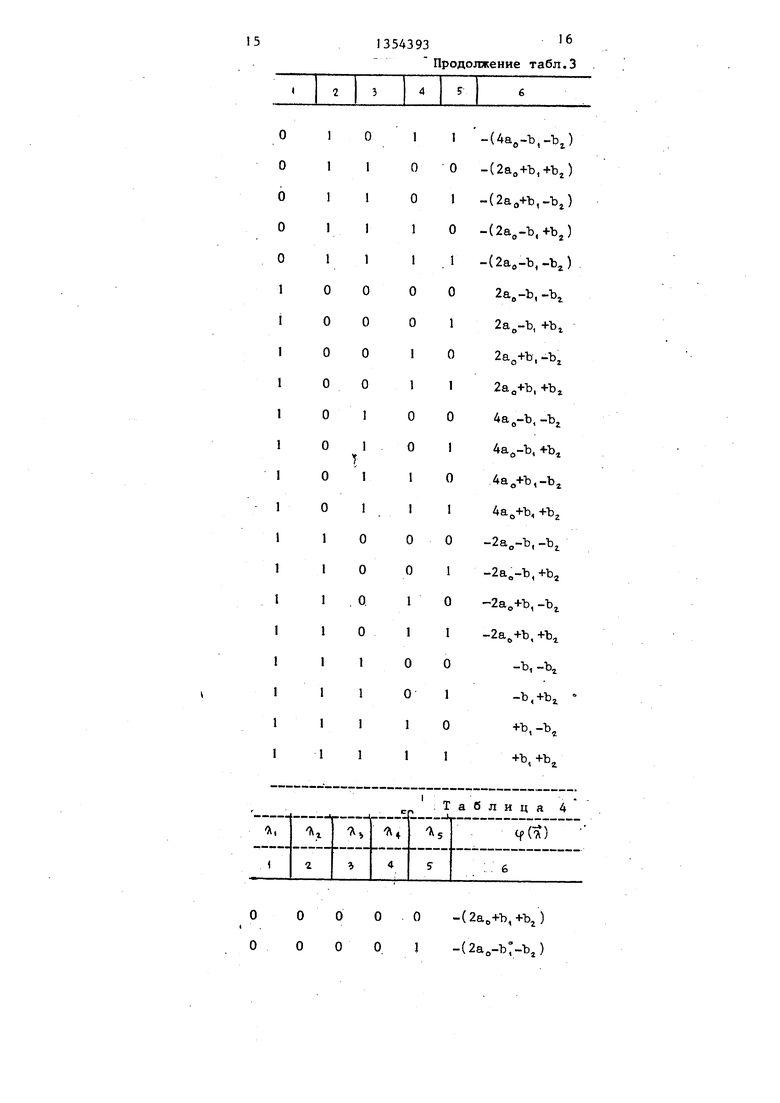

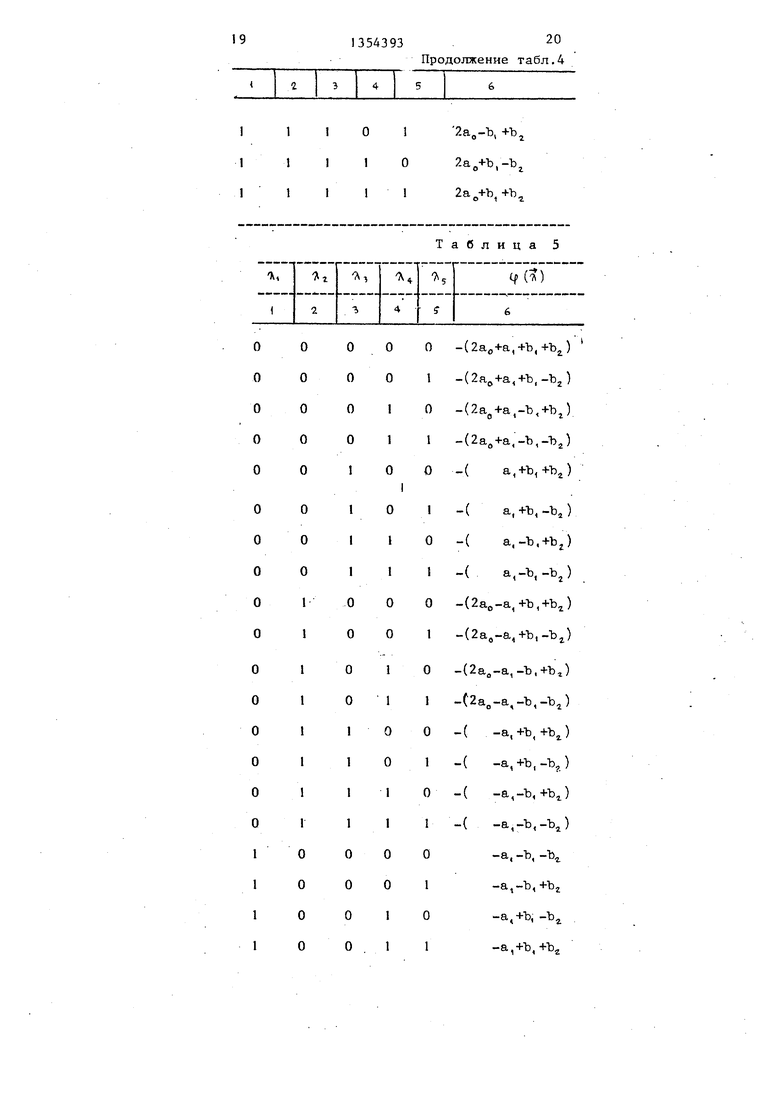

Значения функции tfC) дл-я данного случая приведены в табл. 5.

Для полосовых цифровых фильтров без нулей пропускания на вещественных частотах справедливо соотношение

.а, аг.0.(И)

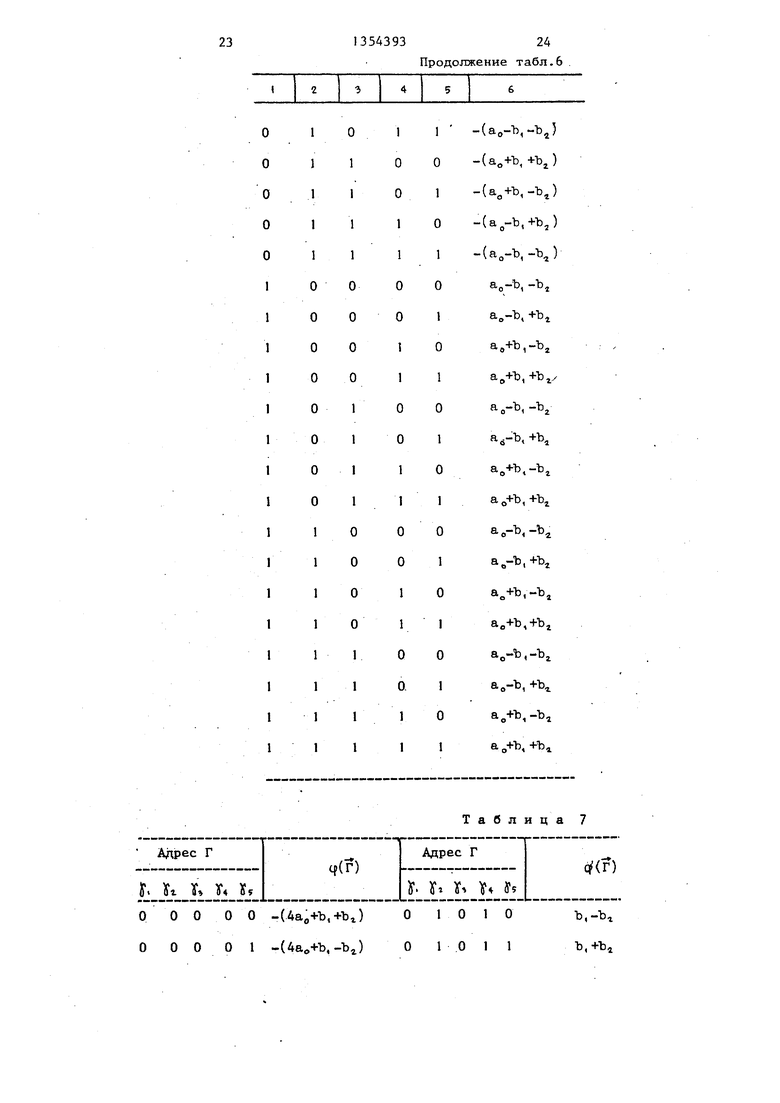

Значения функ1щи ср () для данного случая приведены в табл. 6.

При выполнении соотношений (7)- (11) некоторые значения функции ср() повторяются. В блок 4 памяти записываются только неповторяющиеся значения функции q ().

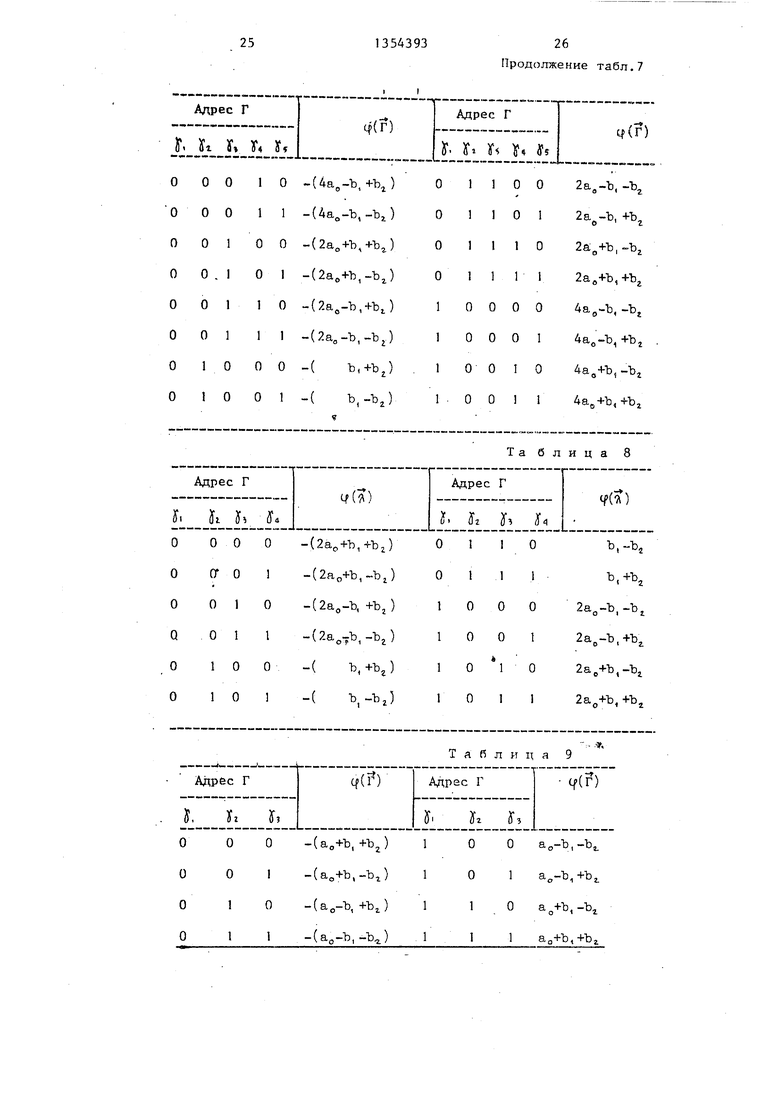

В табл. 7 приведен пример распределения памяти для ЦФНЧ и ЦФВЧ второго порядка с чебьш1евской или бат- тервортовской аппроксимацией АЧХ.

543934

В табл. 8 приведен пример распределения памяти для ПЦФ вторрго порядка с чебышевской или баттервортов- g ской аппроксимацией АЧХ.

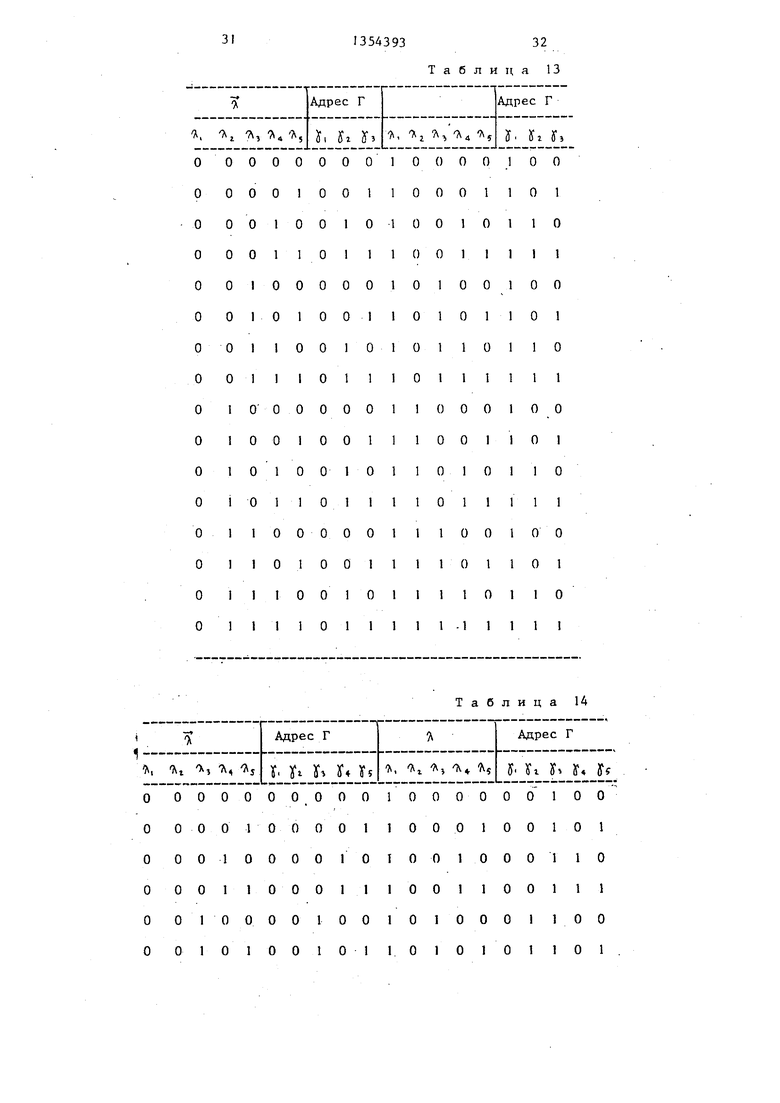

В табл. 9 приведен пример распределения памяти для ПЦФ второго порядка без нулей пропускания на вещественных частотах.

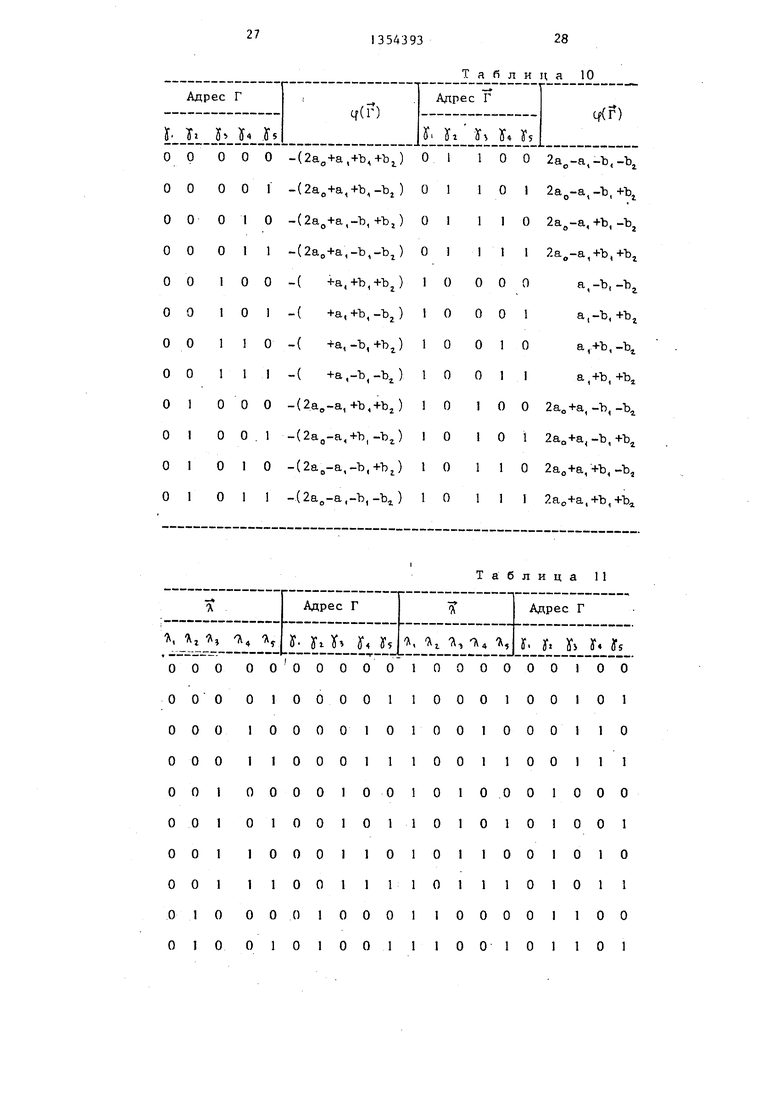

10 В табл. 10 приведен пример распределения памяти для РЦФ, эллиптических цифровых фильтров и цифровых фильтров с инверсной чебышевской аппроксимацией АЧХ.

15 Блок 4 памяти реализован как стек, в котором.на выходе подается первое число из записанных ранее М чисел. После считывания из него первого числа в стеке осуп ествляется сдвиг ин- 20 формации, при котором место k-ro чи ела занимает (k+1)-е, а число, находившееся на выходе в предьщутцем такте, записывается на вход стека.. I

Счетчик 7 имеет коэффициент пе-

ресчета, равный М - числу слов, записанных в блок 4 памяти. Число раз- . рядов р счетчика 7 равно ближайшему целому числу, большему . Компараторы 6.1-6.га осуществляют сравнение

30 кода в счетчике 7 с кодом, получаемым на выходе блоков 5.1-5.m преобразования кодов. При равенстве сравниваемых кодов на выходе компараторов 6.1-6.т формируется сигнал 1, в

35 противном случае - О.

Блоки 5.1-5.га преобразования кода осуществляют преобразование кодовых комбинаций (1, ,... ,7) 5 составленных из одноименных разрядов

40 регистров .1.1-1.5П сдвига, в код

адреса Г(у| ,...,5-) блока. 4 памяти, в котором хранятся деповторяющиеся значения функции tp (9).

В табл. 1 приведено преобразова- ;

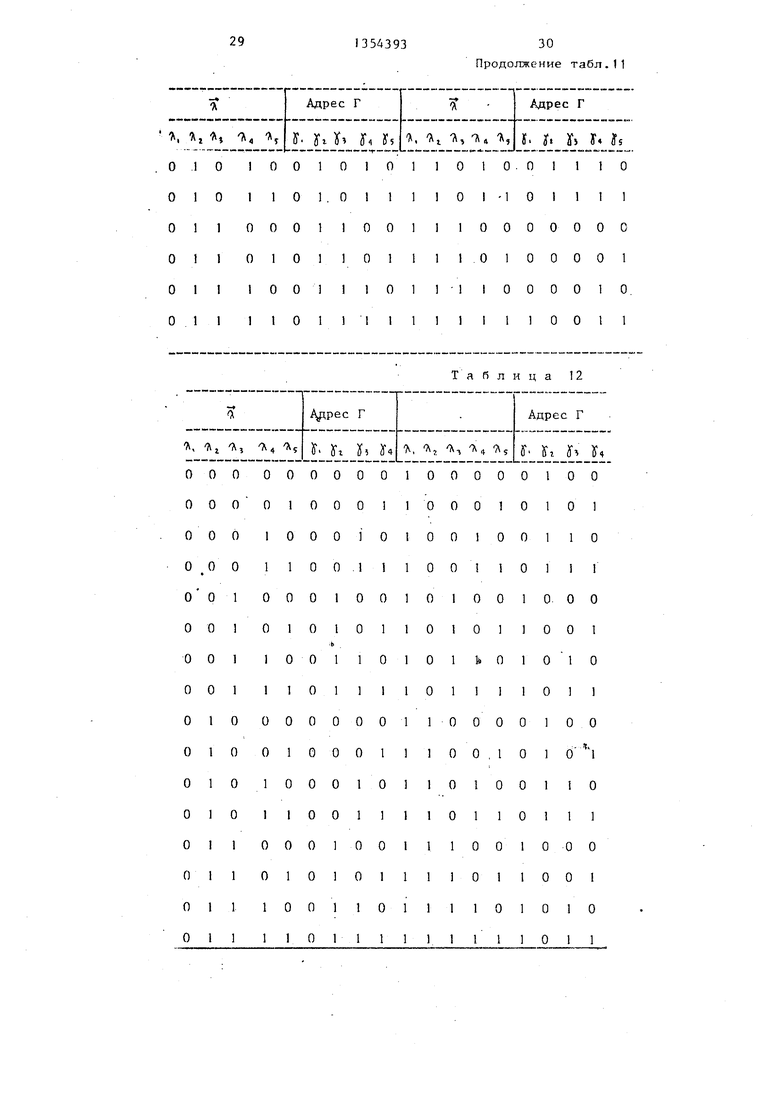

45 ние кода для ЦФНЧ второго порядка с баттервортовской и чебьшевской аппроксимацией, в соответствии с которым работают блоки 5.1-5.m преобразования кода. В табл. 12, 13 и 14

50 приведены преобразования кода соответственно для ПЦФ второго порядка с баттервортовской или чебьшевской аппроксимацией АЧХ, для ПЦФ второ.го порядка без нулей пропускания и для

55 РЦФ, эллиптических цифровых фильтров и цифровых фильтров с инверсной чебьппевской аппроксимацией АЧХ.

В исходном состоянии н регистрах 1.1-1.5 сдвига записаны отсчеты х,

k-i -г «7 « - ответственно, на выходах блоков 5,1-5.т преобрн зования кода устанавливаются значения преобразованных кодов в соответствии с табл. 11-14, счетчик 7 находится в состоянии О, в блоке 8 памяти находятся значения Cf( г) в соответствии с табл. 7-10, в выходном регистре 3 устанавливается число 8д (ар+а,( +Ъ ) 2 синхроимпульсом, поступаюпи1м с второго -выхода 9.2 блока 9 синхронизации. На вход 9.5 блока 9 синхронизации поступает запускающий импульс, разрешающий начать обработку. Цикл обработки состоит из М рабочих и одного подготовительного такта.

В каждом рабочем такте выполняются следуюпще действия.

1. Сравнение компараторами 6.1- б.т кодов, полученных на выходах блоков 5.1-5.т преобразования кодов с кодом, записанным в счетчике 7. Полученный на выходах компараторов 6.1-6.т результат сравнения поступает в качестве множителя

Е

,,J .,-J Ug 2 .

где и. - код на выходе J-ro компаратора в 1-м такте, на первые m входов блока 8 умножения Блок умножения всегда умножает

числа, считанные из блока 4 памяти

на положительные числа.

2.Умножение блоком 8 умножения числа Ц (Гр), находящегося на выходе блока 4 памяти, на число Uj. В результате на выходе блока умножения 8 образуется число

(

где 1 - номер такта.

3.Суммирование сумматором 2 поступивших на его входы чисел (yig и Sj, , где - число, установленное в выходном регистре 3 в предыдущем такте.

4.Запись числа Sg oij+Sg., в выходной регистр 3 синхросигналом с выхода 9.3 блока 9 синхронизации, поступающим на тактовый вход выходного регистра 3.

5.Увеличение содержимого счетчика 7 на единицу синхроимпульсом, по ступающим с четвертого выхода 9.4 блока 9 синхронизации на тактовьй вход счетчика 7.

6.Сдвиг информации в блоке 4 памяти, при котором на его выход подается следующее число tf (Г,), предьщущее число tfdj) подается на вход блока 4 памяти. Все эти действия выполняются синхросигналом, .поступающим с четвертого выхода 9.4 блока синхронизации на тактовый вход блока 4 памяти.

7.Действия 1-6 повторяются для всех М чисел в блоке 4 памяти.

По окончании М тактов счетчик 7 находится в исходном состоянии О, числа ц (г) в блоке 4 памяти также находятся в исходном состоянии.

В выходном регистре 3 сформировано число

20 s ,-/ cr(rg)-Ug+s,

r ccF(rj)-uj.2-4s,(fe

eF с j, g,,

12)

Ug-2- +8,.

Поскольку и. при фиксированном j может принять значение 1 rte более, чем для одного значения 1 (каждое число (| (Г(р .) в цикле поступает на выход блока 4 памяти только один раз), то

(),. (13)

Учитывая (6), получим

--fil.,,;)+Ъ, ( Л4-,))( Х5;- 5;)- + + (а„+а,,+Ъ,)-2- .

Вследствие того, что

A,pX ; Ai-j x., ; 7,. У«., ( 5)

,x.,+a,xU+b у., +Ъ,уУ«

1 - л I(14)

«2 i--o

. х., +а2Х,., +

50

.-У +(а„+а,, 2

IZ , х И агХх-г+Ъ,у,, +

55

- -(а„ х° +а, х°., °..,+Ъ, у°., +

I.,-,..,..

)+ (. х ,.,+а,х.,+Ъ, V,.,,-b

5 1

71354393

ных m-разрядных регистров сдвига, b,yi,) , . , +

вторую группу последовательно вкл ченных т-разрядных регистров сдви последовательно соединенные сумма и выходной регистр, блок памяти, блок множения m блоков преобразо ния кода, m компараторов и блок с хронизации, причем вход ьшадших (п-1) разрядов первого регистра сдвига первой группы является вхо дом младших разрядов цифрового фи тра, выход выходного регистра явл ется выходом цифрового фильтра и соединен с первым входом сумматор а старшие (m-l) разрядов, кроме з кового разряда, выхода выходного гистра соединены с входом младших (m-l) разрядов первого регистра с га второй группы, выход i-ro разр да J-го регистра сдвига первой и второй групп, где ,т; ,п, п количество регистров сдвига в пер и второй группах, соединен с j-M 25 входом i-го блока преобразования да, р-разрядный выход которого со динен с первым р-разрядным входом i-ro компаратора, вторые р-разряд ные входы всех компараторов пораз но объединены и соединены с р-раз ным выходом счетчика, а выход s-r компаратора, где ,m, подключен к s-му входу блока умножения,(т+1 вход которого, где ,g; соедине с 1-ми входом и выходом блока пам

-f:x.-. 2-T-a4-,-b ::xu-2-.

j-o 1

-b,-y:.,Cyi..,-y:.,.|::.-2

;-1).. 1

а,,х,.,,.+Ъ,у,.,+Ъ,у,.,,.

Отсюда видно, что в выходном регистре 3 формируется отсчет выходной последовательности

y,s

м

(17)

Далее следует подготовительный такт, во время которого выполняются следующие действия.

1. Запись чисел х, х,,,, у., соответственно в регистры 1.2, 1.3, 1.5 сдвига из регистров 1.1, 1.2, 1.4 сдвига соответственно по синхросигналу, поступающему с первого выхода 9.1 блока синхронизации на тактовые входы регистров.

2. Запись числа

П1.1

v,

Х- -2 (чч

,-3

г-°

где - разряды следующего отсчет входной последовательност представленного в дополнительном коде

jn- ; V- -v° .

+ l 4 (

г

в первый регистр 1.1 сдвига синхросигналом, поступающим с первого выхода 9.1 блока 9 синхронизации на тактовый вход первого регистра 1.1 сдвига.

3. Запись числа

m-i

J - к

2

-1

де- у

тг 5 V

К jro

- разряды вычисленного отсчета выходной последовательности

V лг + It к

m-l

Y-v -- fo-J

i

Далее начинается выполнение следующего цикла.

Формула изобретения

Цифровой фильтр, содержащий пер- вую группу последовательно соединен-

ных m-разрядных регистров сдвига,

0

5

вторую группу последовательно включенных т-разрядных регистров сдвига, последовательно соединенные сумматор и выходной регистр, блок памяти, блок множения m блоков преобразования кода, m компараторов и блок синхронизации, причем вход ьшадших (п-1) разрядов первого регистра сдвига первой группы является входом младших разрядов цифрового фильтра, выход выходного регистра является выходом цифрового фильтра и соединен с первым входом сумматора, а старшие (m-l) разрядов, кроме знакового разряда, выхода выходного регистра соединены с входом младших (m-l) разрядов первого регистра сдвига второй группы, выход i-ro разряда J-го регистра сдвига первой и второй групп, где ,т; ,п, п- количество регистров сдвига в первой и второй группах, соединен с j-M 25 входом i-го блока преобразования кода, р-разрядный выход которого соединен с первым р-разрядным входом i-ro компаратора, вторые р-разрядные входы всех компараторов поразрядно объединены и соединены с р-разряд- ным выходом счетчика, а выход s-ro компаратора, где ,m, подключен к s-му входу блока умножения,(т+1)-и вход которого, где ,g; соединен с 1-ми входом и выходом блока памя-

0

0

35

ти, вход блока синхронизации явля0

5

ется входом запуска цифрового фильтра, а первый, второй, третий и четвертый выходы блока синхронизации соединены соответственно с объединенными тактовыми входами регистров сдвига первой и второй групп, с входом установки и тактовым входом выходного регистра и с объединенными тактовыми входами счетчика и блока памяти, отличающийся тем, что, с целью увеличения быстродействия, выход первого компаратора соединен с первым входом умножителя, выход которого подключен к второму входу сумматора, выход знакового разряда выходного регистра соединен с входом старшего разряда первого регистра сдвига второй группы через первый инвертор, а вход старшего раз- 5 ряда первого регистра сдвига первой группы соединен через второй инвертор со знаковым разрядом входа цифро- вого фильтра.

0

1354393

10

Таблица 1

011ао+а,,+Ъ

100а,,+а,,-Ъ 101а +а, ,+bj 110а +а +а +Ъ,-bj 111а +а,+а,+Ъ,+Ъ2

Таблица 2

00 О О-(,+Ъг)

000 I-(4а„+Ъ,-Ъ)

О ., О 1 О-(,+bJ

0011(,-bJ 010 О-(2а„+Ь,+Ь2) 0101-(,-bj 011 О-(2а„-Ь,+Ь) 0111(2а,-Ь.-bj 1 О О О-( Ь,+Ь) 1 О О 1-( Ь,-bj

1 О 1 О-( -ь,+ь;)

101 1-( -b,-bj

1 1. О , О(,+bJ

110 1-(2а„+Ь,-Ь)

1 i 10(,+bJ

111 1-(,-bJ

000 О 2а„-Ь,-Ь 00 О 1 2а„-Ь,+Ь 0 0. 1 О-2а„+Ь,-Ь

13

о

.1 1 I

О .0

о о 1 1 1 1

00О О-( +Ъ, +bj)

00О 1-( +Ъ,-bj

О 01 О-( ,,)

0011-( -Ъ,-Ъ,)

0100-(-2а„+Ъ,+ъ.,)

0101-(-2а„+Ъ,-Ъ О 1 .1 О-(,+bJ 0111(2а„-Ъ,-Ъ 10 00-(4ао+Ъ,+bj 100 , 1-(4а„+Ъ,--Ъ 01 О(4а,-Ъ,)

1354393lA

Продолжение табл.2

1

о 1

о 1

о I

о 1

о 1

о 1

-2а„+Ъ, -М),, -Ъ,-Ъ, -Ъ, +Ъ,

ъ,-ъ.

ъ,+ъ,

2а..,-Ъ,-Ъ;

2а„-Ъ,+Ъ

2ао+Ъ,-Ъ 2а,+Ъ,+Ъ, 4а„-Ъ,Ъ, 4а„-Ъ, +Ъг

4а,+Ь,-Ъ,

4а„+Ъ,+Ъз

Таблица 3

5

1 1 1 1 1

О О О

о о о о о 1 I 1 1 I 1 1 1

О00 00 -(2ао+Ъ,+Ъ)

00 О 0. 1 -(2а„-Ъ;-Ъ

1354393

16 Продолжение табл.3

1 1-(4а,-Ъ,-Ъ)

00-(2а„+Ъ,+Ъ,)

О 1-(2ао+Ъ,-Ъ,)

1 О-(2а„-Ъ,+Ъ,)

1.1-(2ав-Ъ,-Ъг)

002а„-Ъ,-Ъ

О 12а„-Ъ, +Ъ

1 ,-Ъ

1 12ао+Ъ, +bj

О О4а„-Ъ,-Ъ, О , ФЪ

104а„+Ъ,-Ъ

1 14а„+Ъ +Ъ2

00-2а„-Ъ,-Ъ

01-2а„-Ъ,+Ь.г 10-2а„+Ъ,-Ъ

О11 ,+Ъ,1

1О О-Ъ,-

101-Ь +Ъ,,

11 О+Ъ,-Ь

111+Ь,+b,j.

:Таблица 4

17

135439318

Продолжение табл.4

I О 1 2ао-Ъ, +Ъ

11 О2а„+Ъ,-Ъ

11 2а„+Ъ,+Ъ

О000-(2ао+а,+Ъ,+Ъ)

О001-(2ao+a,+b,-bJ

О010-(2ag+a,-b,+bJ

0011(2а„+а,-Ъ,-Ъ

О1 О О-( а,+Ъ,+Ъ)

I

О1 о 1-( а,+Ъ,-bj

0II О-( а,-b.+bj)

О111-( а,-Ь,-bj

1О О О-(2ао-а,+b,+b)

1001-(2a,-a,+b,-bJ

1010-(2а„-а,-Ь,+Ь)

1011-(,-b,-bJ

11 О О-( -а,+Ь,+Ь.,)

I1 О 1-( -a,+b,-b,)

111 О-( -а,-Ь,+Ь)

Г111-( -a,-b,-bj 0 О О О-а, -Ь, -Ь 0001-a,-b,+bj 0010-а,+Ъ, -Ъ

00.11-а,+Ь,+Ьг

Таблица 5

21

1354393

22 Продолжение табл.5

Таблица 7

0 000 0 001

о о I о

0011 0 100 0 101 0 110

0111

1000 1 00.1 1 010 1011

-{2а„+а,+Ь,

.(,+b,-bJО1

.(2а„+а,-Ъ,+Ъ,)О1

-(2а,+а,-Ъ,

-( +а,+Ъ,

.( +а,+Ъ,-Ъ)1О

.( +а,-Ъ,+bj1О

.( +a,-b,-bj1О

-(2а„-а,+b,+bj1О

-(2ao-a,+b,-bJ1О

-(2а„-а,-Ъ,+Ъ,)1О

.(2а„-а,-Ъ,-Ъ)1О

00oo oooooinoooooioo

0001000011000100101

0010000101001000110

0011000111001100111

0100001001010001000 0101001011010101001 0110001101011001010 0111001111011101011 1000010001100001100 100101001 1 100101 101

Таблица 10

1 О О 2а,-а,-Ъ,-Ъ,

1 О 1 ,-Ъ,+Ъ

1 О2а„-а,+Ъ,-Ъ

I12а„-а,+Ъ,+Ъ ОПа,-Ъ,-Ъ О 1а,-Ъ,+bj 1 Оа,+Ъ,-Ь

IIа,+Ъ,+Ъ

О О2а„+а,-Ъ,-Ъ О 12ао+а -Ъ,+Ъ 1 О2а,+а,+Ъ,-Ъ, 1 12ао+а,+Ъ,+Ъ

Таблица 11

ГАдрес Г Адрес Г

Лг у. (f.S5 . Л. If. i У Ь fs .10 100101011010.01110

101101.Oil IIOI-IO Ill

1100011001110000000 il01011011110100001 il1001 101 1000010. il 1 0 1 1 1 I 1 1 1 1 1 1 0 0 1 1

Таблица 12 Дррес Г.Адрес Г

Л, Л Л, , , 1г. Ь Ь . У; Ь J

000 000000100000100 OOO OlOOOilOOOlOlOl

000lOOOlOtOOlOOllO 1100.1 1100 1011 1 O OI 000100101001000

001010101101011001

,b

0011001 10101 bOlOlO

001IIOIIIIOIIIIOII

010000000110000100

0100100011100,101 0 l 0101000101 101001 10

010110011110110111

011000100111001000 oil010101 11 101 1001 oil100110111101010 oil110111111111011

31

0000000 1 00001 00 000100110001101 001001010010110 001101110011111 010000010100100 01010011010110 011001010110110 011101110111111 10 00000 11 000 100 100100111001101

101001011010110

i о 1 1 о 1 1 1 1 о 1 1 1 1 1

11000001 1 100100 110100111101101 111001011110110 1111011111-11111

о000000 000 1000000 100

о000100001 1000100101

о0010000101001000110

о0011000111001100111

о0100001001010001100

о0101001011010101101

135439332

Таблица 13

Таблица 14

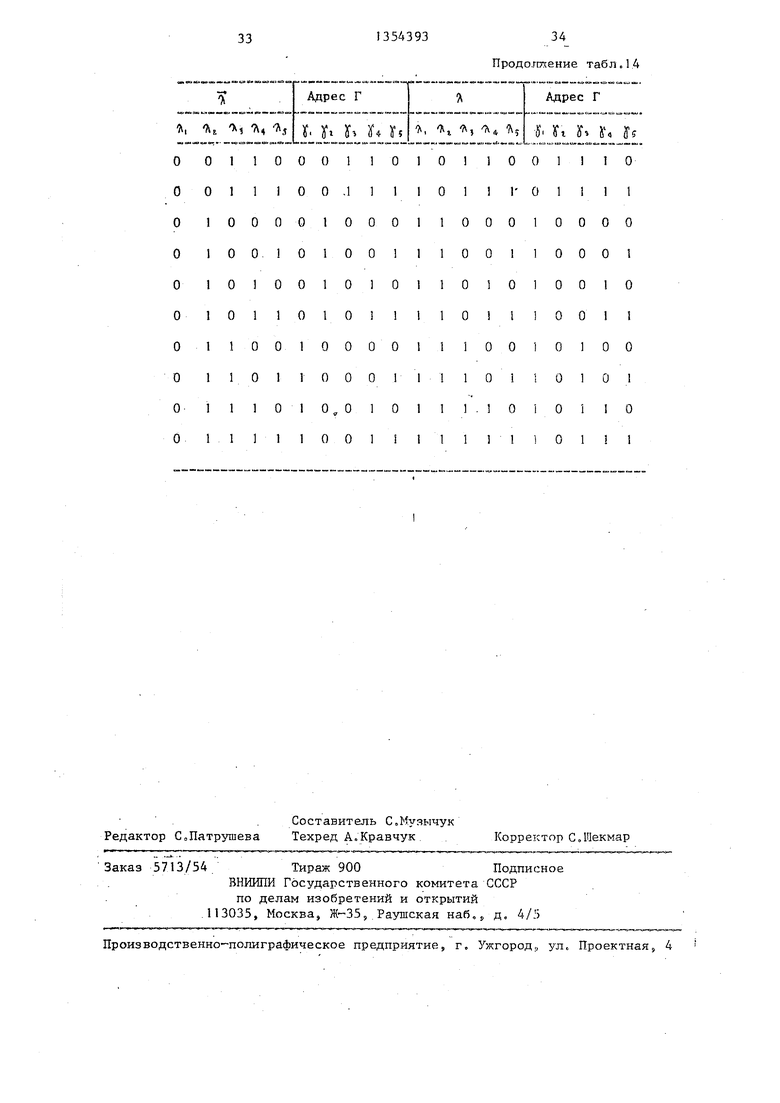

33

OllOOOllOlOllOOlllO О 1 1 I О О Л 1 1 1 О 1 1 1- О 1 1 1 1000010001100010000 100. 1010011100110001

1010010101101010010 101 1010 11 10 110011

11 001 0000 1 1 1 00 ) о 1 00

1 1 о 1 1 о о о г 1 1 1 о 1 1 о 1 о 1 i 11010,01011 i.ioioi 10

il 11 1001 ill 111 101 11

Редактор СоПатрушева

Составитель С.Музычук Техред А.Кравчук

Заказ 5713/54Тираж 900Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий .113035, Москва, Раушская наб,5. Д 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

1354393

34 Продотгаение табл. 1 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридный функциональный преобразователь | 1987 |

|

SU1464180A1 |

| Цифровой фильтр | 1987 |

|

SU1453592A1 |

| Устройство для формирования сигналов передачи данных | 1980 |

|

SU1019659A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

| Программно-управляемый цифровой фильтр | 1979 |

|

SU877787A1 |

| Устройство следящего аналого-цифрового преобразователя | 1987 |

|

SU1522405A1 |

| Цифровой фильтр | 1984 |

|

SU1243088A1 |

| Многоканальный релейный коррелометр | 1982 |

|

SU1062718A1 |

| Устройство для цифрового формирования сигналов с амплитудно-фазовой модуляцией и одной боковой полосой | 1988 |

|

SU1598200A1 |

| Способ цифрового управления непосредственным преобразователем частоты | 1985 |

|

SU1350787A1 |

Изобретение может использовать-i ся в радиосвязи, радиолокации для цифровой обработки сигналов и обеспечивает повышение быстродействия цифрового фильтра. Цифровой рекурсивный фильтр второго порядка содержит регистры сдвига (РС) 1.1-1-,3 « цервой группы, PC 1.4, .1,5 второй группы, сумматор 2, выходной регистр . т а 00 ел 4 ОО О СО 2,1-:- д,дГзалуск

| Цифровой фильтр | 1984 |

|

SU1243088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| бхоЭ , | |||

| ,.,.,. | |||

Авторы

Даты

1987-11-23—Публикация

1986-02-07—Подача