1

Изобретение относится к автомати Кб, вычислительной технике и может быть использовано в системах автоматического управления и контроля, в микропроцессорных системах, а част- ности в цифровых линеаризующих устройствах, а устройствах аппаратной реализации средств математического обеспечения ЭВМ.

Цель изобретения - повышение точ ности вычислений логарифмической функции.

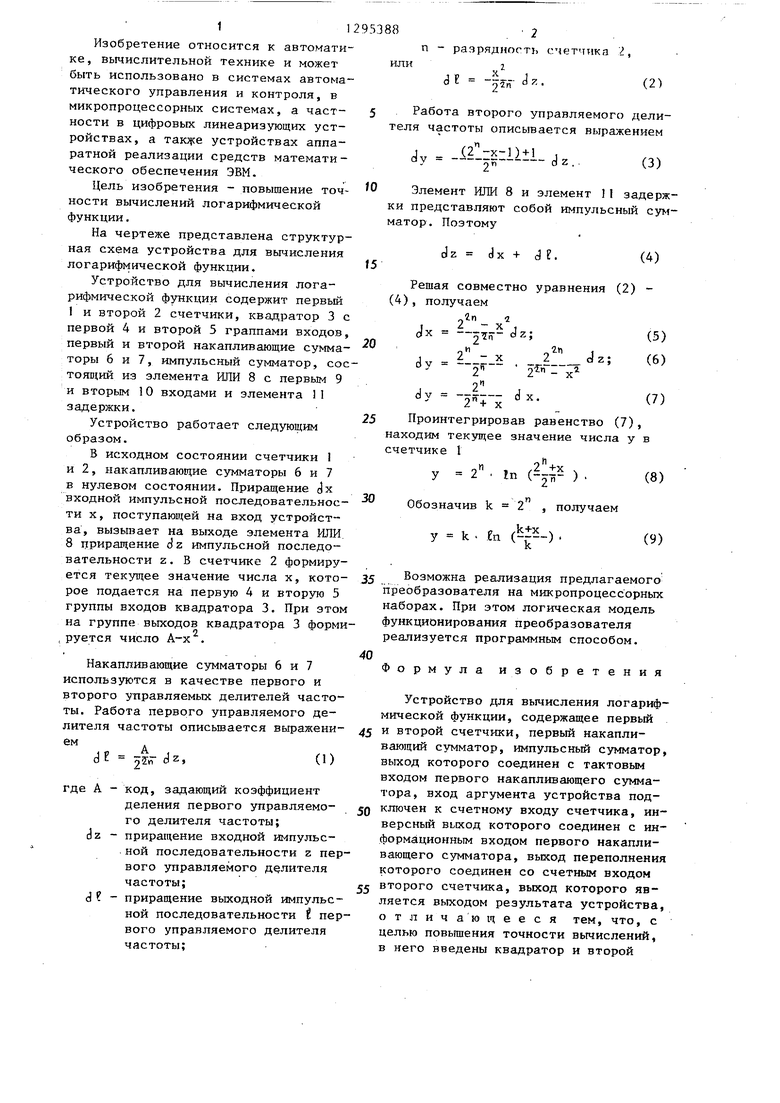

На чертеже представлена структурная схема устройства для вычисления логарифмической функции.

Устройство для вычисления логарифмической функции содержит первьш I и второй 2 счетчики, квадратор 3 первой 4 и второй 5 граппами входов первый и второй накапливающие сумматоры 6 и 7, импульсный сумматор, со тояв1ий из элемента ИЛИ 8 с первым 9 и вторым 10 входами и элемента 1 задержки.

Устройство работает следующим образом.

В исходном состоянии счетчики 1 и 2, накапливающие сумматоры 6 и 7 в нулевом состоянии. Приращение jx входной импульсной последовательности X, поступающей на вход устройства, вызывает на выходе элемента ИЛИ 8 приращение d z импульсной последовательности Z. В счетчике 2 формируется текущее значение числа х, кото рое подается на первую 4 и вторую 5 группы входов квадратора 3. При это на группе выходов квадратора 3 форм

группе выходов ,руется число А-х

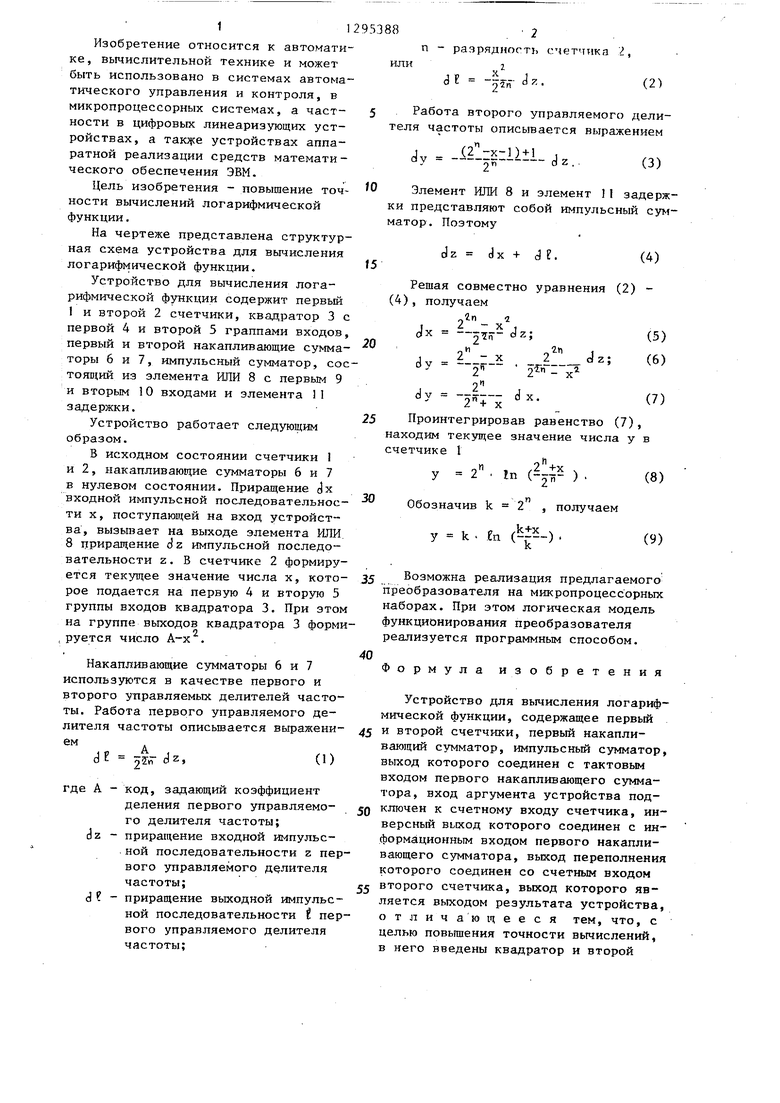

Накапливающие сумматоры 6 и 7 используются в качестве первого и второго управляемых делителей частоты. Работа первого управляемого делителя частоты описьшается выражением

dE jtn- dz,(1)

где А - код, задающий коэффициент

деления первого управляемого делителя частоты;

dz - приращение входной импульсной последовательности z первого управляемого делителя частоты;

d - приращение выходной импульсной последовательности t первого управляемого делителя частоты;

разрядность d Р -|гуг-

счет ттжа 2,

(2)

п или

Работа второго управляемого делителя частоты описывается выражением

I () + 1 J dv ----гг-dz..

2

(3)

5

у k 5

Элемент ИЛИ 8 и элемент 11 задержки представляют собой импульсный сумматор. Поэтому

dz tJx + d е.

Решая совместно уравнения (4), получаем

1

0

5

Jx

dy

dy

iz;

2- Л

2 (4) (2) (5) (6)

d

21 X

Проинтегрировав равенство (7), находим текзщее значение числа у в счетчике 1

п

(7)

У 2

In

h ,

f--- -} 2

(8)

у k

Обозначив k

получаем

eu (i.)

(9)

у k

Возможна реализация предлагаемого преобразователя на микропроцессорных наборах. При этом логическая модель функционирования преобразователя реализуется программным способом.

Формула изобретения

Устройство для вычисления логарифмической функции, содержащее первый и второй счетчрЕки, первый накапливающий сумматор, импульсный сумматор, выход которого соединен с тактовым входом первого накапливающего сумматора, вход аргумента устройства подключен к счетному входу счетчика, ин- версньй вьгкод которого соединен с информационным входом первого накапливающего сумматора, выход переполнения которого соединен со счетным входом второго счетчика, выход которого является выходом результата устройства, отличающееся тем, что, с целью повьппения точности вычислений, в него введены квадратор и второй

3 1, 9 зла 84

накапливающий сумматор, тактовьй входвыходом квадратора, информационный в

которого соединен с выходом импульс-вход которого соединен с выходом перного сумматора, первый вход которогового счетчика вход аргумента

соединен с выходом переполнения вто-устройства соединен с вторым вхо

рого накапливающего сумматора, инфор- 5Д° импульсного суммато матдионный вход которого соединен сра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмической функции | 1985 |

|

SU1280617A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1233143A1 |

| Устройство для ивлечения корня | 1985 |

|

SU1277102A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1244663A1 |

| Устройство для вычисления экспоненциальной функции | 1985 |

|

SU1295389A1 |

| Логарифмический преобразователь | 1982 |

|

SU1037248A1 |

| Устройство для вычисления экспоненциальной функции | 1985 |

|

SU1309043A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1120322A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1203517A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1003094A1 |

Изобретение относится к авто- - матике, вычислительной технике и rR3 0rO может быть использовано в системах автоматического управления и контроля, в микропроцессорных системах, в частности в цифровых линеаризующих устройствах, а также устройствах аппаратной реализации средств математического обеспечения ЭВМ. Цель изобретения - повышение точности вычисления логарифмической функции. Устройство содержит первый счетчик 1 результата, второй счетчик 2, квадратор 3, два управляемых делитегя частоты на накапливакмдих сумматорах 6 и 7, импульсный сумматор, состоящий из элемента ИЛИ 8 и элемента 11 задержки. 1 ил.Q (Л тк

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Число-импульсное устройство для воспроизведения логарифмических функций | 1983 |

|

SU1144106A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-09—Подача