Изобретение относится к вычисли- тельной технике и может быть исполь зовано в арифметических устройствах электронных цифровых вычислительных машин и в цифровых измерительных приборах.

Цель изобретения - упрощение устройства.

5 на вход переноса сумматора 1, на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и на второй вход элемента ИСКЛЮЧАКЬ ЩЕЕ ИЛИ 12. Присутствие логического О не только на первом, но и на ром входе элемента ИСКЛЮЧАЩЕЕ ИЛИ 10 вызывает появление логического О на выходе этого элемента. При поступлении логического О на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 потенциал на выходе 16 знака Зн. С результата устройства повторяет потенциал на шине 15 знакового разряда Зн. В второго операнда.

Логический О с выхода элемента

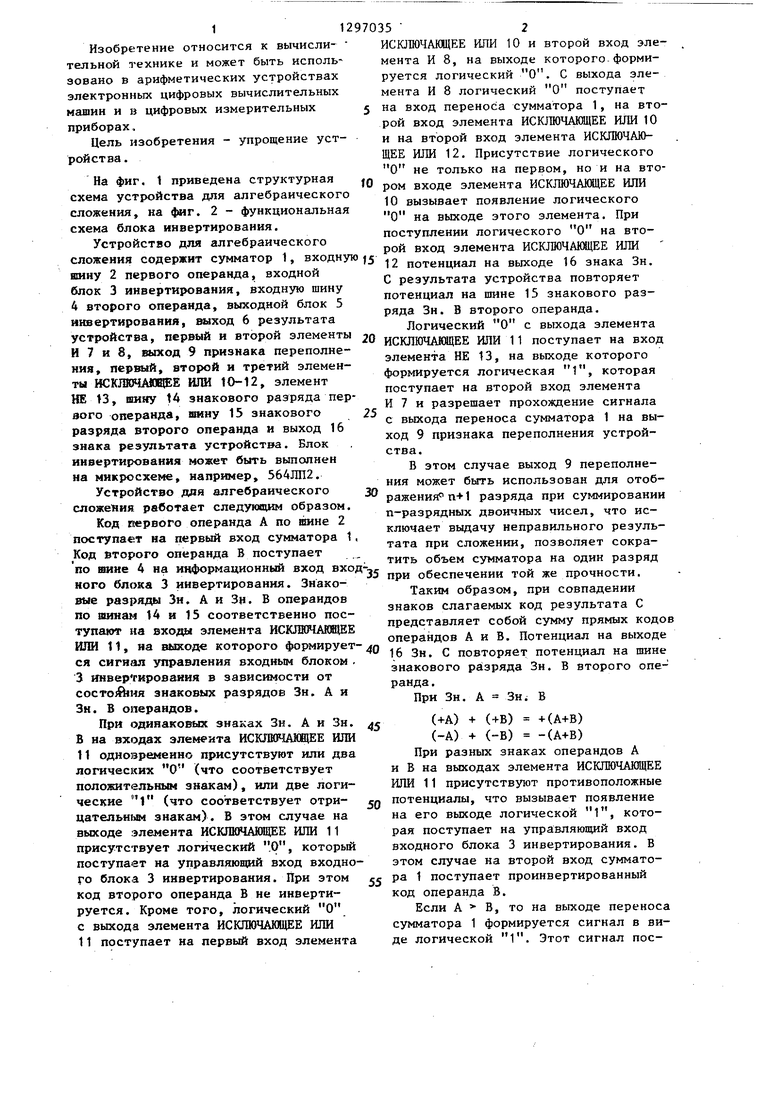

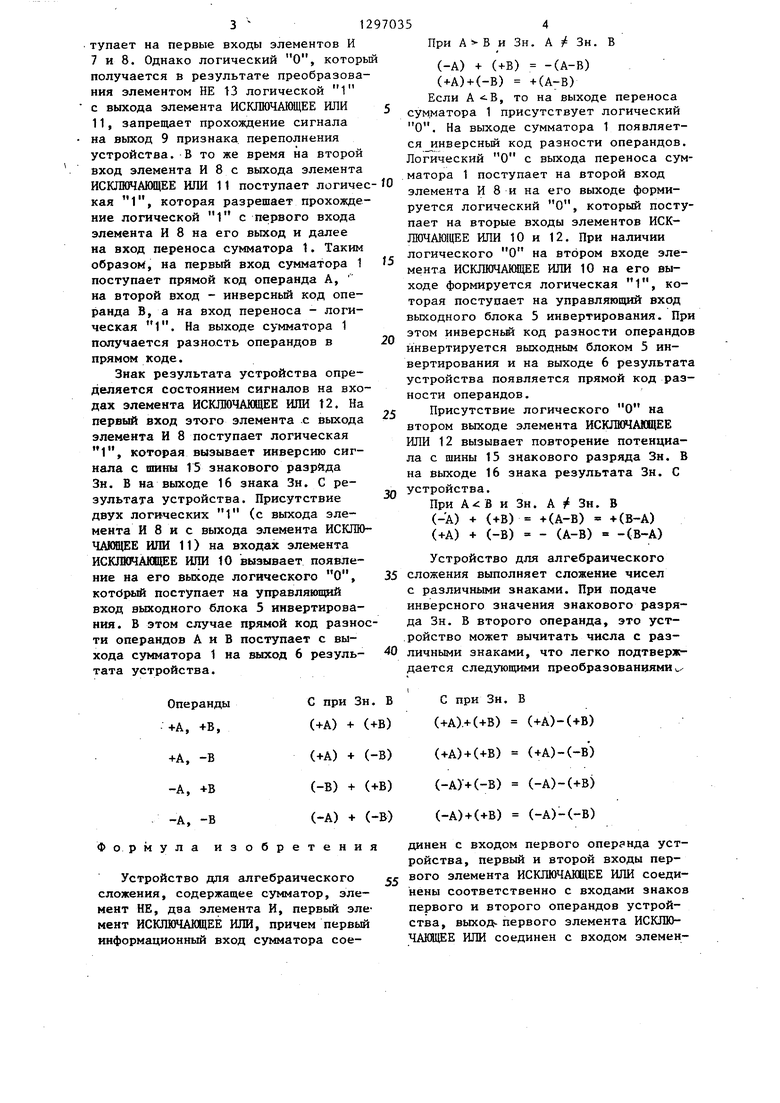

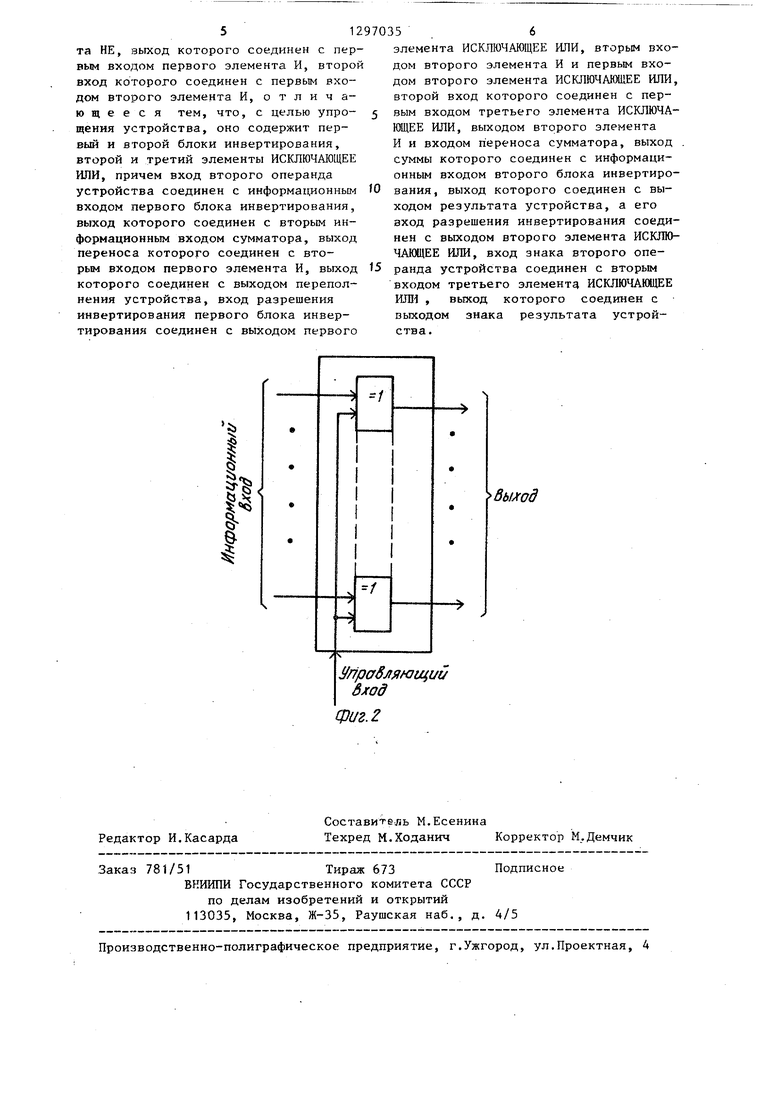

На фиг. 1 приведена структурная схема устройства для алгебраического сложения, на 4«г. 2 - функциональная схема блока инвертирования.

Устройство для алгебраического сложения содержит сумматор 1, входную 15 шину 2 первого операнда, входной блок 3 инвертирования, входную шину 4 второго операнда, выходной блок 5 инвертирования, 6 результата

устройства, первый и второй элементы 0 ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступает на вход И 7 и 8, выход 9 признака переполне25

элемента НЕ 13, на выходе которого формируется логическая 1, которая поступает на второй вход элемента И 7 и разрешает проховдение сигнала с выхода переноса сумматора 1 на выход 9 признака переполнения устройства.

В этом случае выход 9 переполнения может быть использован для отоб- ражения разряда при суммировании п-разрядных двоичных чисел, что исключает выдачу неправильного результата при сложении, позволяет сокра , . . тить объем сумматора на один разряд

по вшне 4 на информационный вход вход-,с - i- г., -г, при обеспечении той же прочности.

«t4 jr%V4mi I4 bX4«n гъ т«гг Лж

КИЯ, первый, второй и третий элементы ИСКЛЮЧАЯЩЕ ИЛИ 10-12, элемент НЕ 13, шину Ц знакового разряда пер аого операнда, шину 15 знакового разряда второго операнда и выход 16 знака результата устройства. Блок инвертирования может быть выполнен на микросхеме, например, 564ЛП2.

Устройство дяя алгебраического сложеТ1ия работает следующим образом.

Код iwpBoro операнда А по шине 2 поступает на первый вход сумматора 1 Код второго операнда В поступает

ноге блока 3 инвертирования. Знаковые разряды Зн. А и Зн. 6 операндов по шинам 14 и 15 соответственно поступают на входы элемента ИСКЛШАЮЩЕЕ ИЛИ 11, на выходе которого формирует- Q ся сигнал управления входным блоком . 3 инвертирования в зависимости от состо}Й1Ия знаковых разрядов Зн. А и Зн. В операндов.

При одинаковых знаках Зн. А и Зн. В на входах элемента ИСКЛЮЧАЩЕЕ ШШ 11 одновременно присутствуют или два логических О (что соответствует положительным знакам), или две логи45

ческие 1 (что соответствует отри- цательн1Л4 знакам). В этом случае на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ 11 присутствует логический О, который поступает на управляющий вход входного блока 3 инвертирования. При этом код второго операнда В не инвертируется. Кроме того, логический О с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступает на первый вход элемента

50

55

Таким образом, при совпадении знаков слагаемых код результата С представляет собой сумму прямых кодов операндов А и Б. Потенциал на выходе 16 Зн. С повторяет потенциал на шине знакового разряда Зн. В второго операнда .

При Зн. А Зн; В

(+А) + (+В) (А+В) (-А) (-В) -(А+В)

При разных знаках операндов А и В на выходах элемента ИСКЛЮЧАЮЩЕЕ ШШ 11 присутствуют противоположные потенциалы, что вызывает появление на его выходе логической 1, которая поступает на управляющий вход входного блока 3 инвертирования. В этом случае на второй вход сумматора 1 поступает проинвертированный код операнда В.

Если А В, то на выходе переноса сумматора 1 формируется сигнал в виде логической 1. Этот сигнал посИСЮТЮЧАЩЕЕ ИЛИ 10 и второй вход элемента И 8, на выходе которого-формируется логический О. С выхода элемента И 8 логический О поступает

на вход переноса сумматора 1, на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и на второй вход элемента ИСКЛЮЧАКЬ ЩЕЕ ИЛИ 12. Присутствие логического О не только на первом, но и на втором входе элемента ИСКЛЮЧАЩЕЕ ИЛИ 10 вызывает появление логического О на выходе этого элемента. При поступлении логического О на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 потенциал на выходе 16 знака Зн. С результата устройства повторяет потенциал на шине 15 знакового разряда Зн. В второго операнда.

Логический О с выхода элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступает на вход

Q

5

0

5

Таким образом, при совпадении знаков слагаемых код результата С представляет собой сумму прямых кодов операндов А и Б. Потенциал на выходе 16 Зн. С повторяет потенциал на шине знакового разряда Зн. В второго операнда .

При Зн. А Зн; В

(+А) + (+В) (А+В) (-А) (-В) -(А+В)

При разных знаках операндов А и В на выходах элемента ИСКЛЮЧАЮЩЕЕ ШШ 11 присутствуют противоположные потенциалы, что вызывает появление на его выходе логической 1, которая поступает на управляющий вход входного блока 3 инвертирования. В этом случае на второй вход сумматора 1 поступает проинвертированный код операнда В.

Если А В, то на выходе переноса сумматора 1 формируется сигнал в виде логической 1. Этот сигнал поступает на первые входы элементов И 7 и 8. Однако логический О, которы получается в результате преобразования элементом НЕ 13 логической 1 с выхода элемента ИСКЛЮЧАЩЕЕ ИЛИ 11, запрещает прохождение сигнала на выход 9 признака переполнения устройства. В то же время на второй вход элемента И 8 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступает логичес кая 1, которая разрешает прохождение логической 1 с первого входа элемента И 8 на его вьпсод и далее на вход переноса сумматора 1. Таким образом, на первый вход сумматора 1 поступает прямой код операнда А, на второй вход - инверсный код операнда В, а на вход переноса - логическая 1. На выходе сумматора 1

получается разность операндов в прямом коде.

Знак результата устройства определяется состоянием сигналов на входах элемента ИСКЛЮЧАЩЕЕ ШШ t2. На первый вход этого элемента с выхода элемента И 8 поступает логическая 1, которая вызывает инверсию сигнала с шины 15 знакового разрйда Зн. В на выходе 16 знака Зн. С результата устройства. Присутствие двух логических 1 (с выхода элемента И 8 и с выхода элемента ИСКЛЮЧАЩЕЕ ИЛИ 11) на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 вызывает появление на его выходе логического О, который поступает на управляющий вход выходного блока 5 инвертирования. В этом случае прямой код разности операндов А и В поступает с выхода сумматора 1 на выход 6 результата устройства.

анды +В,

-В +В -В

С при Зн. В (+А) -1- (+В)

(+А) + (-В) (-В) + (+В) (-А) + (-В)

Формула изобретения

Устройство для алгебраического сложения, содержащее сумматор, элемент НЕ, два элемента И, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый информационный вход сумматора соеПри . . В

(-А) + (+В) -(А-В) () + (-В) -t-(A-B) Если А В, то на выходе переноса сумматора 1 присутствует логический О. На выходе сумматора 1 появляется инверсньй код разности операндов. Логический О с выхода переноса сумматора 1 поступает на второй вход элемента И 8 и на его выходе формируется логический О, который поступает на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и 12. При наличии логического О на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 на его выходе формируется логическая 1, которая поступает на управляющий вход выходного блока 5 инвертирования. При этом инверсньй код разности операндов инвертируется выходным блоком 5 инвертирования и на выходе 6 результата устройства появляется прямой код разности операндов.

Присутствие логического О на втором выходе элемента ИСКЖНМЩЕЕ ИЛИ 12 вызывает повторение потенциала с шины 15 знакового разряда Зн. В на выходе 16 знака результата Зн. С устройства.

При . . В (-А) -- +В) +(А-В) +(В-А) (+А) + (-В) - (А-В) -(В-А)

Устройство для алгебраического сложения выполняет сложение чисел с различными знаками. При подаче инверсного значения знакового разряда Зн. В второго операнда, это устройство может вычитать числа с различными знаками, что легко подтверждается следующш и преобразованиями v

1

С при Зн. В

(+А).-1-(+В) (+А)-(+В)

(fA)(+B) (+А)-(-в )

(-АУ+(-В) (-А)-(+В)

(-А)(+В) (-А)-(-В)

динен с входом первого устройства, первый и второй входы первого элемента ИСКЛЮЧАЩЕЕ ИЛИ соединены соответственно с входами знаков первого и второго операндов устройства, выход- первого элемента ИСКЛЮЧАЩЕЕ ИЛИ соединен с входом элемента НЕ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И, отличающееся тем, что, с целью упро- щения устройства, оно содержит первый и второй блоки инвертирования, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход второго операнда устройства соединен с информационным входом первого блока инвертирования, выход которого соединен с вторым информационным входом сумматора, выход переноса которого соединен с вторым входом первого элемента И, выход которого соединен с выходом переполнения устройства, вход разрешения инвертирования первого блока инвертирования соединен с выходом первого

Управляющий djcod

Фиг. 2

Редактор И.Касарда

Составитель М.Есенина

Техред М.Ходанич Корректор М.Демчик

Заказ 781/51Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторым входом второго элемента И и первым входом второго элемента ИСКЛЮЧАНЖЕЕ ИЛИ второй вход которого соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом второго элемента И и входом переноса сумматора, выход суммы которого соединен с информационным входом второго блока инвертирования, выход которого соединен с выходом результата устройства, а его вход разрешения инвертирования соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход знака второго операнда устройства соединен с вторым входом третьего элемента ИСКЛЮЧАЩЕЕ ИЛИ , выход которого соединен с выходом знака результата устройства.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического вычитания | 1985 |

|

SU1297036A1 |

| Вычислительное устройство | 1988 |

|

SU1517024A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1985 |

|

SU1259249A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1972 |

|

SU332459A1 |

| Устройство для сложения чисел в дополнительном коде | 1991 |

|

SU1784972A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Устройство для сложения в двоичной и двоично-десятичной системах счисления | 1990 |

|

SU1789980A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах электронных цифровых вычислительных i машин и в цифровых измерительных при борах. Цель изобретения - упрощение устройства. Устройство рля алгебраического сложения содержит сумматор 1, два блока 3 и 5 инвертирования, два элемента И 7 и 8, три элемента ИСК- ТЮЧАЮЩЕЕ ИЛИ 10-12, элемент НЕ 13. Преимущества устройства заключаются II более простом его построении и бо- лее простой схеме управления устройства. 2 ил. (Л В - 10 тг W Фиг.1

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-29—Подача