Изобретение относится к области вычислительной техники и может быть испольяовано для аппаратурной реализации функциональных зависимостей в специализированных и универсальных быстродействующих цифровых вычислительных машинах.

Целью изобретения является повыше .ние точности вычислений.

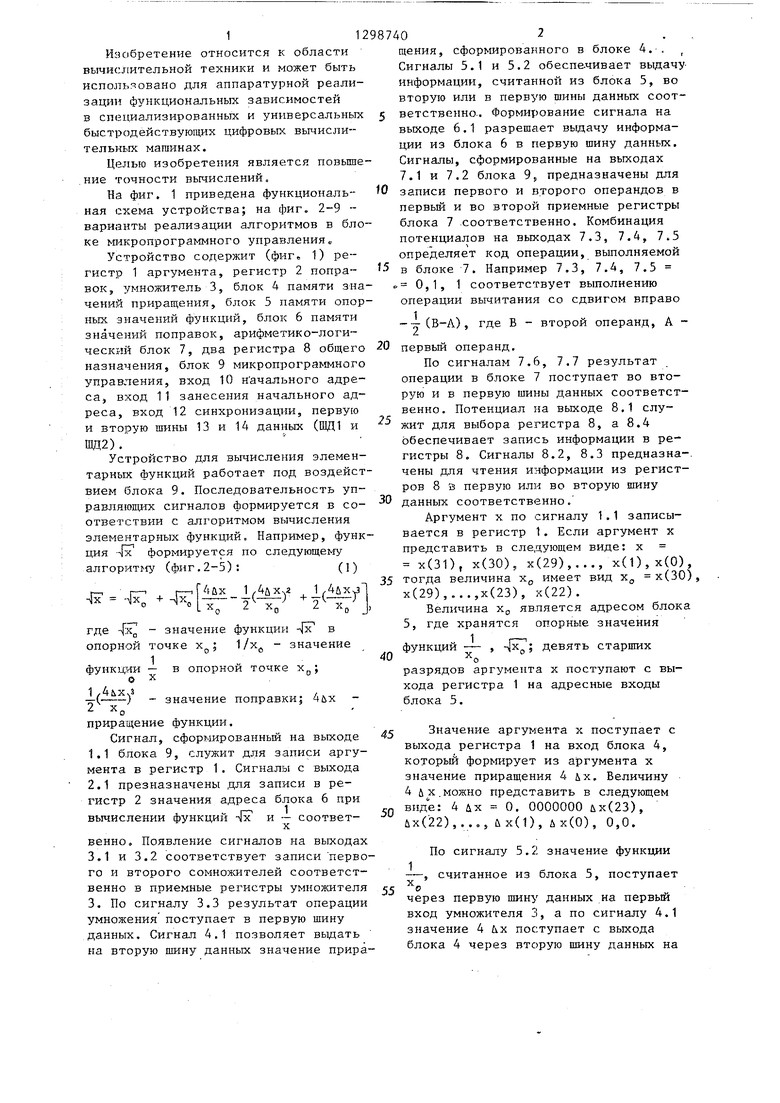

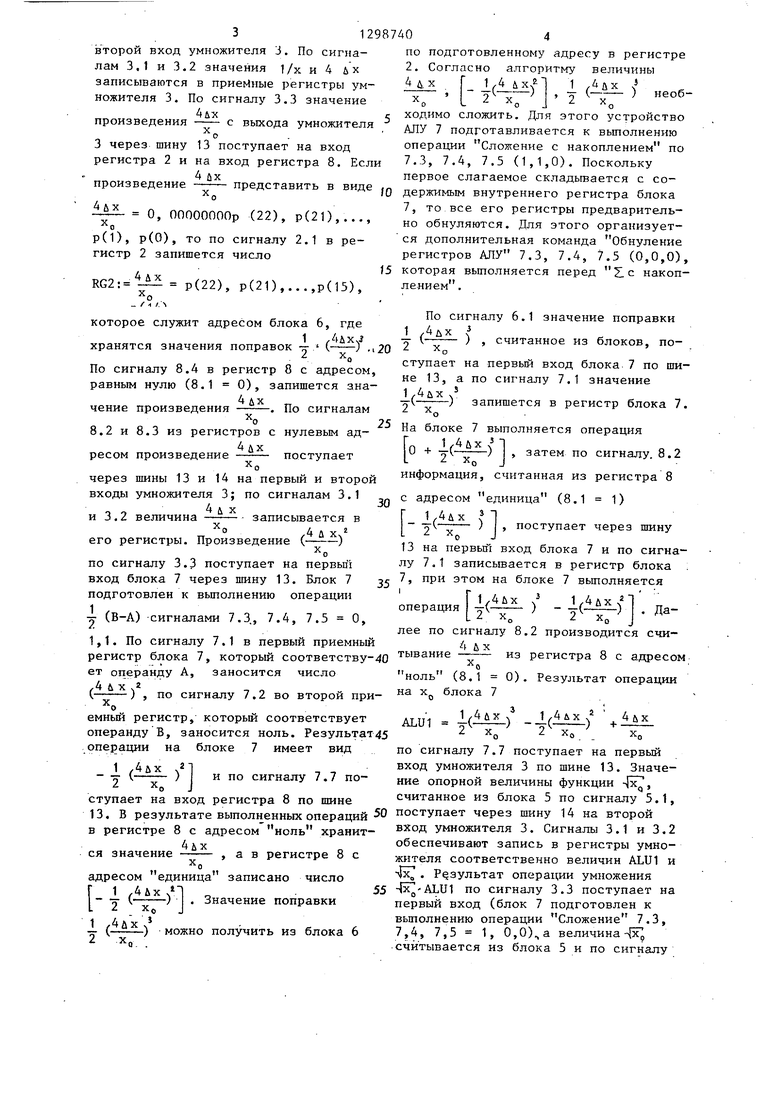

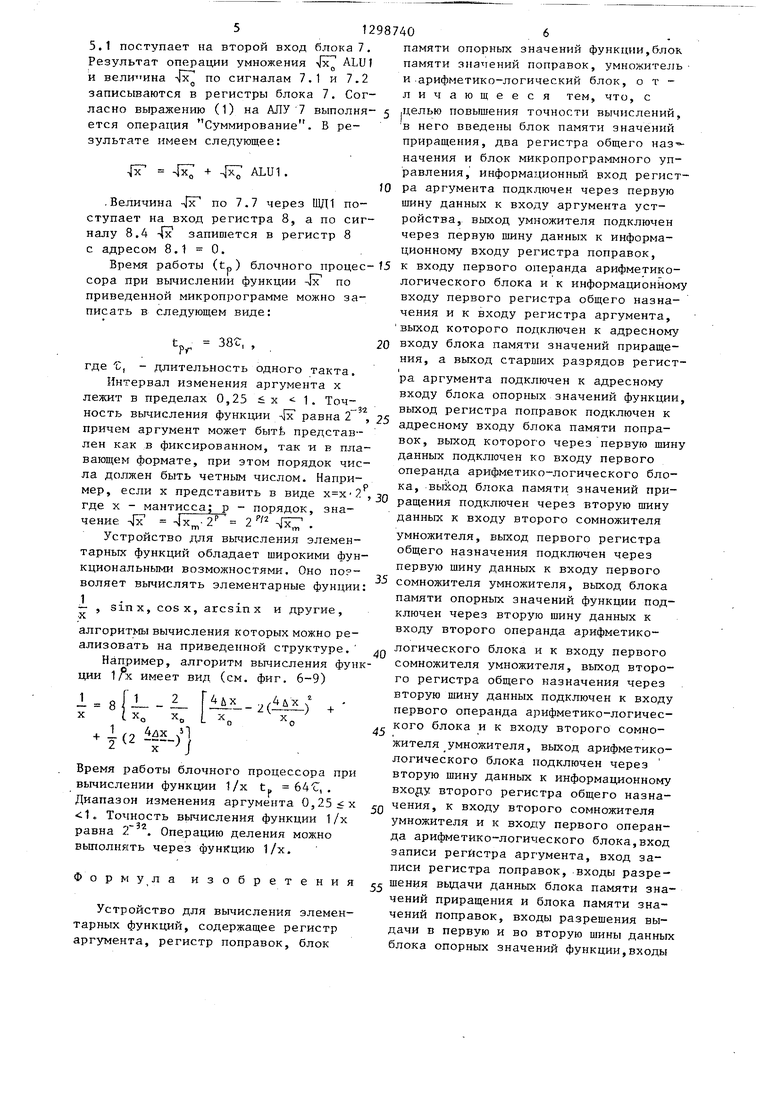

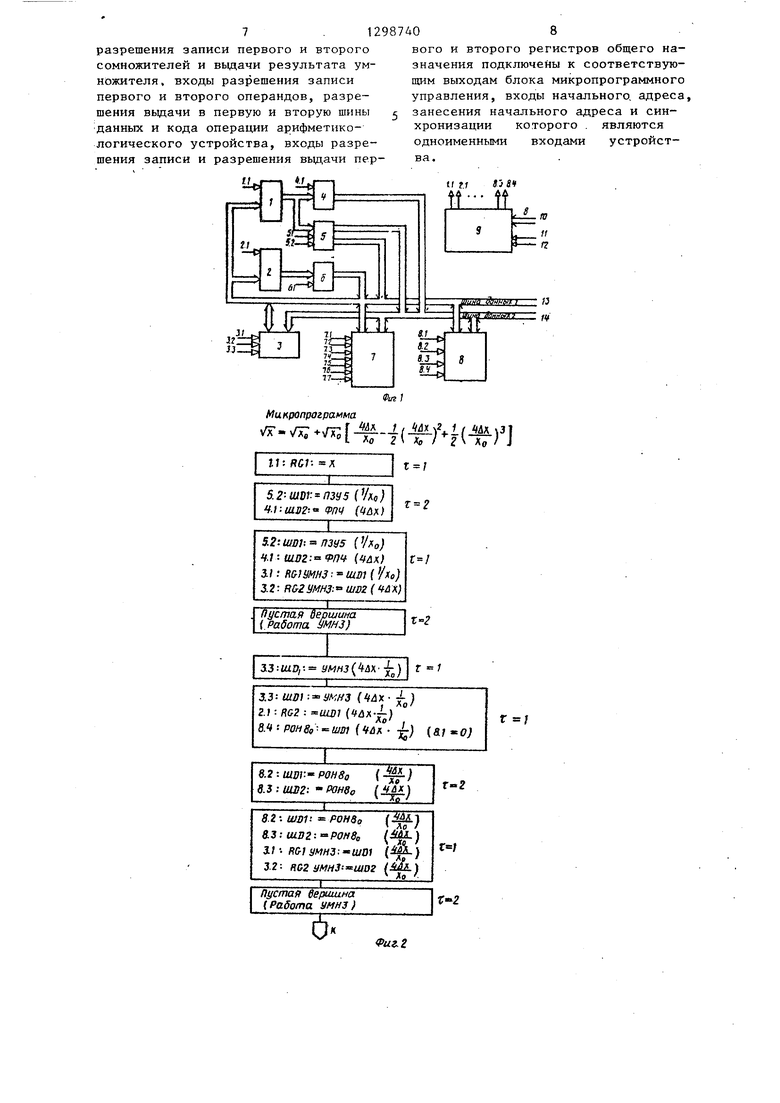

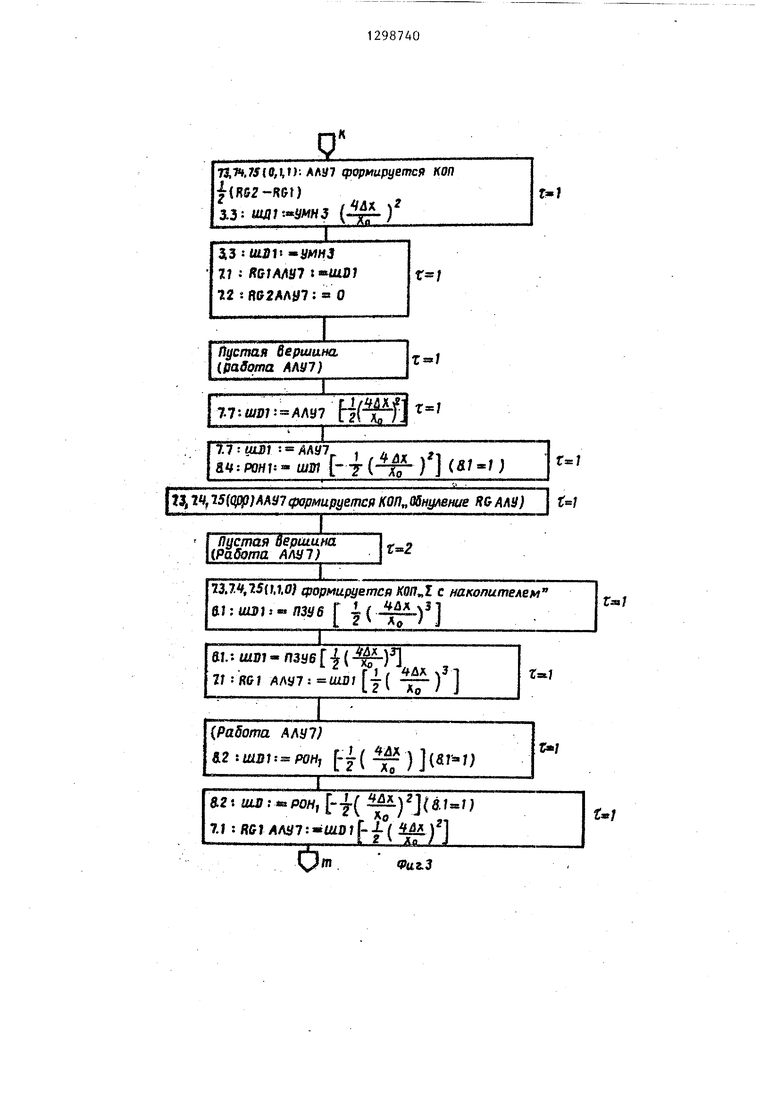

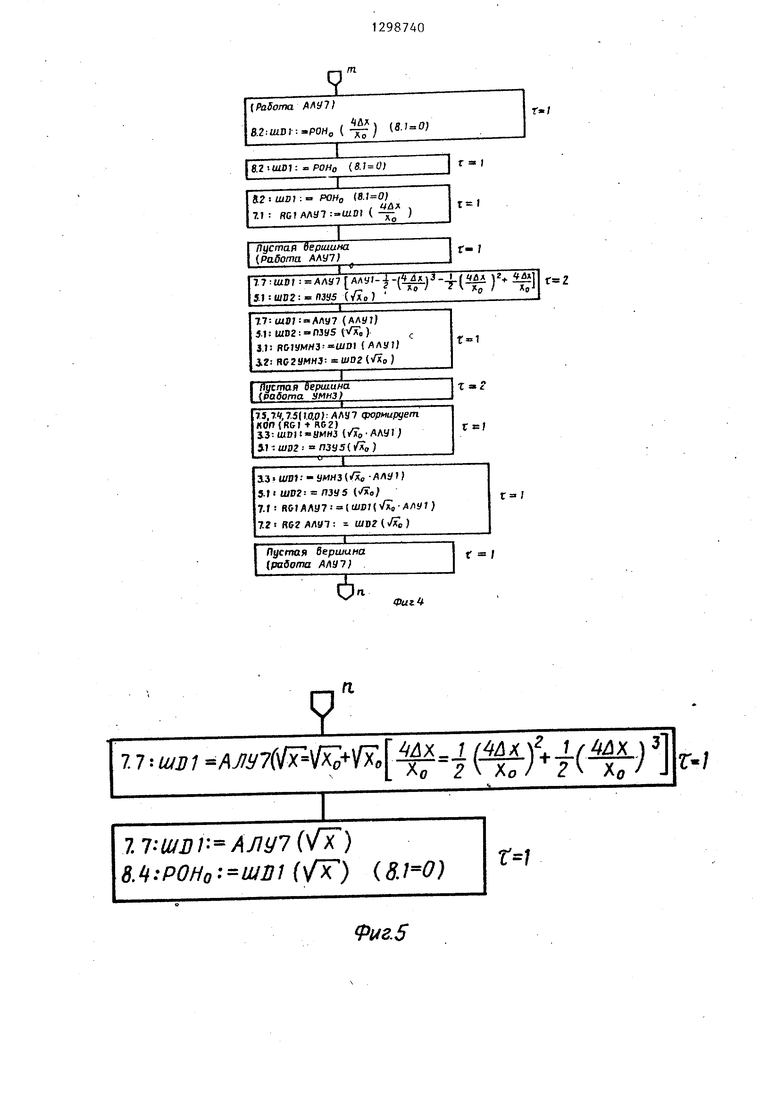

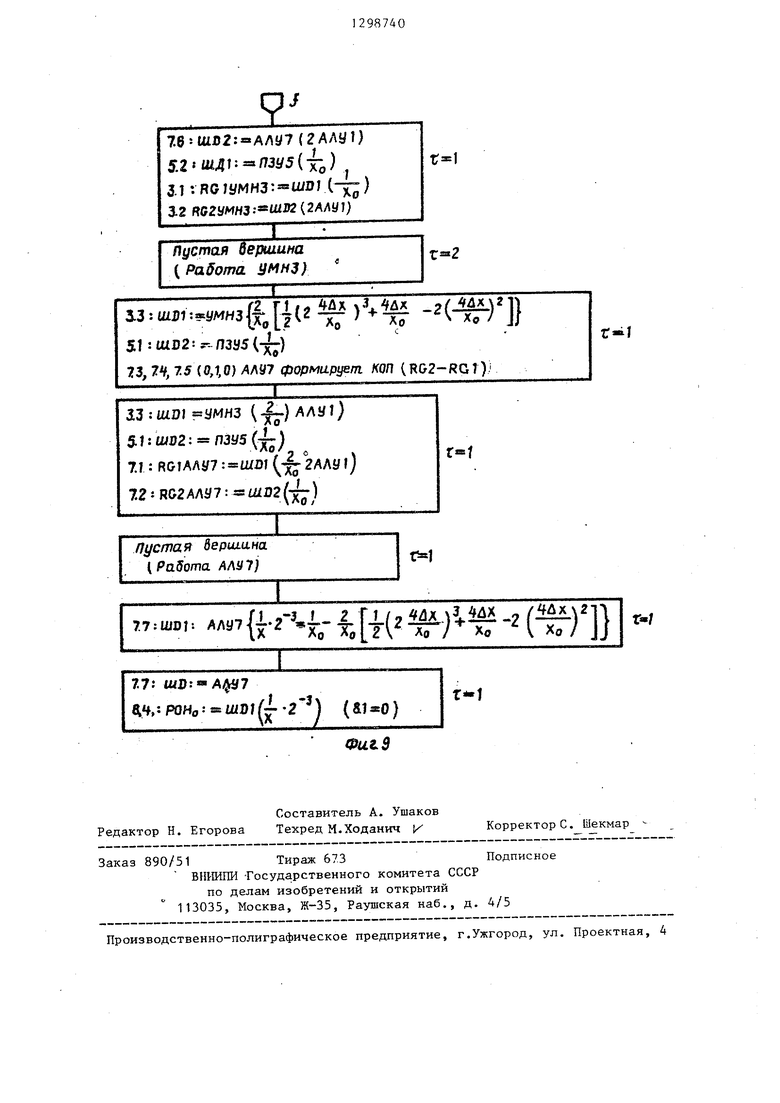

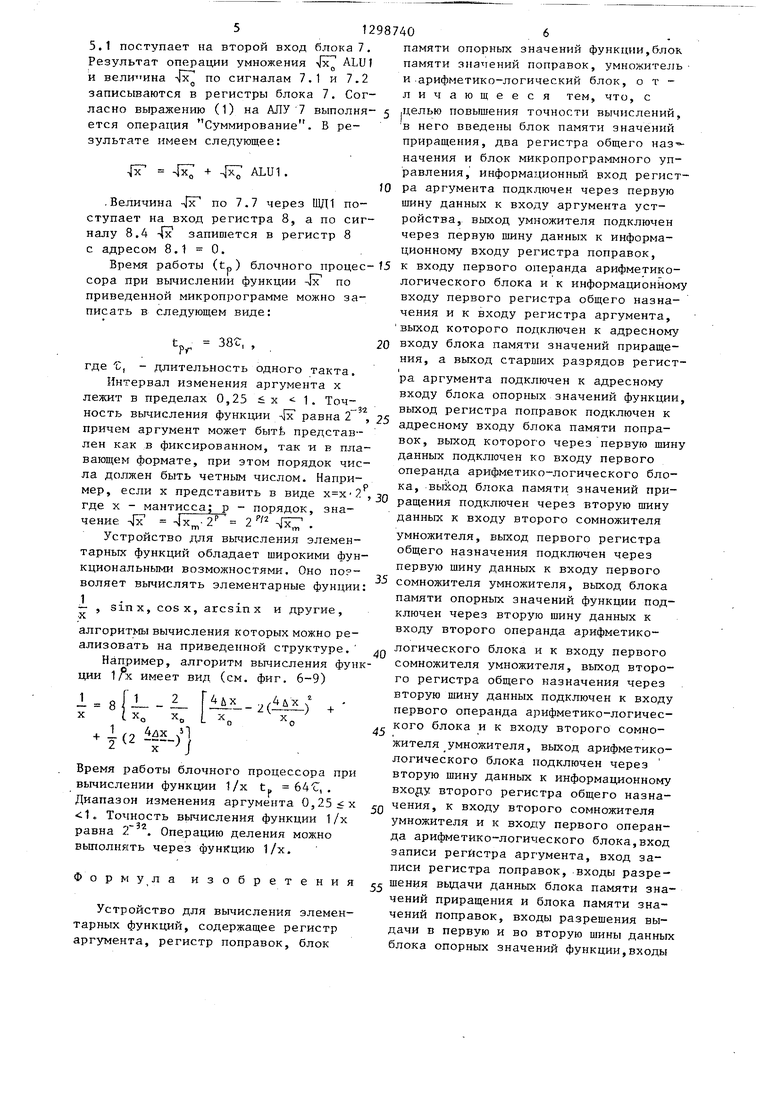

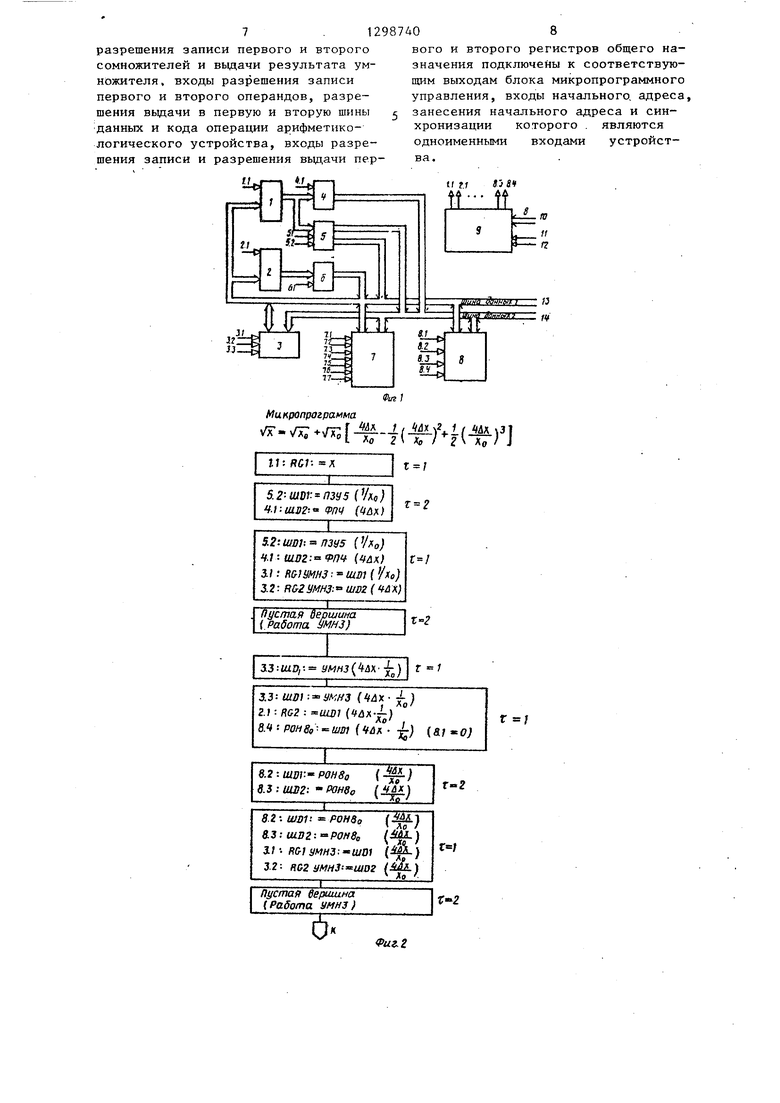

На фиг. 1 приведена функциональная схема устройства; на фиг, 2-9 - варианты реализации алгоритмов в блоке микропрограммного управления.,

Устройство содержит (фиг« 1) регистр 1 аргумента, регистр 2 поправок, умножитель 3, блок 4 памяти значений приращения, блок 5 памяти опорных значений функций, блок 6 памяти значений поправок, арифметико-логический блок 7, два регистра 8 общего назначения, блок 9 микропрограммного управления, вход 10 н ачального адреса, вход 11 занесения нач;зльного адреса, вход 12 синхронизации, первую и вторую шины 13 и 14 данных (ШД1 и

ЩЦ2).

Устройство для вычисления элементарных функций работает под воздействием блока 9. Последовательность управляющих сигналов формируется в соответствии с алгоритмом вычисления элементарных функций. Например, функция 4х формируется по следующему алгоритму (фиг.2-5);(1)

- I- ЬАйХчг 1x4uxj - )

где - значение функции в опорной точке х„; 1/х - значение

о в в опорной точке х

о

значение поправки; 4йх 1

функздии - о

1,

Y х Ац

приращение функции.

Сигнал, сформированный на выходе 1,1 блока 9, служит для записи аргумента в регистр 1. Сигналы с выхода 2.1 презназначены ,цля записи в регистр 2 значения адреса блока 6 при вычислении функций и - соответ-

X

венно. Появление сигналов на выходах 3.1 и 3.2 соответствует записи первого и второго сомножителей соответственно в приемные регистры умножителя 3. По сигналу 3.3 результат операции умножения поступает в первую шину данных. Сигнал 4,1 позволяет вьщать на вторую шину данных значение прира

5

0

5

0

5

0

щения, сформированного в блоке 4.-, Сигналы 5.1 и 5.2 обеспечивает выдачу информации, считанной из блока 5, во вторую или в первую шины данных соответственно.. Формирование сигнала на выходе 6.1 разрешает вьщачу информации из блока 6 в первую шину данных. Сигналы, сформированные на выходах 7.1 и 7.2 блока 9, предназначены для записи первого и второго операндов в первый и во второй приемные регистры блока 7 .соответственно. Комбинация потенциалов на выходах 7.3, 7.4, 7.5 определяет код операции, выполняемой в блоке 7. Например 7,3, 7.4, 7.5 0,1, 1 соответствует выполнению операции вычитания со сдвигом вправо

--у{В-А), где В - второй операнд, А первый операнд.

По сигналам 7.6, 7.7 результат операции в блоке 7 поступает во вторую и в первую шины данных соответственно. Потенциал на выходе 8.1 служит для выбора регистра 8, а 8.4 обеспечивает запись информации в регистры 8. Сигналы 8.2, 8.3 предназна-. чены для чтения информации из регистров 8 а первую или во вторую шину данных соответственно.

Аргумент X по сигналу 1.1 записывается в регистр 1. Если аргумент х представить в следующем виде: х х(31), х(30), х(29),..., х(1), х(0), тогда величина х, имеет вид х х(30), х(29),...,х(23), х(22).

Величина х,, яв.пяется адресом блока 5, где хранятся опорные значения

„ 1

функции -

, -|хГ; девять старших

разрядов аргумента х поступают с выхода регистра 1 на адресные входы блока 5.

Значение аргумента х поступает с выхода регистра 1 на вход блока 4, которьй формирует из аргумента х значение приращения 4 (jx. Величину 4 UX.можно представить в следующем виде: 4 дх 0. 0000000 йх(23), йх(22),..,, йх(1), йх(0), 0,0.

По сигналу 5.2 значение функции , считанное из блока 5, поступает

J

через первую шину данных на первый

вход умножителя 3, а по сигналу 4.1 значение 4 fvx поступает с выхода блока 4 через вторую шину данных на

3129

второй вход умножителя 3. По сигналам 3.1 и 3.2 значения 1/х и 4 йх записываются в приемные регистры умножителя 3. По сигналу 3.3 значение

4лх произведения с выхода умножителя

3 через шину 13 поступает на вход регистра 2 и на вход регистра 8. Есл

4 их произведение представить в виде

0

Ь о, ОПОООПООр (22), р(21),...,

0

р(1), р(0), то по сигналу 2.1 в регистр 2 запишется число

4 дх

RG2:

о

- f л /.л

р(22), р(21),...,р(15).

которое служит адресом блока 6, где

1 ..4UXJ хранятся значения поправок - (,j .i20

0 По сигналу 8.4 в регистр 8 с адресом,

равным нулю (8.1 0), запишется зна АХ „ чение произведения . По сигналам

о25

8,2 и 8.3 из регистров с нулевым ад4 UX ресом произведение поступает

через шины 13 и 14 на первый и второй входы умножителя 3; по сигналам 3.1

Ч- Л X

и 3.2 величина записывается в

о 4 л X его регистры. Произведение ()

0

30

информация, считанная из регистра 8

с адресом единица (8.1 1) ,4д X

И поступает через шину

по сигналу 3.3 поступает на первьш вход блока 7 через шину 13. Блок 7 подготовлен к выполнению операции 1

13 на первьШ вход блока 7 и по сигна лу 7.1 записьшается в регистр блока - 7, при этом на блоке 7 выполняется

-у (В-А) сигналами 7.3., 7.4, 7.5 О,

операция

Г 12

/ -I(A)

/л V. /

Да2 X

лее по сигналу 8.2 производится счи- 1,1. По сигналу 7.1 в первый приемный 4 и х регистр блока 7, который соответству-40 Ь вание -

из регистра 8 с адресом

0

ет операнду А, заносится число

() , по сигналу 7.2 во второй eMHbtfi регистр, который соответствует

операнду В, заносится ноль. Результат45 операции на блоке 7 имеет вид

и по сигналу 7.7 попо сигналу 7.7 поступает на первый вход умножителя 3 по шине 13. Значение опорной величины функции Цх ,

, Л

ступает на вход регистра 8 по шине считанное из блока 5 по сигналу 5.1, 13. В результате выполненных операций 50 поступает через шину 14 на второй в регистре 8 с адресом ноль хранит- ход умножителя 3. Сигналы 3.1 и 3.2 xjjобеспечивают запись в регистры умно жителя соответственно величин ALU1 и

4х . Результат операции умножения 55 -{x -ALUI по сигналу 3.3 поступает на первый вход (блок 7 подготовлен к вьшолнению операции Сложение 7.3, 7,4, 7,5 1, 0,0)а величина Цх считывается из блока 5 и по сигналу

ся значение

Хо адресом единица

записано число

() , Значение поправки 2 Хо J

можно из блока 6

по подготовленному адресу в регистре 2. Согласно алгоритму величины

4 д, X

L 1. ixn L J

1/4йх

7Г

) необходимо сложить. Для этого устройство АЛУ 7 подготавливается к вьшолнению

по

операции Сложение с накоплением 7.3, 7.4, 7.5 (1,1,0). Поскольку первое слагаемое складывается с содержимым внутреннего регистра блока 7, то все его регистры предварительно обнуляются. Для этого организует- ся дополнительная команда Обнуление регистров АЛУ 7.3, 7.4, 7.5 (0,0,0),

которая вьтолняется перед Z.c накоплением

По сигналу 6.1 значение поправки

3

) , считанное из блоков, по1/ дх

7Г ---

2х„

ступает на первый вход блока 7 по шине 13, а по сигналу 7.1 значение

Ь4ьх

запишется в регистр блока 7.

На блоке 7

выполняется операция

3

Г„ 1 х4йх .М„ „

О + у() , затем по сигналу. 8.2

L / XQ J

информация, считанная из регистра 8

с адресом единица (8.1 1) ,4д X

И поступает через шину

13 на первьШ вход блока 7 и по сигналу 7.1 записьшается в регистр блока ; 7, при этом на блоке 7 выполняется

операция

Г 12

/ -I(A)

/л V. /

Да2 X

ее по сигналу 8.2 производится счи- 4 и х Ь вание -

лее по сигналу 8.2 производи 4 и х Ь вание -

ноль

на х блока

из регистра 8

0

(8.1 0). Результат 7

3

ALU1

1/4йх

i .

/

XQ 2 хо

XQ

по сигналу 7.7 поступает на вход умножителя 3 по шине 13ние опорной величины функции Цх ,

считанное из блока 5 по сигналу 5 поступает через шину 14 на второй ход умножителя 3. Сигналы 3.1 и 3 обеспечивают запись в регистры умн

5.1 поступает на второй вход блока, Результат операции умножения 4х ALUI и величина 4х по сигналам 7.1 и 7.2 записываются в регистры блока 7. Согласно выражению (1) на АЛУ 7 выполня- ется операция Суммирование. В результате имеем следующее:

43Г 4 + -4х: ALU1.

памяти опорных значений функции,блок памяти значений поправок, умножитель- и .арифметико-логический блок, отличающееся тем, что, с делью повышения точности вычислений, в него введены блок памяти значений приращения, два регистра общего наз - начения и блок микропрограммного управления, информационный вход регистра аргумента подключен через первую шину данных к входу аргумента устройства, выход умножителя подключен через первую шину данных к информационному входу регистра поправок.

.Величина 4х по 7.7 через ШЛ1 поступает на вход регистра 8, а по сигналу 8.4 -{х запип1ется в регистр 8 с адресом 8.1 0.

Время работы (tp) блочного процес-t5 к входу первого операнда арифметико- сора при вычислении функции -ч по логического блока и к информационному

входу первого регистра общего назначения и к входу регистра аргумента, выход которого подключен к адресному 20

приведенной микропрограмме можно записать в следующем виде:

звг,

входу блока памяти значений приращения, а выход старших разрядов регист- I ра аргумента подключен к адресному

входу блока памяти значений приращения, а выход старших разрядов регист- I ра аргумента подключен к адресному

входу блока опорных значений функции, выход регистра поправок подключен к

где г, - длительность одного такта,

Интервал изменения аргумента х лежит в пределах 0,25 х 1. ТочI-1-3-Z I: JJif1 J ri i I JJll| /cl v-/ лч./ ГьЛЕимс;п j

ность вычисления функции равна 2,7 ;.. - адресному входу блока памяти попра- причем аргумент может быть представвок, выход которого через первую шину лен как в фиксированном, так я в плавающем формате, при этом порядок числа должен быть четным числом. Напри.,р

данных подключен ко входу первого операнда арифметико-логического бломер, если х представить в виде , JQ где X - мантисса; р - порядок, зна- чение -4х 2 3 .

Устройство для вычисления элемен- тарньтх функций обладает широкими функциональными возможностями. Оно порка, выход блока памяти значений приращения подключен через вторую шину данных к входу второго сомножителя умножителя, выход первого регистра общего назначения подключен через первую шину данных к входу первого

воляет вычислять элементарные фунции: сомножителя умножителя, выход блока .памяти опорных значений функции под31ПХ, COSX, arcsinx и другие.

алгоритмы вычисления которых можно реализовать на приведенной структуре.

Например, алгоритм вьиисления функции имеет вид (см. фиг. 6-9)

2

X.

,4дх

Z - - )

X J

Время работы блочного процессора при вычислении функции 1/х tp 64 с, . Диапазон изменения аргумента 0, 1е Точность вьгчисления функции 1/х равна 2 . Операцию деления можно выполнять через функцию 1/х.

Формула изобретения

Устройство для вьгчисления элементарных функцШ1, содержащее регистр аргумента, регистр поправок, блок

памяти опорных значений функции,блок памяти значений поправок, умножитель- и .арифметико-логический блок, отличающееся тем, что, с делью повышения точности вычислений, в него введены блок памяти значений приращения, два регистра общего наз - начения и блок микропрограммного управления, информационный вход регистра аргумента подключен через первую шину данных к входу аргумента устройства, выход умножителя подключен через первую шину данных к информационному входу регистра поправок.

входу первого регистра общего назначения и к входу регистра аргумента, выход которого подключен к адресному

входу блока памяти значений приращения, а выход старших разрядов регист I ра аргумента подключен к адресному

входу блока опорных значений функции выход регистра поправок подключен к

I: JJif1 J ri i I JJll| /cl v-/ лч./ ГьЛЕимс;п j

..вок, выход которого через первую шину

данных подключен ко входу первого операнда арифметико-логического бловок, выход которого через первую шину

ка, выход блока памяти значений приращения подключен через вторую шину данных к входу второго сомножителя умножителя, выход первого регистра общего назначения подключен через первую шину данных к входу первого

40

45

ключен через вторую шину данных к входу второго операнда арифметико- логического блока и к входу первого сомножителя умножителя, выход второго регистра общего назначения через вторую шину данных подключен к входу первого операнда арифметико-логического блока и к входу второго сомножителя умножителя, выход арифметико- логического блока подключен через вторую шину данных к информационному входу второго регистра общего назна Q чения, к входу второго сомножителя умножителя и к входу первого операнда арифметико-логического блока,вход записи регистра аргумента, вход записи регистра поправок, входы разре шения вьщачи данных блока памяти значений приращения и блока памяти значений поправок, входы разрешения выдачи в первую и во вторую шины данных блока опорных значений функции,входы

разрешения записи первого и второго сомножителей и выдачи результата умножителя, входы разрешения записи первого и второго операндов, разрешения вьщачи в первую и вторую шины Сданных и кода операции арифметико- логического устройства, входы разрешения записи и разрешения выдачи перМикропрограмма

л-.(

вого и второго регистров общего назначения подключены к соответствующим выходам блока микропрограммного управления, входы начального, адреса, занесения начального адреса и синхронизации которого . являются одноименными входами устройства.

Фиг. 2

и Л.ЙГСвДП: АЛУ7 формируется коп

{KSZ-R&n

3.3 : ЩД; ()

Т

ДЗ- Ш -I/WHJ

i KffiAAin «««шв; 72 S яагдлу : в о

Пустая вершина (работа АМ7}

1

7.7.й/и7.

a/MA.f1

.г1 Ло /4

Т7:«иВ1 , д., ,- а :РОНТ: Ш « -у(-) (Я/«П

((1рр)ААУ7формируетсяКОП„05нуАение HGAAJ)

Листая BepOLUHa (Работа АЛУТ)

1

73.7.,75(,l.0 срорми(ется с накопителем e.1;ULiSJ:« ПЗУ6 Г l(.Mi.)1

а1.:шш.(-)

Г) ,

г; :ЯС ЛЛУ7: «ОШ/

(Работа АЛУ7)

&2 itUS1: POHj -j( - ) (

8.21ШЛ:шрон, -|.( :2Mj2J gf

Foo -р-

7.1 : ЯС Л«/7: «ШД Г F- i ( )Л

Фиг.З

г-1

Ts/

)

Г) , ЛЛ лЗ т

IJl хГ/ J

с«/

Фиг.З

(Работа АЛУ7)

йх

8.г:Ш1))-:.рОН, {-) (8.)

8. « POWo (8.)

иг--UtDI РОНо {8.)

7.1 : ffCf АЛУ7: ШП ( - )

АО

Пустая вершина (Работа АМ7)

1.7-IUDI : ГЛЛУ -1-/М1,)3- ( VflA «+ 5.1:ШВг:-ПЗ /5 (/7„) «0 / о

7.7-.ШВ7:вМ97 (АЛЫТ;

5.1 U/DZi-nsyS (vTo)

3.1 R(HS/MW3 «U/DI (

А ногимнз: в:шп2(Л(,)

I

Пустая вершина {работа имнз)

f5,r4,7..0.0)-АЛУ1 аюрнириет «ОП()

13: шш t«HMH3 (/FO Алуг; И шог-- ша5(/7о)

азчиш- -аимз(/до -ллг/ J

3.| Ш0г ПЗУ5 (а)

7. t ЯС ЛЛУ7 (ШВТ(/д с-/1/1УГ)

7.2 t ВСг ЛЛа7 : ШВ2 ( Л )

Пустая вершина {работа АЛУ7)

17-.ШЩ Л.У7б/Г / +1, (Mif.C) 1

L Ло / Z X(7 J

()

8Л:РОНо-ш1 1 ) ((

йх

) (8.)

Г-

rcf

f ;

п

ФигЧГ-/

.5

Минропрограмма

I

7

.в(1- Л , , , xotxo (

П : КС.1:-Х

1

52 : « ЛЗ{/5 ( У;( 1.1 {Л02 - РПЦ(Ч&К}

5.2:iUD1 i /73t/( /До) ./ : fiLB2 (ЛХ) ЗТ J R(WMH3: UiD} ( Др) 3.2 Я( 2 f/MW J: iUD2(A Л )

1

Пустая Вершмна (PaSomcL Умнз)

I

J.3- . -умнз(f --j-o)r ° 1

3.3 iUffJ : M/f3 (ЛХ- Удд)

2.1 (2 ) 8.4 POH8o- UUJ)l( ()

А /1

а 2 : POWo аз . UUf2: РОНво

JL

8.2. ULDI .РОНво 8.Ъ°.Ш.02 РОНво

3.1 Я&1УМНЗ : ШВ1 (-)

3.2: Л&2 УМНЗ : 1Ш32(3)

1

Пустая вершина (Работа 1JMH3)

дх

Ха

t

Гв2

t-y

Г«.2

Га|

ш

г«;

Фиг. 6

7.3,7М,7.5(0,1.0)- АЛУ 7 (рормирует КОП (R&2- Я&/} 3,3:tUD1 ()

«eeeiceeieeeieiii e ™ ™ ™ ™ ™

т

3.Z: lUSI .ВИНЗ

7.J ; ЯС; 7.2 : Я г2ЛЛ«/7: «0

1

Пустая оеришна (Ри5отаААУ7)

1

77:Ш1 :-ЛЛУ7 -(Я

7.7:Ш2 / -АЛУ7

at )(&; /)

j

Г-;

г3, 7.,7.5( МУ7 срормирует. КОП„Обнуление КОАЛУ

Г

Пустая вершина (Радота АЛУ)

23,7.ftt 15 (1,1,0) АЛУ7 срормирует. К on 2 с накопителем В.1:ШГ. ПЗУ5 (2-)

1

6. J: « ПЗУб ( 2 f 7.1 : R&f : - ULD -|( 2- -

I

(Работа АЛУ7}

8.г iUDJ . С-) (8.)

8.2 : ШОГ- РОНо( (8.) 7.1 RG1 ААУ7 « Ш01

Xtf -J

6

г«/

Г-/

Г-;

Г-;

r-j

tr-/

t

.) Т

Xtf -J

Фиг. 7

(Работа ААУ7)

8.2 UW : POHr :()(

1

5.г-Ш, ,((/7«/Л - i

B.2 tUD1- POH}()

7.1: КЭ ААУ7-Ш01 ()

Г«7

flycmap оерш-ина (Работа

77. .-/1/1 7 /1 7 4: (2 А Ж. L лоАО Хо

7.7-Ш.(У7 (AlMl) 8. POHj -tUSI (ALU1)

8.2 PJ// (ALU1)

8.3 : ШО. W/У; (ALUDГ /

75, 7, 7.5(1,0,0) : АЛУ7 срормарует КОП(Н01 - Я&2)

8.2 ШШ: POHf 83 UID21 POHj 7.1 : КОАЛУ -.0101 (ALU1)

7.2: ПС2АЛУ7 UUB2(ALUJ)

памимммапншммннпиа мванпмпмммнввпмааиното

Пустая вершина ( PaSoma AMI)

I

75 г . (ги/,//;

Q.Z ШВГ. ПЗУ5 ( Уло)

Г«7

Г 5

Г«|

t /

t «f

Фиг.8

7.6-ШВ2: АЛУ7(2АЛУ1) 5.2«Ш41; ПЗУ5(7;)

3.1: Я01УМНЗ: шигС-)

3.2«С2УМНЗ:«ШЛ2(2АЛУ1)

1

Пустая вершина (Работа УМнЗ)

«:шМ,..м„з(|.Д|(г Mi , -г(

51:ШС2:г-ПЗа5(-)

7.3, 7., 75 (0,1,0) ЛЛа формирует. КОП (RG2-RG Г);

13:Ш01г УМНЗ -|-)АЛУ1)

5:|:ШД2: ПЗУ5(4-)

/2 N

7.1 : К&1МУ7: 1и01(2МУ1)

7.2 Я&2АЛУ7 (-)

пустая 6ерш.ана (PaSoma АЛУ7)

()()1}

7.7:ШВТ

77: Ш1)

/ .-Г

1; .:рОНо:«Ш1)|(1-2) ()

Редактор Н. Егорова

Составитель А. Ушаков Техред М.Ходанич 1

Заказ 890/51Тираж 67.3Подписное

ВНИИПИ -Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

r«J

r«l

Г-/

Фиг. 9

Корректоре. Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Устройство для вычисления тригонометрических функций | 1985 |

|

SU1257639A1 |

| Вычислительное устройство | 1988 |

|

SU1539772A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Арифметическое устройство | 1980 |

|

SU885993A1 |

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| Устройство для вычисления функции табличным методом | 1986 |

|

SU1383337A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных ЭВМ для аппаратурной реализации функциональных зависимостей. Цель изобретения - повышение точности вычислений. Устройство содержит регистр аргумента, регистр поправок, умножитель, блок памяти значений приращения,блок памяти опорных значений функции,блок памяти значений поправок, арифметико- логический блок, два регистра общего назначения, блок микропрограммного управления. Принцип работы устройства основан на вычислении элементарных функций под управлением микропрограммного блока в соответствии с алгоритмом вычисления этих функций за с счет использования блока памяти опор- ных значений функций и блок памяти значений поправок. 9 ил.

| Устройство для вычисления элементарных функций | 1982 |

|

SU1061136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный генератор | 1982 |

|

SU1072033A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ртутный выпрямитель | 1936 |

|

SU50419A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-06-06—Подача