v{

Рх/2+0, если порядок операнда четный; Р„/2+1, если порядок операнда нечетный,

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1988 |

|

SU1529214A1 |

| Устройство для преобразования координат | 1988 |

|

SU1541600A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для преобразования координат | 1986 |

|

SU1405051A1 |

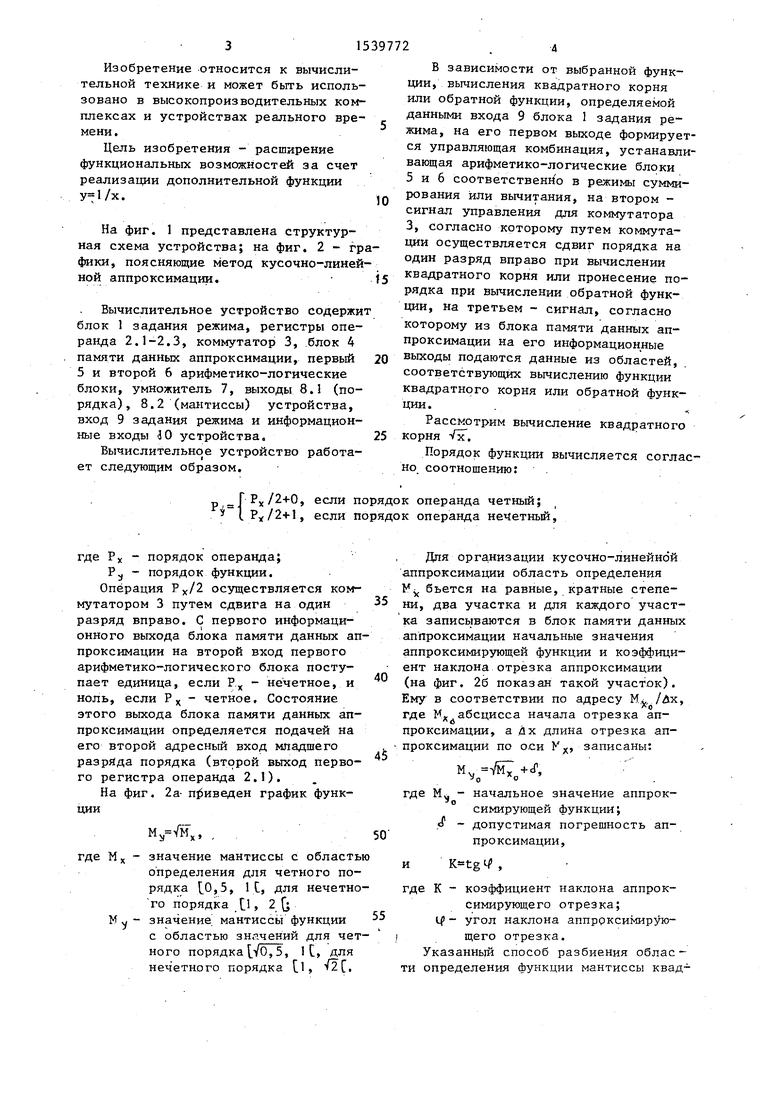

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных комплексах и устройствах реального времени. Цель изобретения - расширение функциональных возможностей устройства за счет реализации функции Y=1/X. Вычислительное устройство содержит блок 1 задания режима, регистры операнда. 2.1-2.3, коммутатор 3, блок 4 памяти данных аппроксимации, арифметико-логические блоки 5,6, умножитель 7 с соответствующими связями. 2 ил.

где Рх порядок операнда; РЭ - порядок функции.

Операция Р х/2 осуществляется коммутатором 3 путем сдвига на один разряд вправо. С первого информационного выхода блока памяти данных аппроксимации на второй вход первого арифметико-логического блока поступает единица, если Рх - нечетное, и ноль, если РХ четное. Состояние этого выхода блока памяти данных аппроксимации определяется подачей на его второй адресный вход младшего разряда порядка (второй выход первого регистра операнда 2.1).

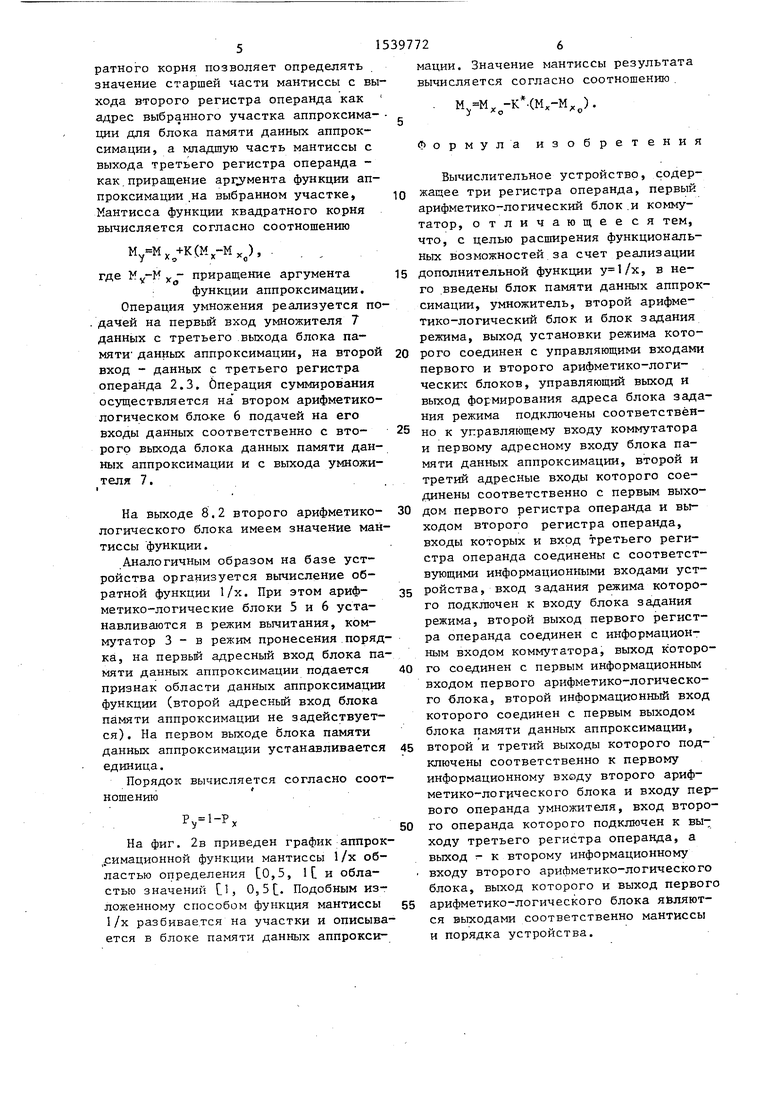

На фиг. 2а приведен график функции

,

Мх - значение мантиссы с областью определения для четного порядка 0,5, 1C, для нечетного порядка , 2 (j

Му- значение мантиссы функции 5 с областью знгчений для четного порядка УО,5, 1 С, для нечетного порядка 1, 2,

0

5 ,

0

Для организации кусочно-линейной аппроксимации область определения Fv бьется на равные, кратные степени, два участка и для каждого участка записываются в блок памяти данных аппроксимации начальные значения аппроксимирующей функции и коэффициент наклона отрезка аппроксимации (на фиг. 26 показан такой участок). Ему в соответствии по адресу Mv /dx,

АО

где М абсцисса начала отрезка апЛо

проксимации, а дх длина отрезка аппроксимации по оси Кх, записаны:

+ cf

где My - начальное значение аппроксимирующей Функции; о - допустимая погрешность аппроксимации,

и

K-tgif,

где К - коэффициент наклона аппроксимирующего отрезка; Ц - угол наклона аппррксимирую- i щего отрезка.

Указанный способ разбиения области определения Функции мантиссы квадратного корня позволяет определять значение старшей части мантиссы с выхода второго регистра операнда как адрес выбранного участка аппроксима- ции для блока памяти данных аппроксимации, а младшую часть мантиссы с выхода третьего регистра операнда - как приращение аргумента функции аппроксимации .на выбранном участке, Мантисса функции квадратного корня вычисляется согласно соотношению

+к(мх-мХв),

где УУ-МХ- приращение аргумента

функции аппроксимации. Операция умножения реализуется подачей на первьй вход умножителя 7 данных с третьего выхода блока памяти1 данных аппроксимации, на второй вход - данных с третьего регистра операнда 2.3. Операция суммирования осуществляется на втором арифметико- логическом бло-ке 6 подачей на его входы данных соответственно с второго выхода блока данных памяти данных аппроксимации и с выхода умножителя 7. i

На выходе 8,2 второго арифметико- логического блока имеем значение мантиссы функции.

Аналогичным образом на базе устройства организуется вычисление обратной функции 1/х. При этом арифметико-логические блоки 5 и 6 устанавливаются в режим вычитания, коммутатор 3 - в режим пронесения порядка, на первьй адресный вход блока памяти данных аппроксимации подается признак области данных аппроксимации функции (второй адресный вход блока памяти аппроксимации не задействует- ся). На первом выходе блока памяти данных аппроксимации устанавливается единица.

Порядок вычисляется согласно соотношению

у х

На фиг. 2в приведен график аппрок- тримационной функции мантиссы 1/х областью определения tO,5, 1 и областью значений , 0, 5 С. Подобным изложенному способом функция мантиссы 1/х разбивается на участки и описывается в блоке памяти данных аппрокси

мации. Значение мантиссы результата вычисляется согласно соотношению

м-м,

(МХ-М.

).

0

0

5

0

5

0

5

0

5

Формула изобретения

Вычислительное устройство, содержащее три регистра операнда, первый арифметико-логический блок и коммутатор, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации 5 дополнительной функции , в него введены блок памяти данных аппроксимации, умножитель, второй арифметико-логический блок и блок задания режима, выход установки режима которого соединен с управляющими входами первого и второго арифметико-логических блоков, управляющий выход и выход формирования адреса блока задания режима подключены соответственно к управляющему входу коммутатора и первому адресному входу блока памяти данных аппроксимации, второй и третий адресные входы которого соединены соответственно с первым выходом первого регистра операнда и выходом второго регистра операнда, входы которых и вход третьего регистра операнда соединены с соответствующими информационными входами устройства, вход задания режима которого подключен к входу блока задания режима, второй выход первого регистра операнда соединен с информационным входом коммутатора, выход которого соединен с первым информационным входом первого арифметико-логического блока, второй информационный вход которого соединен с первым выходом блока памяти данных аппроксимации, второй и третий выходы которого подключены соответственно к первому информационному входу второго арифметико-логического блока и входу первого операнда умножителя, вход второго операнда которого подключен к выходу третьего регистра операнда, а выход - к второму информационному входу второго арифметико-логического блока, выход которого и выход первого арифметико-логического блока являются выходами соответственно мантиссы и порядка устройства.

0,54

Фиг. г

Составитель А.Чудак Редактор М.Петрова Техред М.Ходанич

Hxl

Мщ+лх м

Корректор С.Шекмар

Авторы

Даты

1990-01-30—Публикация

1988-03-09—Подача