113

Изобретение относится к вычислительной технике и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении,

Целью изобретения - повышение надежности устройства.

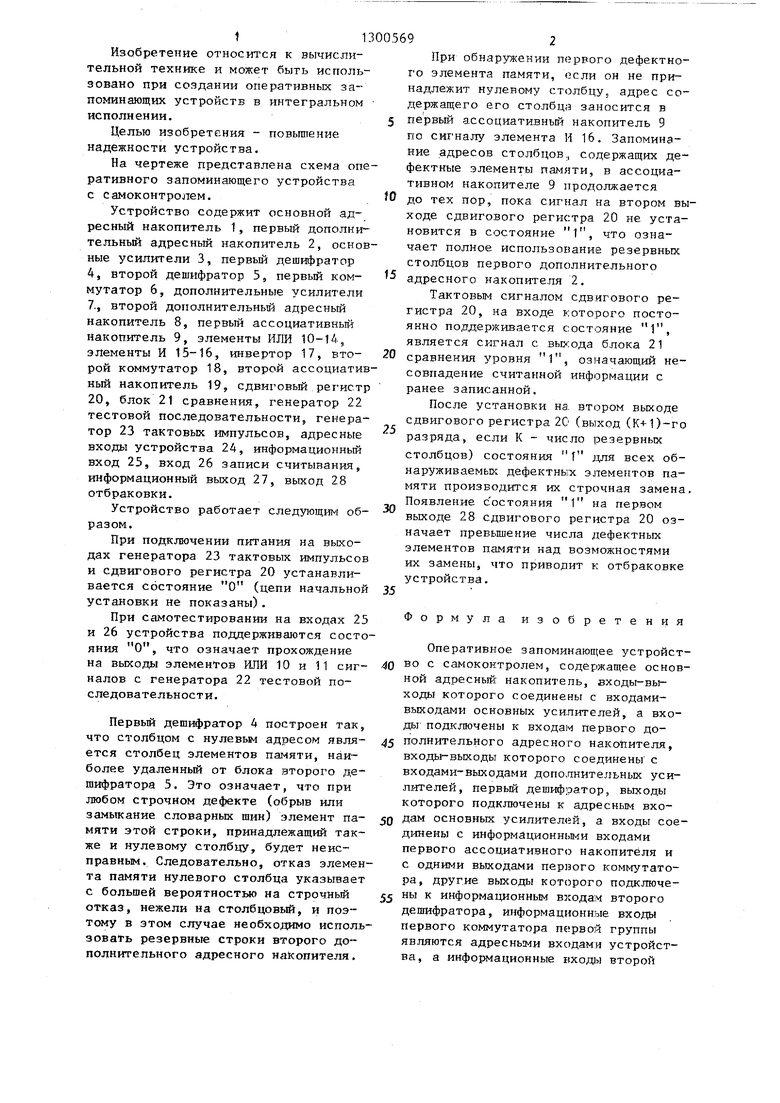

На чертеже представлена схема оперативного запоминающего устройства с самоконтролем.

Устройство содержит основной адресный накопитель 1, первый дополнительный адресный накопитель 2, основные усилители 3, первый дешифратор 4, второй дешифратор 5, первый ком- мутатор 6, дополнительные усилители 7., второй дополнительный адресный накопитель 8, первый ассоциативньй накопитель 9, элементы ИЛИ 10-14, элементы И 15-16, инвертор 17, второй коммутатор 18, второй ассоциатив ный накопитель 19, сдвиговый регистр 20, блок 21 сравнения, генератор 22 тестовой последовательности, генератор 23 тактовых импульсов, адресные входы устройства 24, информационный вход 25, вход 26 записи считывания, информационный выход 27, выход 28 отбраковки.

Устройство работает следующим образом.

При подключении питания на выходах генератора 23 тактовых импульсов и сдвигового регистра 20 устанавливается состояние О (цепи начальной установки не показаны).

При самотестировании на входах 25 и 26 устройства поддерживаются состояния О, что означает прохождение на выходы элементов ИЛИ 10 и 11 сигналов с генератора 22 тестовой последовательности.

Первьй дешифратор 4 построен так, что столбцом с нулевым адресом является столбец элементов памяти, наиболее удаленный от блока второго дешифратора 5. Это означает, что при любом строчном дефекте (обрыв или замыкание словарных шин) элемент памяти этой строки, принадлежащий также и нулевому столбцу, будет неисправным. Следовательно, отказ элемента памяти нулевого столбца указывает с большей вероятностыо на строчный отказ, нежели на столбцовый, и поэтому в этом случае необходимо испол.ъ- зовать резервные строки второго дополнительного адресного накопителя.

При обнарзшении первого дефектного элемента памяти, если он не принадлежит нулевому столбцу,, адрес содержащего его столбца заносится в первый ассоциативный накопитель 9 по сигналу элемента И 16. Запоминание адресов столбцов,, содержащих дефектные элементы памяти, в ассоциативном накопителе 9 продолжается до тех пор, пока сигнал на втором выходе сдвигового регистра 20 не установится в состояние 1, что означает полное использование резервных столбцов первого дополнительного адресного накопителя 2.

Тактовым сигналом сдвигового регистра 20, на входе которого постоянно поддерживается состояние 1, является сигнал с вькода блока 21 сравнения уровня 1, означающий несовпадение считанной информации с ранее записанной.

После установки на. втором выходе сдвигового регистра 20 (выход (К+1)-го разряда, если К - число резервных столбцов) состояния f ;р1Я всех об- наруживаемьк дефектных элементов памяти производится их строчная замена. Появление с остояния 1 на первом выходе 28 сдвигового регистра 20 означает превышение числа дефектных элементов пг1мяти над возможностями их замены, что приводит к отбраковке устройства.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее основной адресный: накопитель, входы-выходы которого соединены с входами- выходами основных уси.пителей, а входы подключены к входам первого дополнительного адресного накопителя, входы-выходы которого соединены с входам и-выходам и допо.пнительных усилителей, первый дешифратор, выходы которого подключены к адресным вхоязм основных усилителей, а входы сое- д1-шены с информационными входами первого ассоциативного накопителя и с одними выходами первого коммутатора, другие выходы котсзрого подключены к информационным входам второго дешифратора, информационн.ые входы первого коммутатора первой группы ЯВ.ПЯЮТСЯ адресньми входами устройства, а информационные входы второй

группы и управляющий вход соединены соответственно с выходами группы и первым выходом генератора тестовой последовательности, вход которого подключен к выходу генератора тактовых импульсов, информационные и управляющие входы основных и дополнительных усилителей соединены соответственно с выходами первого и второго элементов ИЛИ, первые входы которых являются соответственно информационным и управляющим входами устройства а информационные выходы основных и дополнительных накопителей подключены к информационным входам второго коммутатора, блок сравнения, выход которого соединен с входом сдвигового регистра, первый выход которого является выходом отбраковки устройства, третий элемент ИЛИ, второй вход которого подключен к второму выходу генератора тестовой последовательности, отличающеес тем, что, с целью повышения надежности устройства, в него введены второй дополнительньй адресный накопитель, второй ассоциативный накопитель, четвертый и пятый элементы ИЖ, первьй и второй элементы И,

инвертор, причем входы-выходы второго первого и второго элементов ИЛИ со- дополнительного адресного накопителя соединены с входами-вьлходами основных усилителей , а входы подк1аочены к входам четвертого элемента ИЛИ и к выходам второго ассоциативного на- 35 копителя, управляющий вход которого

ответственно, первый и второй входы первого элемента И соединены соответственно с выходсж блока сравнения и с выходом третьего элемента ИЛИ, первый вход которого подключен к второму выходу сдвигового регистра.

O

5

0

5

соединен с входом инвертора и выходом первого элемента И, а информационные входы подключены к информационным входам дешифратора, управляющий вход которого соединен с выходом четвертого элемента ИЛИ, а выходы подключены к входам основного адресного накопителя, выход пятого элемента ИЛИ соединен с управляющим входом второго коммутатора а входы подключены к адресным входам дополнительных усилителей и к выходам первого ассоциативного накопителя, управ-ляющий вход которого соединен с выходом второго элемента И, второй вход которого подключен к выходу инвертора, а первый вход соединен с выходом блока сравнения, первьй и второй входы которого подключены к выходам первого и второго элементов ИЛИ, третий вход соединен с выходом второго коммутатора и является информационным выходом устройства, а четвертый вход подключен к выходу генератора тактовых импульсой, вход которого соединен с первым выходом генератора тестовой последовательности, третий и четвертый выходы которого подключены к вторьм входам

первого и второго элементов ИЛИ со-

ответственно, первый и второй входы первого элемента И соединены соответственно с выходсж блока сравнения и с выходом третьего элемента ИЛИ, первый вход которого подключен к второму выходу сдвигового регистра.

Составитель О.Исаев Редактор Н.Киштулинец Техред Л.Сердюкова

Заказ 1156/53 Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1317485A1 |

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2014 |

|

RU2535182C1 |

| Устройство для индикации | 1984 |

|

SU1427414A1 |

| Генератор случайного Марковского процесса | 1982 |

|

SU1070548A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Центральный процессор | 1980 |

|

SU890400A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Целью изобретения является повьппейие надежности устройства. Устройство содержит основной адресный накопитель, первый и второй дополнительные адресные накопители, основные и дополнительные усилители, первый и второй дешифраторы, первый и второй коммутаторы, первый к второй ассоциативные накопители, элементы ИЛИ, элементы И, инвертор, сдвиговый регистр, блок сравнения, генератор тестовой последовательности, генератор тактовых импульсов. Повышение надежности устройства достигается за счет обнаружения неисправных строк и столбцов элементов памяти и замены их на резервные элементы памяти, что позволяет в конечном итоге повысить выход годных микросхем и срок их эксплуатации.1 ил. (Л ел а

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU855739A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-30—Публикация

1985-09-30—Подача