Изобретение относится к вычислительной технике и может быть использовано при создании оперативных запоминающих устройств.

Целью изобретения является снижение потребляемой мощности в режиме внещ- них обращений.

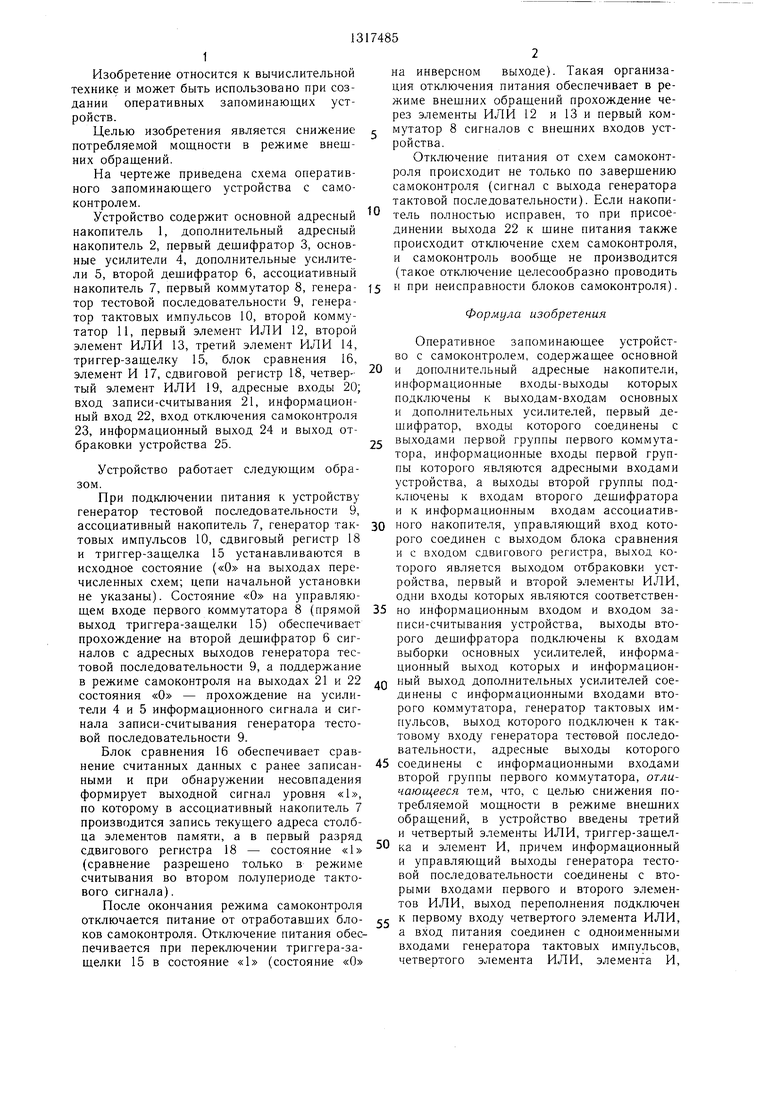

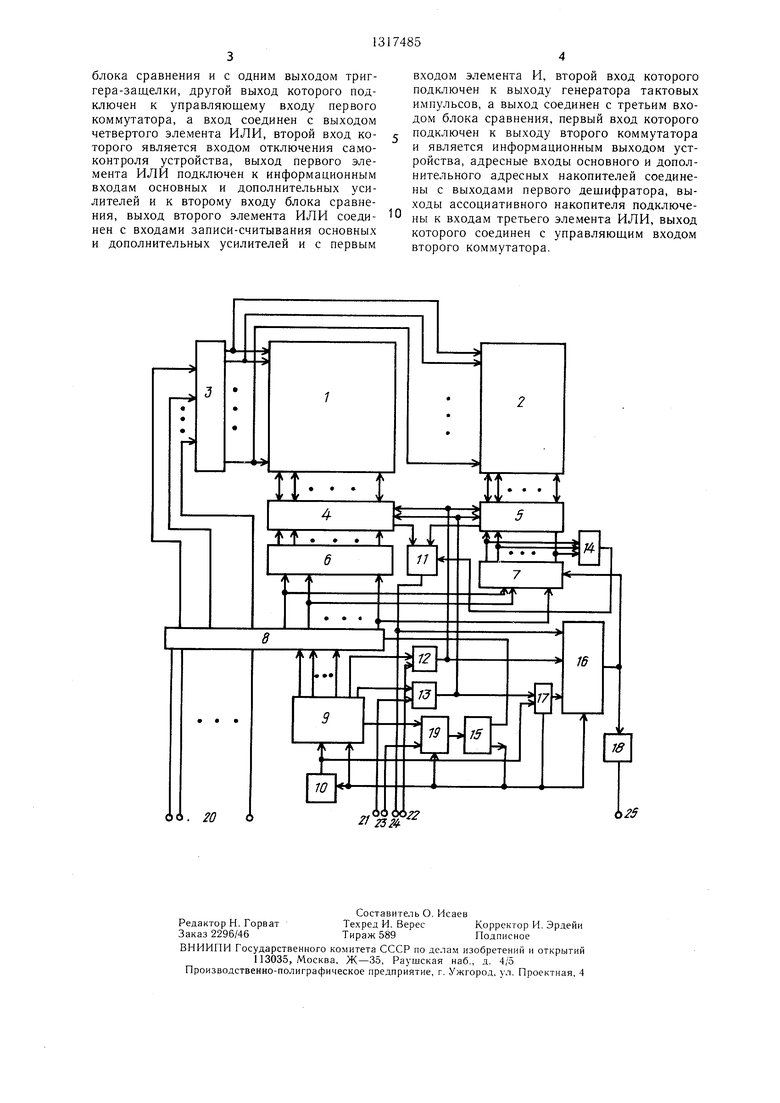

На чертеже приведена схема оперативного запоминающего устройства с самоконтролем.

Устройство содержит основной адресный накопитель 1, дополнительный адресный накопитель 2, первый дещифратор 3, основные усилители 4, дополнительные усилители 5, второй дешифратор 6, ассоциативный накопитель 7, первый коммутатор 8, генера- тор тестовой последовательности 9, генератор тактовых импульсов 10, второй коммутатор И, первый элемент ИЛИ 12, второй элемент ИЛИ 13, третий элемент ИЛИ 14, триггер-защелку 15, блок сравнения 16, элемент И 17, сдвиговой регистр 18, четвертый элемент ИЛИ 19, адресные входы 20; вход записи-считывания 21, информационный вход 22, вход отключения самоконтроля 23, информационный выход 24 и выход отбраковки устройства 25.

Устройство работает следующим образом.

При подключении питания к устройству генератор тестовой последовательности 9, ассоциативный накопитель 7, генератор тактовых импульсов 10, сдвиговый регистр 18 и триггер-защелка 15 устанавливаются в исходное состояние («О на выходах перечисленных схем; цепи начальной установки не указаны). Состояние «О на управляющем входе первого коммутатора 8 (прямой выход триггера-защелки 15) обеспечивает прохождение на второй дешифратор 6 сигналов с адресных выходов генератора тестовой последовательности 9, а поддержание в режиме самоконтроля на выходах 21 н 22 состояния «О - прохождение на усилители 4 и 5 информационного сигнала и сигнала записи-считывания генератора тестовой последовательности 9.

Блок сравнения 16 обеспечивает сравнение считанных данных с ранее записанными и при обнаружении несовпадения формирует выходной сигнал уровня «1, по которому в ассоциативный накопитель 7 производится запись текущего адреса столбца элементов памяти, а в первый разряд сдвигового регистра 18 - состояние «1 (сравнение разрешено только в режиме считывания во втором полупериоде тактового сигнала).

После окончания режима самоконтроля отключается питание от отработавщих блоков самоконтроля. Отключение питания обеспечивается при переключении триггера-защелки 15 в состояние «1 (состояние «О

на инверсном выходе). Такая организация отключения питания обеспечивает в режиме внещних обращений прохождение через элементы ИЛИ 12 и 13 и первый коммутатор 8 сигналов с внещних входов устройства.

Отключение питания от схем самоконтроля происходит не только по заверщению самоконтроля (сигнал с выхода генератора тактовой последовательности). Если накопитель полностью исправен, то при присоединении выхода 22 к щине питания также происходит отключение схем самоконтроля, и самоконтроль вообще не производится (такое отключение целесообразно проводить и при неисправности блоков самоконтроля).

Формула изобретения

0

5

0

Оперативное запоминающее устройство с самоконтролем, содержащее основной и дополнительный адресные накопители, информационные входы-выходы которых подключены к выходам-входам основных и дополнительных усилителей, первый дешифратор, входы которого соединены с выходами первой группы первого коммутатора, информационные входы первой группы которого являются адресными входами устройства, а выходы второй группы подключены к входам второго дещифратора и к информационным входам ассоциативного накопителя, управляющий вход которого соединен с выходом блока сравнения и с входом сдвигового регистра, выход которого является выходом отбраковки устройства, первый и второй элементы ИЛИ, одни входы которых являются соответствен5 но информационным входом и входом записи-считывания устройства, выходы второго дещифратора подключены к входам выборки основных усилителей, информационный выход которых и информационный выход дополнительных усилителей соединены с информационными входами второго коммутатора, генератор тактовых им- гЕульсов, выход которого подключен к тактовому входу генератора тестовой последовательности, адресные выходы которого соединены с информационными входами второй группы первого коммутатора, отличающееся тем, что, с целью снижения потребляемой мощности в режиме внешних обращений, в устройство введены третий и четвертый элементы ИЛИ, триггер-защел50 ка и элемент И, причем информационный и управляющий выходы генератора тестовой последовательности соединены с вторыми входами первого и второго элементов ИЛИ, выход переполнения подключен к первому входу четвертого элемента ИЛИ, а вход питания соединен с одноименными входами генератора тактовых импульсов, четвертого элемента ИЛИ, элемента И,

0

5

55

блока сравнения и с одним выходом триггера-защелки, другой выход которого подключен к управляющему входу первого коммутатора, а вход соединен с выходом четвертого элемента ИЛИ, второй вход которого является входом отключения самоконтроля устройства, выход первого элемента ИЛИ подключен к информационным входам основных и дополнительных усилителей и к второму входу блока сравнения, выход второго элемента ИЛИ соединен с входами записи-считывания основных и дополнительных усилителей и с первым

входом элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход соединен с третьим входом блока сравнения, первый вход которого

подключен к выходу второго коммутатора и является информационным выходом устройства, адресные входы основного и дополнительного адресных накопителей соединены с выходами первого дешифратора, выходы ассоциативного накопителя подключены к входам третьего элемента ИЛИ, выход которого соединен с управляющим входом второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1300569A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Динамическое запоминающее устройство с автономным контролем | 1984 |

|

SU1290418A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1554030A1 |

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1156145A1 |

| Запоминающее устройство | 1975 |

|

SU556494A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании оперативны.х запоминающих устройств в интегральном исполнении. Целью изобретения является снижение потребляемой мощности в режиме внещних обращений. Устройство содержит основной и дополнительный адресные накопители, ассоциативный накопитель, основные и дополнительный усилители, первый и второй дещифраторы, первый и второй коммутаторы, генератор тактовых импульсов, генератор тестовой последовательности, элементы ИЛИ, И, блок сравнения, триггер-защелку, сдвиговый регистр. Уменьщение мощности потребления в режиме внешних обращений достигается за счет отключения питания от блоков самоконтроля. 1 ил. g со 4 00 ел

6 6 . Л7 о

„, ОО OQ22

2} 2324Ь $

| Электроника, 1981, № 15, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-15—Публикация

1985-09-30—Подача