Изобретение относится к вычислительной технике и может быть использовано для контроля многоразрядных полупроводниковых оперативных запоминающих устройств.

Цель изобретения - повышение быстродействия и достоверности контроля.

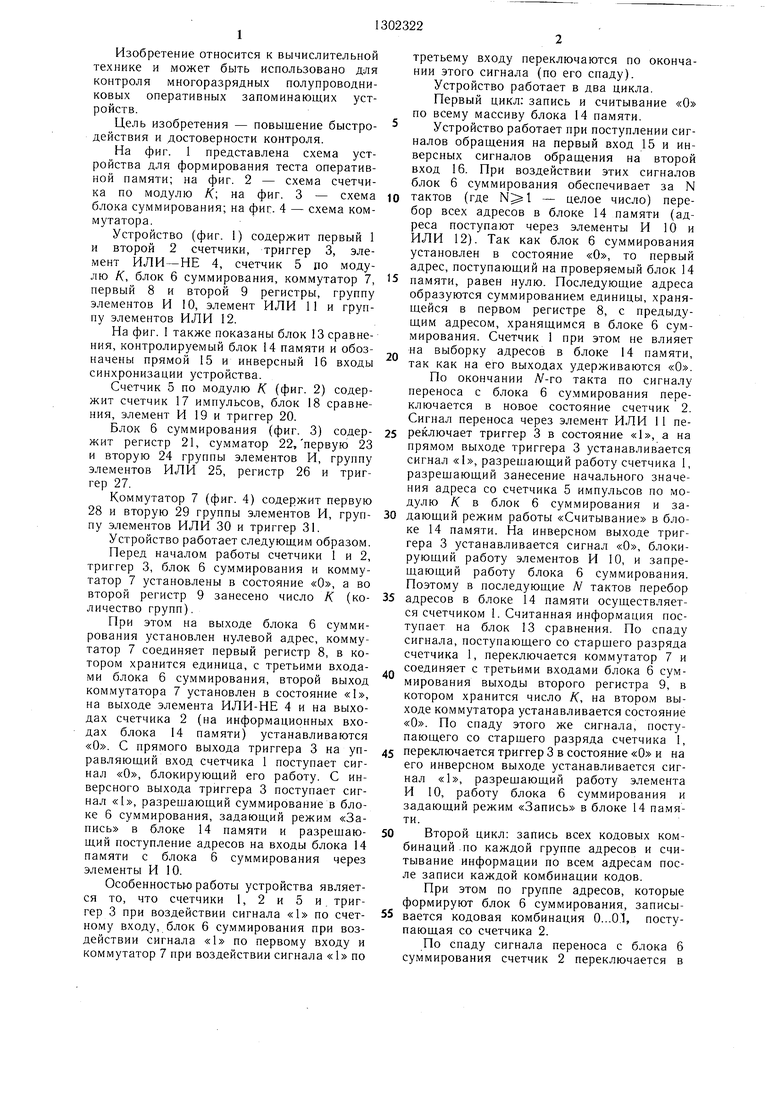

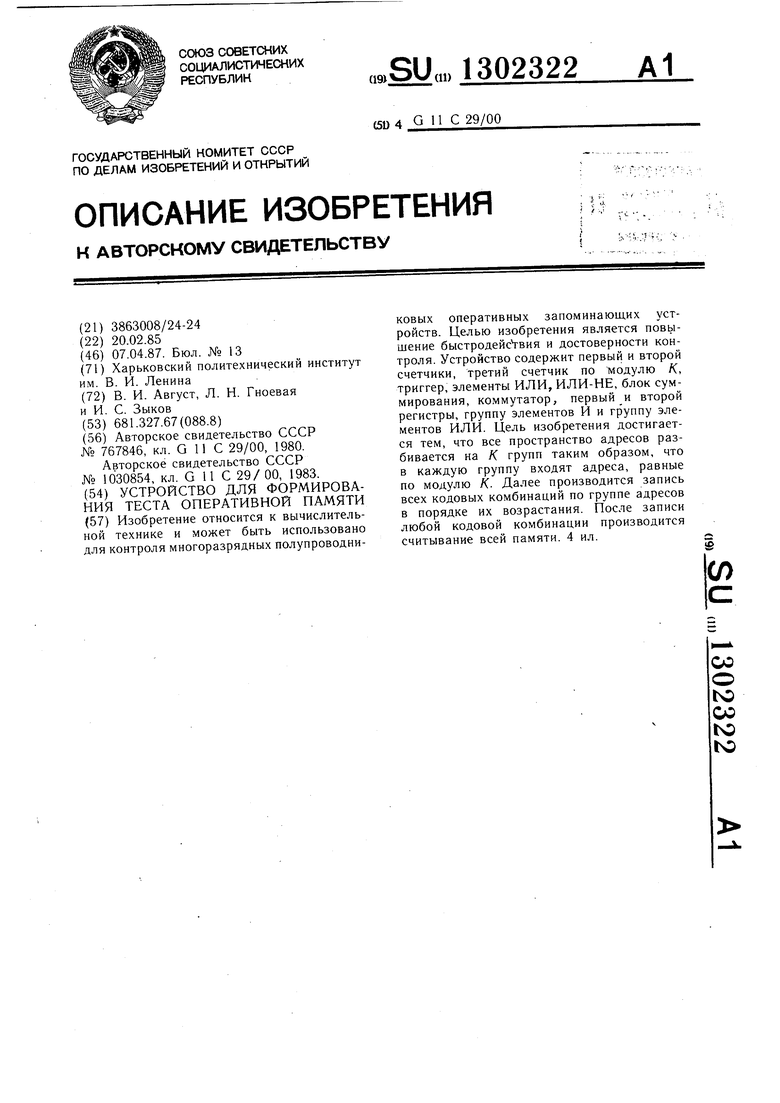

На фиг. 1 представлена схема устройства для формирования теста оперативной памяти; на фиг. 2 - схема счетчика по модулю К , на фиг. 3 - схема блока суммирования; на фиг. 4 - схема коммутатора.

Устройство (фиг. 1) содержит первый 1 и второй 2 счетчики, триггер 3, эле- .мент ИЛИ-НЕ 4, счетчик 5 по моду10

третьему входу переключаются по окончании этого сигнала (по его спаду).

Устройство работает в два цикла.

Первый цикл; запись и считывание «О по всему массиву блока 14 памяти.

Устройство работает при поступлении сигналов обращения на первый вход 15 и инверсных сигналов обращения на второй вход 16. При воздействии этих сигналов блок 6 суммирования обеспечивает за N тактов (где - целое число) перебор всех адресов в блоке 14 памяти (адреса поступают через элементы И 10 и ИЛИ 12). Так как блок б суммирования установлен в состояние «О, то первый адрес, поступающий на проверяемый блок 14

лю К, блок б суммирования, коммутатор 7, 5 памяти, равен нулю. Последующие адреса первый 8 и второй 9 регистры, группуобразуются суммированием единицы, храняэлементов И 10, элемент ИЛИ 11 и груп-щейся в первом регистре 8, с предыдущим адресом, хранящимся в блоке б суммирования. Счетчик 1 при этом не влияет

пу элементов ИЛИ 12.

На фиг. 1 также показаны блок 13 сравнения, контролируемый блок 14 памяти и обозначены прямой 15 и инверсный 16 входы синхронизации устройства.

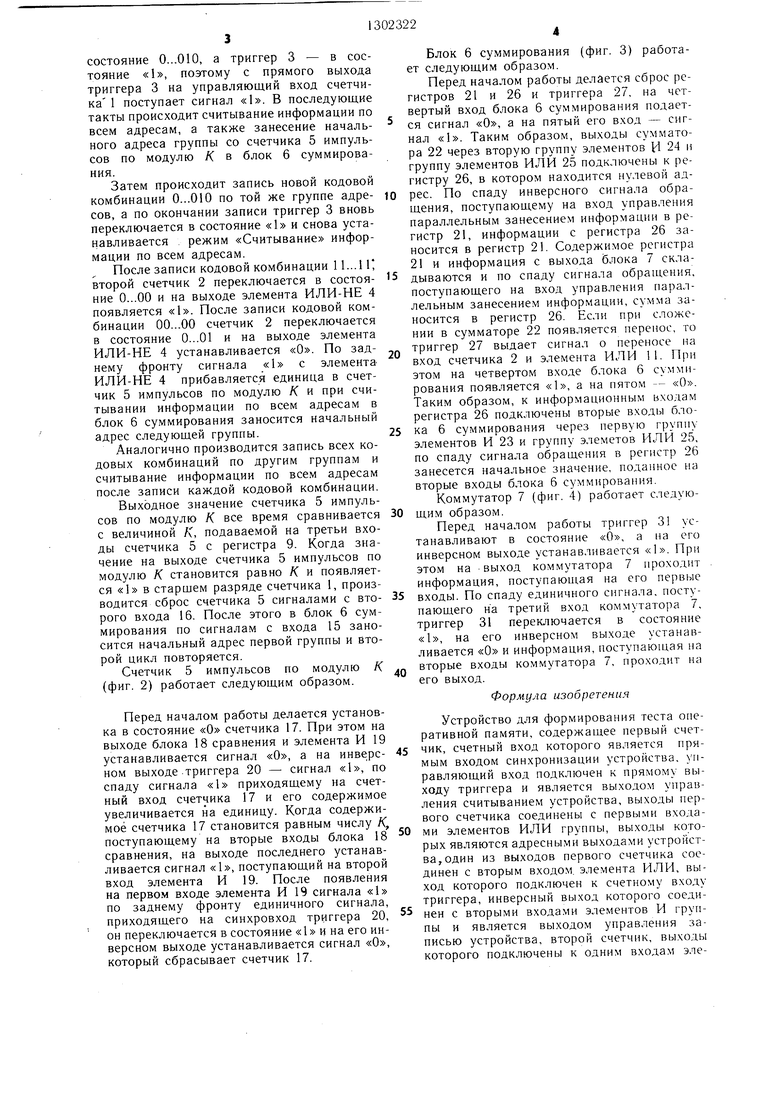

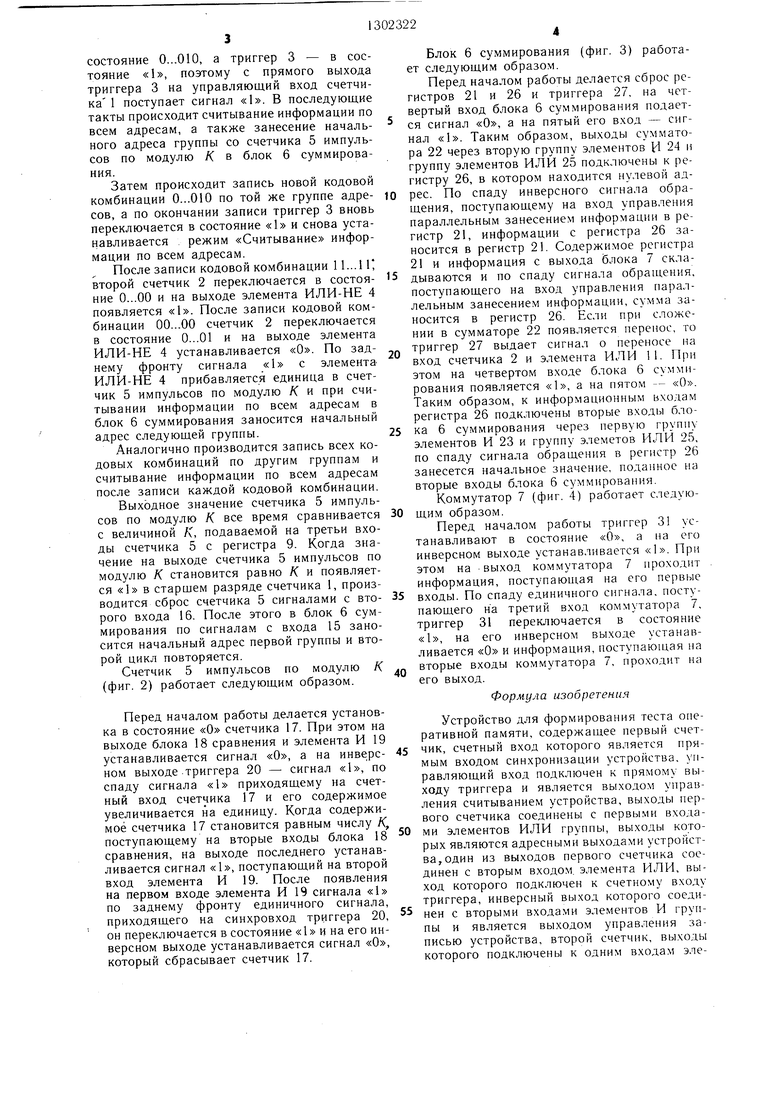

Счетчик 5 по модулю К (фиг. 2) содержит счетчик 17 импульсов, блок 18 сравнения, элемент И 19 и триггер 20.

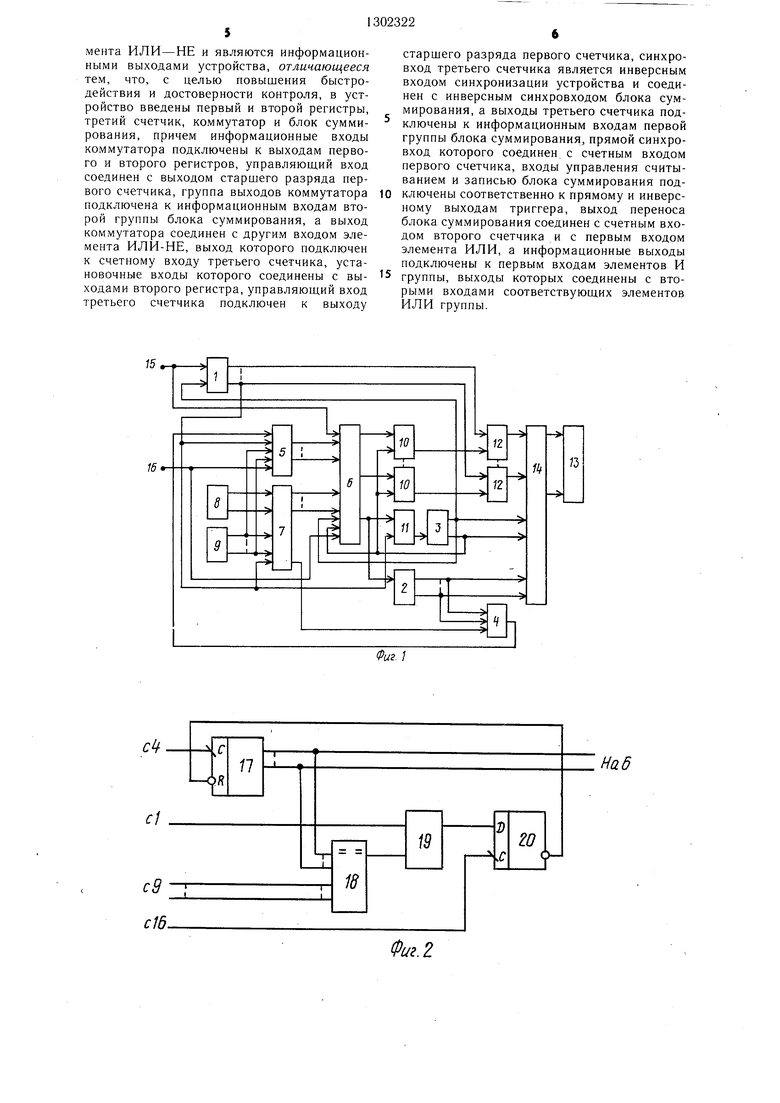

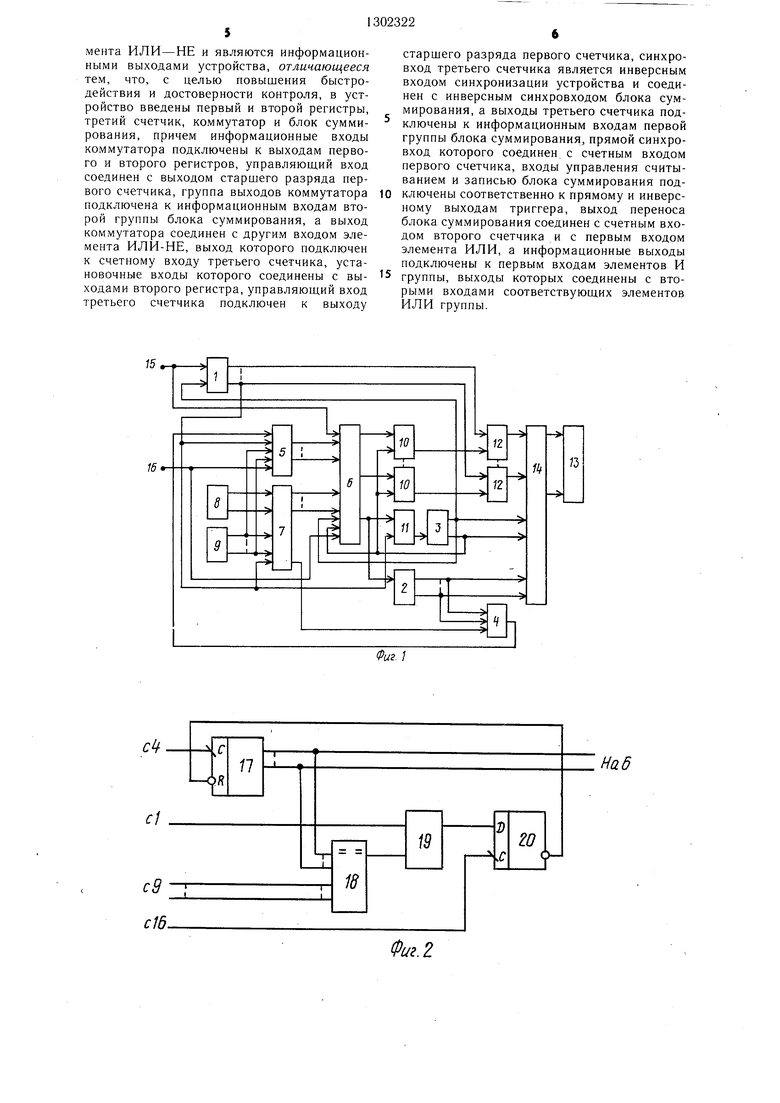

Блок 6 суммирования (фиг. 3) содержит регистр 21, сумматор 22, первую 23 и вторую 24 группы элементов И, группу элементов ИЛИ 25, регистр 26 и триггер 27.

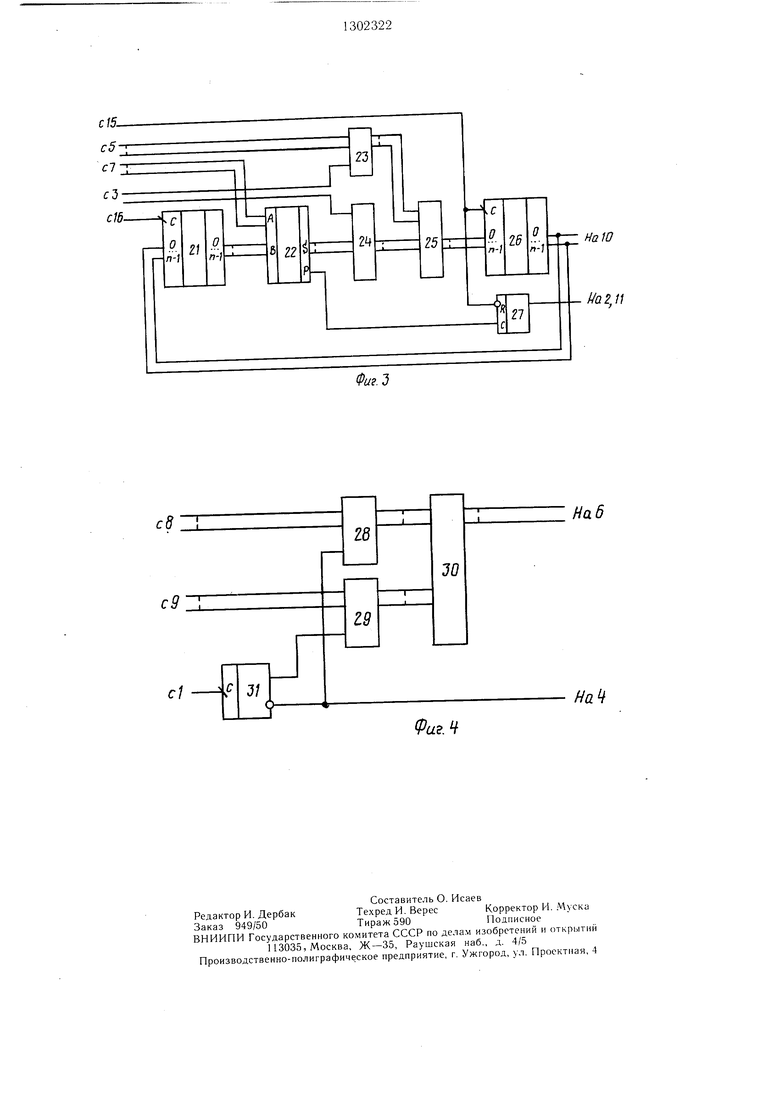

Коммутатор 7 (фиг. 4) содержит первую

20

25

на выборку адресов в блоке 14 памяти, так как на его выходах удерживаются «О. По окончании N-ro такта по сигналу переноса с блока 6 суммирования переключается в новое состояние счетчик 2. Сигнал переноса через элемент ИЛИ 11 переключает триггер 3 в состояние «1, а на прямом выходе триггера 3 устанавливается сигнал «1, разрешающий работу счетчика I, разрешающий занесение начального значения адреса со счетчика 5 импульсов по модулю К в блок б суммирования и за28 и вторую 29 группы элементов И, груп- 30 дающий режим работы «Считывание в бло- пу элементов ИЛИ 30 и триггер 31.ке 14 памяти. На инверсном выходе тригУстройство работает следующим образом.гера 3 устанавливается сигнал «О, блокиПеред началом работы счетчики 1 и 2,рующий работу элементов И 10, и запретриггер 3, блок 6 суммирования и комму-щающий работу блока б суммирования,

татор 7 установлены в состояние «О, а воПоэтому в последующие Л тактов перебор

второй регистр 9 занесено число /С (ко- 35 адресов в блоке 14 памяти осуществляется счетчиком 1. Считанная информация поступает на блок 13 сравнения. По спаду сигнала, поступающего со старшего разряда счетчика 1, переключается коммутатор 7 и соединяет с третьими входами блока 6 суммирования выходы второго регистра 9, в

личество групп).

При этом на выходе блока б суммирования установлен нулевой адрес, коммутатор 7 соединяет первый регистр 8, в котором хранится единица, с третьими входами блока 6 суммирования, второй выход коммутатора 7 установлен в состояние «1, на выходе элемента ИЛИ-НЕ 4 и на выходах счетчика 2 (на информационных входах блока 14 памяти) устанавливаются

40

котором хранится число /С, на втором выходе коммутатора устанавливается состояние «О. По спаду этого же сигнала, поступающего со старшего разряда счетчика 1,

.0. С прямого выхода триггера 3 на уп- 45 переключается триггер 3 в состояние «О и на

его инверсном выходе устанавливается сигнал «1, разрешающий работу элемента И 10, работу блока б суммирования и задающий режим «Запись в блоке 14 памяти.

50 Второй цикл: запись всех кодовых комбинаций -ПО каждой группе адресов и считывание информации по всем адресам после записи каждой комбинации кодов.

При этом по группе адресов, которые формируют блок б суммирования, записыравляющий вход счетчика 1 поступает сигнал «О, блокирующий его работу. С инверсного выхода триггера 3 поступает сигнал «1, разрешающий суммирование в блоке 6 суммирования, задающий режим «Запись в блоке 14 памяти и разрешающий поступление адресов на входы блока 14 памяти с блока 6 суммирования через элементы И 10.

Особенностью работы устройства является то, что счетчики 1, 2 и 5 и. триггер 3 при воздействии сигнала «1 по счет-55 вается кодовая комбинация О...01, посту- ному входу, блок б суммирования при воз-пающая со счетчика 2.

действии сигнала «1 по первому входу иПо спаду сигнала переноса с блока б

коммутатор 7 при воздействии сигнала «1 посуммирования счетчик 2 переключается в

третьему входу переключаются по окончании этого сигнала (по его спаду).

Устройство работает в два цикла.

Первый цикл; запись и считывание «О по всему массиву блока 14 памяти.

Устройство работает при поступлении сигналов обращения на первый вход 15 и инверсных сигналов обращения на второй вход 16. При воздействии этих сигналов блок 6 суммирования обеспечивает за N тактов (где - целое число) перебор всех адресов в блоке 14 памяти (адреса поступают через элементы И 10 и ИЛИ 12). Так как блок б суммирования установлен в состояние «О, то первый адрес, поступающий на проверяемый блок 14

памяти, равен нулю. Последующие адреса образуются суммированием единицы, храня

на выборку адресов в блоке 14 памяти, так как на его выходах удерживаются «О. По окончании N-ro такта по сигналу переноса с блока 6 суммирования переключается в новое состояние счетчик 2. Сигнал переноса через элемент ИЛИ 11 переключает триггер 3 в состояние «1, а на прямом выходе триггера 3 устанавливается сигнал «1, разрешающий работу счетчика I, разрешающий занесение начального значения адреса со счетчика 5 импульсов по модулю К в блок б суммирования и задающий режим работы «Считывание в бло- ке 14 памяти. На инверсном выходе тригкотором хранится число /С, на втором выходе коммутатора устанавливается состояние «О. По спаду этого же сигнала, поступающего со старшего разряда счетчика 1,

переключается триггер 3 в состояние «О и на

состояние 0...010, а триггер 3 - в состояние «1, поэтому с прямого выхода триггера 3 на управляющий вход счетчика 1 поступает сигнал «1. В последующие такты происходит считывание информации по всем адресам, а также занесение начального адреса группы со счетчика 5 импульсов по модулю К. в блок 6 суммирования.

Затем происходит запись новой кодовой комбинации 0...010 по той же группе адресов, а по окончании записи триггер 3 вновь переключается в состояние «1 и снова устанавливается режим «Считывание информации по всем адресам.

После записи кодовой комбинации 11...11 второй счетчик 2 переключается в состояние 0...00 и на выходе элемента ИЛИ-НЕ 4 появляется «1. После записи кодовой комбинации 00...00 счетчик 2 переключается в состояние 0...01 и на выходе элемента ИЛИ-НЕ 4 устанавливается «О. По заднему фронту сигнала «1 с элемента ИЛИ-НЕ 4 прибавляется единица в счетчик 5 импульсов по модулю К и при считывании информации по всем адресам в блок 6 суммирования заносится начальный адрес следующей группы.

Аналогично производится запись всех кодовых комбинаций по другим группам и считывание информации по всем адресам после записи каждой кодовой комбинации.

Выходное значение счетчика 5 импульсов по модулю К все время сравнивается с величиной /, подаваемой на третьи входы счетчика 5 с регистра 9. Когда значение на выходе счетчика 5 импульсов по модулю К становится равно К и появляется «1 в старшем разряде счетчика 1, производится сброс счетчика 5 сигналами с второго входа 16. После этого в блок б суммирования по сигналам с входа 15 заносится начальный адрес первой группы и второй цикл повторяется.

Счетчик 5 импульсов по модулю К (фиг. 2) работает следующим образом.

Перед началом работы делается установка в состояние «О счетчика 17. При этом на выходе блока 18 сравнения и элемента И 19 устанавливается сигнал «О, а на инверсном выходе триггера 20 - сигнал «1, по спаду сигнала «1 приходящему на счетный вход счетчика 17 и его содержимое увеличивается на единицу. Когда содержимое счетчика 17 становится равным числу К, поступающему на вторые входы блока 18 сравнения, на выходе последнего устанавливается сигнал «1, поступающий на второй вход элемента И 19. После появления на первом входе элемента И 19 сигнала «1 по заднему фронту единичного сигнала, приходящего на синхровход триггера 20, он переключается в состояние «1 и на его инверсном выходе устанавливается сигнал «О, который сбрасывает счетчик 17.

Блок 6 суммирования (фиг. 3) работает следующим образом.

Перед началом работы делается сброс регистров 21 и 26 и триггера 27, на четвертый вход блока 6 суммирования подает- ся сигнал «О, а на пятый его вход - сигнал «1. Таким образом, выходы сумматора 22 через вторую группу элементов И 24 и группу элементов ИЛИ 25 подключены к регистру 26, в котором находится нулевой ад0 рее. По спаду инверсного сигнала обращения, поступающему на вход управления параллельным занесением информации в регистр 21, информации с регистра 26 заносится в регистр 21. Содержимое регистра 21 и информация с выхода блока 7 скла5 дываются и по спаду сигнала обращения, поступающего на вход управления параллельным занесением информации, сумма заносится в регистр 26. Если при сложении в сумматоре 22 появляется перенос, то триггер 27 выдает сигнал о переносе на вход счетчика 2 и элемента ИЛИ 11. При этом на четвертом входе блока 6 суммирования появляется «1, а на пятом - «О. Таким образом, к информационным входам регистра 26 подключены вторые входы бло5 ка 6 суммирования через первую группу элементов И 23 и группу элеметов ИЛИ 25, по спаду сигнала обращения в регистр 26 занесется начальное значение, поданное на вторые входы блока 6 суммирования.

Коммутатор 7 (фиг. 4) работает следую0 щим образом.

Перед началом работы триггер 31 устанавливают в состояние «О, а на его инверсном выходе устанавливается «1. При этом на ВЫХОД коммутатора 7 проходит информация, поступающая на его первые

входы. По спаду единичного сигнала, поступающего на третий вход коммутатора 7, триггер 31 переключается в состояние «1, на его инверсном выходе уста на tv ливается «О и информация, поступающая на

вторые входы коммутатора 7, проходит на его выход.

Формула изобретения

Устройство для формирования теста оперативной памяти, содержащее первый счет5 чик, счетный вход которого является прямым входом синхронизации устройства, управляющий вход подключен к прямому выходу триггера и является выходом управления считыванием устройства, выходы первого счетчика соединены с первыми входа0 ми элементов ИЛИ группы, выходы которых являются адресными выходами устройства, один из выходов первого счетчика соединен с вторым входом, элемента ИЛИ, выход которого подключен к счетному входу триггера, инверсный выход которого соеди5 нен с вторыми входами элементов И группы и является выходом управления записью устройства, второй счетчик, выходы которого подключены к одним входам элемента ИЛИ-НЕ и являются информационными выходами устройства, отличающееся тем, что, с целью повышения быстродействия и достоверности контроля, в устройство введены первый и второй регистры, третий счетчик, коммутатор и блок суммирования, причем информационные входы коммутатора подключены к выходам первого и второго регистров, управляющий вход соединен с выходом старшего разряда первого счетчика, группа выходов коммутатора подключена к информационным входам второй группы блока суммирования, а выход KOMiMyTBTOpa соединен с другим входом элемента ИЛИ-НЕ, выход которого подключен к счетному входу третьего счетчика, установочные входы которого соединены с выходами второго регистра, управляющий вход третьего счетчика подключен к выходу

старшего разряда первого счетчика, синхро- вход третьего счетчика является инверсным входом синхронизации устройства и соединен с инверсным синхровходом блока суммирования, а выходы третьего счетчика подключены к информационным входам первой группы блока суммирования прямой синхро- вход которого соединен с счетным входом первого счетчика, входы управления считыванием и записью блока суммирования подключены соответственно к прямому и инверсному выходам триггера, выход переноса блока суммирования соединен с счетным входом второго счетчика и с первым входом элемента ИЛИ, а информационные выходы подключены к первым входам элементов И группы, выходы которых соединены с вторыми входами соответствующих элементов ИЛИ группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования теста блока оперативной памяти | 1990 |

|

SU1714609A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1987 |

|

SU1411777A1 |

| Устройство для адресации памяти на цилиндрических магнитных доменах | 1984 |

|

SU1185395A1 |

| Устройство для регистрации сейсмической информации | 1990 |

|

SU1811615A3 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля многоразрядных полупроводниковых оперативных запоминающих устройств. Целью изобретения является повьь шение быстродействия и достоверности контроля. Устройство содержит первый и второй счетчики, третий счетчик по модулю К, триггер, элементы ИЛИ, ИЛИ-НЕ, блок суммирования, коммутатор, первый и второй регистры, группу элементов И и группу элементов ИЛИ. Цель изобретения достигается тем, что все пространство адресов разбивается на К групп таким образом, что в каждую группу входят адреса, равные по модулю К. Далее производится запись всех кодовых комбинаций по группе адресов в порядке их возрастания. После записи любой кодовой комбинации производится считывание всей памяти. 4 ил. оэ о ьо ОО го to

Наб

Фиг. 2

НаЮ

с8.

На 6

На

| Устройство для контроля накопителей информации | 1979 |

|

SU767846A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля многоразрядных блоков памяти | 1982 |

|

SU1030854A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-07—Публикация

1985-02-20—Подача