J

О

о о

Изобретение относится к вычислительной технике и может быть использовано для контроля оперативных запоминающих устройств.

Целью изобретения является повышение достоверности контроля за счет увеличения количества переборов адресных цепей при считывании.

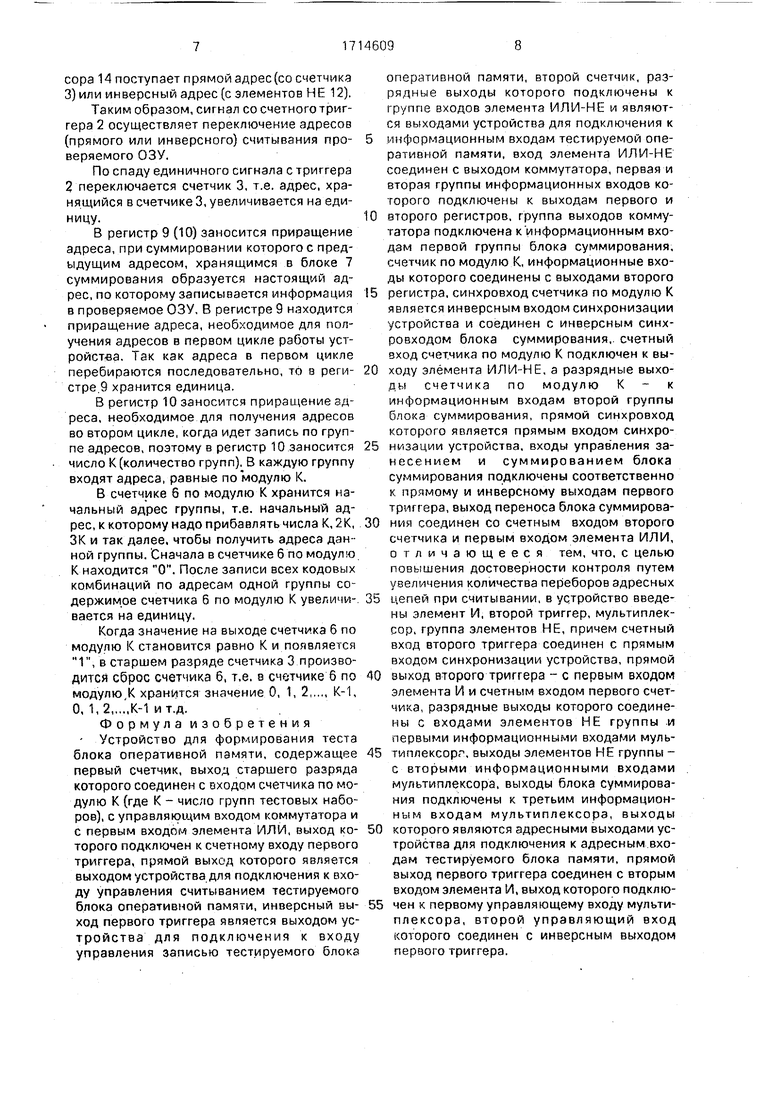

На фиг. 1 представлена схема устройства для формирования теста блока оперативной памяти; на фиг.2 - схема счетчика по модулю К; на фиг.З - схема блока суммирования; на фиг.4 - схема коммутатора; на фиг.5 - временная диаграмма формирования адреса считывания.

Устройство содержит первый 1 и второй 2 триггеры, первый 3 и второй 4 счетчики, элемент ИЛИ-НЕ 5, счетчик 6 по модулю К, блок7суммирования, коммутаторе, первый 9 и второй 10 регистры, элемент МЛИ 11, группу элементов НЕ 12, элемент И 13, мультиплексор 14, прямой вход 15 синхронизации устройства, инверсный вход 16 синхронизации устройства и блок 17 памяти..

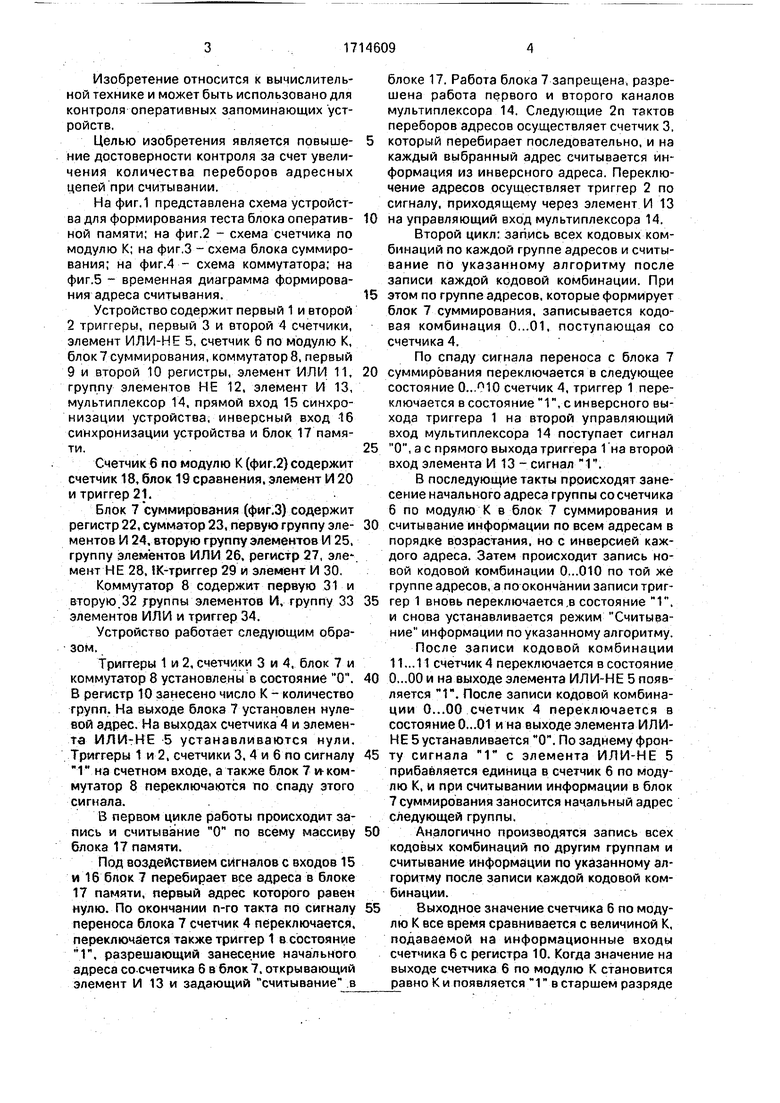

Счетчик б по модулю К (фиг,2) содержит счетчик 18, блок 19 сравнения, элемент И 20 и триггер 21,

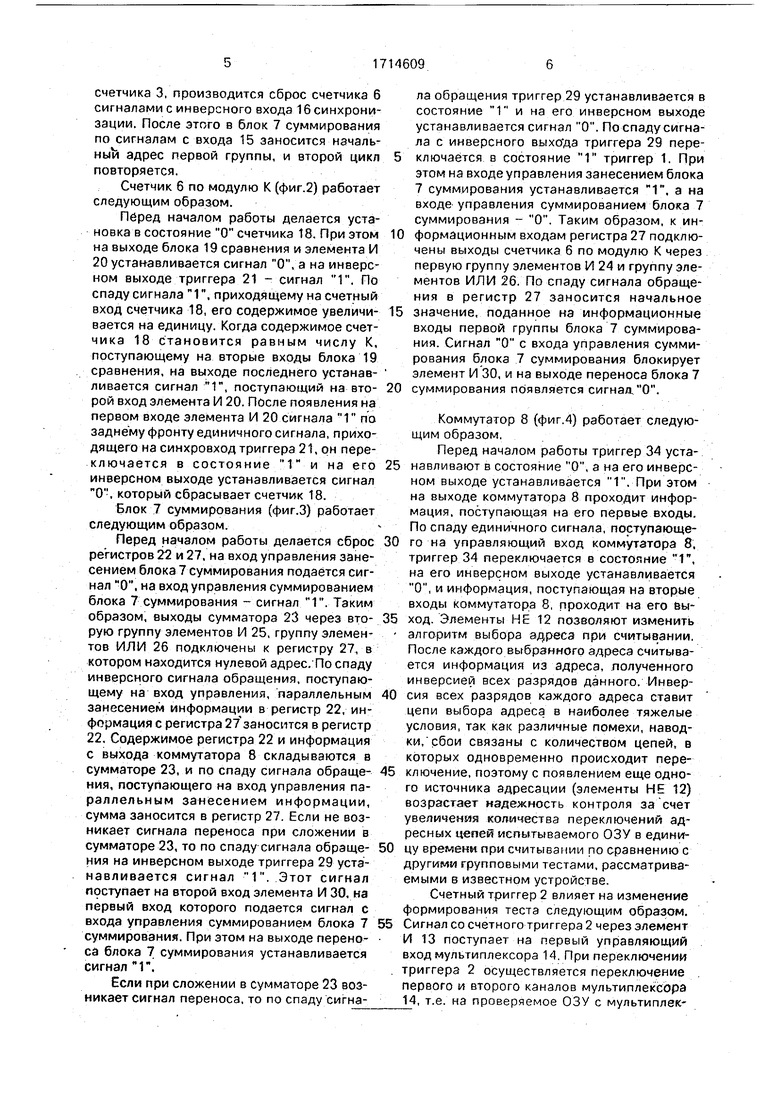

Блок 7 суммирования (фиг.З) содержит регистр 22, сумматор 23. первую группу элементов И 24, вторую группу элементов И 25, группу элементов ИЛИ 26. регистр 27, эле, мент НЕ 28,1К-триггер 29 и элемент И 30.

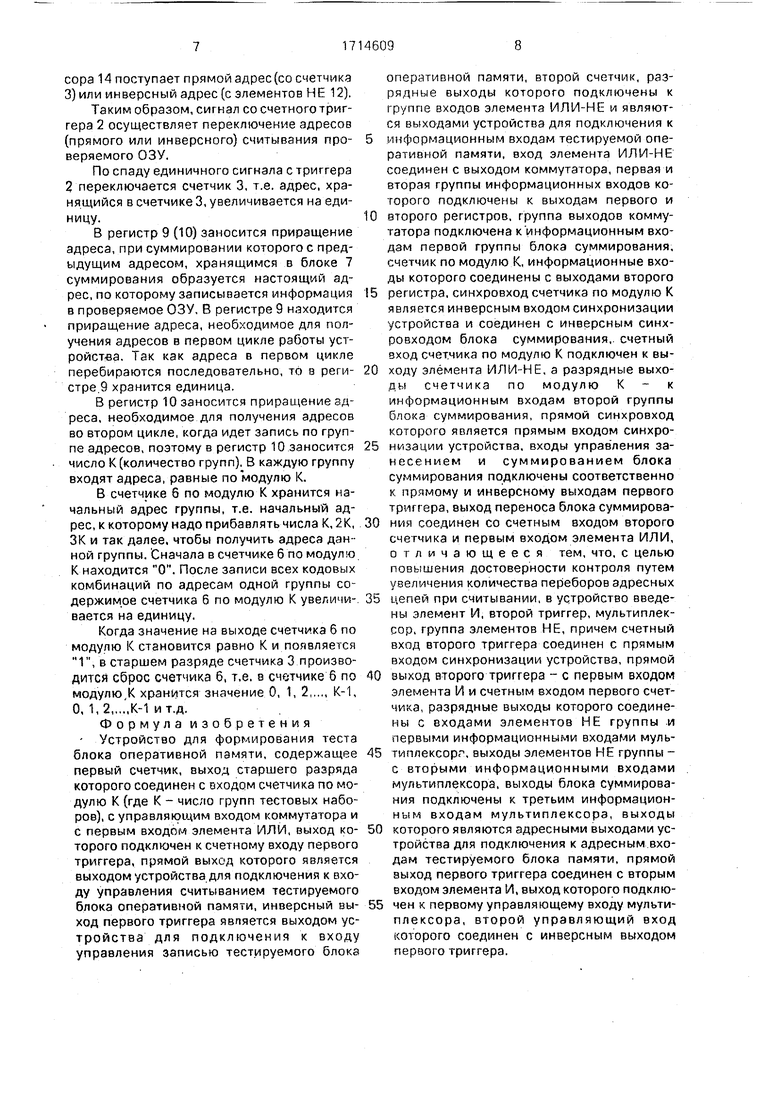

Коммутатор 8 содержит первую 31 и вторую.32 группы элементов И, группу 33 элементов ИЛИ и триггер 34.

Устройство работает следующим образом.

Тригтеры 1 и 2, счетчики 3 и 4, блок 7 и коммутатор 8 установлены в состояние О. В регистр 10 занесено число К - количество групп. На выходе блока 7 установлен нулевой адрес. На выходах счетчика 4 и элемента ИЛИ-ИЕ Б устанавливаются нули. Триггеры 1 и 2. счетчики 3. 4 и 6 по сигналу 1 на счетном входе, а также блок 7 и-коммутатор 8 переключаются по спаду этого сигнала.

В первом цикле работы происходит запись и считывание О по всему массиву блока 17 памяти.

Под воздействием сигналов с входов 15 и 16 бпок 7 перебирает все адреса в блоке 17 памяти, первый адрес которого равен нулю. По окончании п-го такта по сигналу переноса блока 7 счетчик 4 переключается, переключается также триггер 1 в состояние 1. разрешающий занесе.ние начального адреса со-счетчика 6 в блок 7, открывающий элемент И 13 и задающий считывание .в

блоке 17. Работа блока 7 запрещена, разрешена работа первого и второго каналов мультиплексора 14. Следующие 2п тактов переборов адресов осуществляет счетчик 3. который перебирает последовательно, и на каждый выбранный адрес считывается информация из инверсного адреса. Переключение адресов осуществляет триггер 2 по сигналу, приходящему через элемент И 13 на управляющий вход мультиплексора 14.

Второй цикл: заг1ись всех кодовых комбинаций по каждой группе адресов и считывание по указанному алгоритму после записи каждой кодовой комбинации. При этом по группе адресов, которые формирует блок 7 суммирования, записывается кодовая комбинация 0...01, поступающая со счетчика 4.

По спаду сигнала переноса с блока 7 суммирования переключается в следующее состояние 0...010 счетчик 4, триггер 1 переключается в состояние 1, с инверсного выхода триггера 1 на второй управляющий вход мультиплексора 14 поступает сигнал О, а с прямого выхода триггера 1на второй вход элемента И 13 - сигнал 1.

В последующие такты происходят занесение начального адреса группы со счетчика

6по модулю К в блок 7 суммирования и считывание информации по всем адресам в порядке возрастания, но с инверсией каждого адреса. Затем происходит запись новой кодовой комбинации 0...010 по той же группе адресов, а по окончании записи триггер 1 вновь переключается,в состояние 1, и снова устанавливается режим Считывание информации по указанному алгоритму.

После записи кодовой комбинации 11... 11 счетчик 4 переключается в состоя ние 0...00 и на выходе элемента ИЛИ-НЕ 5 появляется 1. После записи кодовой комбинации 0...00 счетчик 4 переключается в состояние 0...01 и на выходе элемента ИЛИНЕ 5 устанавливается О. По заднему фронту сигнала 1 с элемента ИЛИ-НЕ 5 прибавляется единица в счетчик 6 по модулю К, и при считывании информации в блок

7суммирования заносится начальный адрес следующей группы.

Аналогично производятся запись всех кодовых комбинаций по другим группам и считывание информации по указанному алгоритму после записи каждой кодовой комбинации.

Выходное значение счетчика 6 по модулю К все время сравнивается с величиной К, подаваемой на информационные входы счетчика 6 с регистра 10. Когда значение на выходе счетчика 6 по модулю К становится равно К и появляется 1 в старшем разряде

счетчика 3, производится сброс счетчика б сигналами с инверсного входа 16 синхронизации. После этого в блок 7 суммирования по сигналам с входа 15 заносится начальный адрес первой группы, и второй цикл повторяется.

Счетчик б по модулю К (фиг.2) работает следующим образом.

Пбред началом работы делается установка в состояние О счетчика 18. При этом на выходе блока 19 сравнения и элемента И 20 устанавливается сигнал О, а на инверсном выходе триггера 21 - сигнал 1. По спаду сигнала 1, приходящему на счетный вход счетчика 18, его содержимое увеличивается на единицу. Когда содержимое счетчика 18 становится равным числу К, поступающему на вторые входы блока 19 сравнения, на выходе последнего устанавливается сигнал 1, поступающий на второй вход элемента И 20. После появления на первом входе элемента И 20 сигнала 1 по заднему фронту единичного сигнала, приходящего на синхровход триггера 21, он переключается в состояние 1 и на его инверсном выходе устанавливается сигнал О, который сбрасывает счетчик 18.

Блок 7 суммирования (фиг.З) работает следующим образом.

Перед началом работы делается сброс регистров 22 и 27, на вход управления занесением блока 7 суммирования подаётся сигнал О, на вход управления суммированием блока 7 суммирования - сигнал 1. Таким образом, выходы сумматора 23 через вторую группу элементов И 25, группу элементов ИЛИ 26 подключены к регистру 27, в котором находится нулевой адрес. По спаду инверсного сигнала обращения, поступающему на вход управления, параллельным занесением информации в регистр 22, информация с регистра 27 заносится в регистр 22. Содержимое регистра 22 и информация с выхода коммутатора 8 складываются в сумматоре 23, и по спаду сигнала обращения, поступающего на вход управления параллельным занесением информации, сумма заносится в регистр 27. Если не возникает сигнала переноса при сложении в сумматоре 23, то по спаду сигнала обращения на инверсном выходе триггера 29 устанавливается сигнал 1. Этот сигнал поступает на второй вход элемента И 30, на первый вход которого подается сигнал с входа управления суммированием блока 7 суммирования. При этом на выходе переноса блока 7 суммирования устанавливается сигнал Г.

Если при сложении в сумматоре 23 возникает сигнал переноса, то по спаду сигнала обращения триггер 29 устанавливается в состояние 1 и на его инверсном выходе устанавливается сигнал О. По спаду сигнала с инверсного выхода триггера 29 переключается в состояние 1 триггер 1. При этом на входе управления занесением блока 7 суммирования устанавливается 1, а на входе управления суммированием блока 7 суммирования - О. Таким образом, к информационным входам регистра 27 подключены выходы счетчика 6 по модулю К через первую группу элементов И 24 и группу элементов ИЛИ 26. По спаду сигнала обращения в регистр 27 заносится начальное значение, поданное на информационные входы первой группы блока 7 суммирования. Сигнал О с входа управления суммирования блока 7 суммирования блокирует элемент И 30, и на выходе переноса блока 7 суммирования появляется сигнал,О.

Коммутатор 8 (фиг.4) работает следующим образом,

Перед началом работы триггер 34 устанавливают в состояние О, а на его инверсном выходе устанавливается 1, При этом на выходе коммутатора 8 проходит информация, поступающая на его первые входы. По спаду единичного сигнала, поступающего на управляющий вход коммутатора 8, триггер 34 переключается в состояние 1, на его инверсном выходе устанавливается О, и информация, поступающая на вторые входы коммутатора 8, проходит на его выход. Элементы НЕ 12 позволяют изменить алгоритм выбора адреса при считывании, После каждого выбранного адреса считывается информация из адреса, .полученного инверсией всех разрядов данного. Инверсия всех разрядов каждого адреса ставит цепи выбора адреса в наиболее тяжелые условия, так как различные помехи, наводки,сбои связаны с количеством цепей, в которых одновременно происходит переключение, поэтому с появлением еще одного источника адресации (элементы НЕ 12) возрастает нздежность контроля засчет увеличения количества переключений адресных цепей испытываемого ОЗУ в едини цу времени при считывании по сравнению с другими групповыми тестами, рассматриваемыми в известном устройстве.

Счетный триггер 2 влияет на изменение формирования теста следующим образом. Сигнал со счетного триггера 2 через элемент И 13 поступает на первый управляющий вход мультиплексора 14. При переключении триггера 2 осуществляется переключение , первого и второго каналов мультиплексора 14, т.е. на проверяемое ОЗУ с мультиплексора 14 поступает прямой адрес(со счетчика 3)или инверсный адрес (с элементов НЕ 12).

Таким образом, сигнал со счетного триггера 2 осуществляет переключение адресов (прямого или инверсного) считывания проверяемого ОЗУ.

По спаду единичного сигнала с триггера 2 переключается счетчик 3, т.е. адрес, хранящийся в счетчике 3, увеличивается на единицу.

В регистр 9 (10) заносится приращение адреса, при суммировании которого с предыдущим адресом, хранящимся в блоке 7 суммирования образуется настоящий адрес, по которому записывается информация в проверяемое ОЗУ, В регистре 9 находится приращение адреса, необходимое для получения адресов в первом цикле работы устройства. Так как адреса в первом цикле перебираются последовательно, то в регистре.9 хранится единица.

В регистр 10 заносится приращение здреса, необходимое для получения адресов во втором цикле, когда идет запись по группе адресов, поэтому в регистр 10 заносится число К (количество групп). В каждую группу входят адреса, равные по модулю К.

В счетчике 6 по модулю К хранится начальный адрес группы, т.е. начальный адрес, к которому надо прибавлять числа К, 2К, ЗК и так далее, чтобы получить адреса данной группы. Сначала в счетчике б по модулю К находится О. После записи всех кодовых комбинаций по адресам одной группы содержимое счетчика б по модулю К увеличи-. вается на единицу.

Когда значение на выходе счетчика 6 по модулю К становится равно К и появляется 1, в старшем разряде счетчика 3 производится сброс счетчика 6. т,е. в счетчике 6 по

модулю,К хранится значение О, 1, 2 К-1,

0,1,2К-1 и т.д.

Формула изобретения - Устройство для формирования теста блока оперативной памяти, содержащее первый счетчик, выход старшего разряда которого соединен с входом счетчика по модулю К (где К - число групп тестовых наборов), с управляющим входом коммутатора и с первым входом элемента ИЛИ, выход которого подключен к счетному входу первого триггера, прямой выход которого является выходом устройства для подключения к входу управления считыванием тестируемого блока оперативной памяти, инверсный выход первого триггера является выходом устройства для подключения к входу управления записью тестируемого блока

оперативной памяти, второй счетчик, разрядные выходы которого подключены к группе входов элемента ИЛИ-НЕ и являются выходами устройства для подключения к

информационным входам тестируемой оперативной памяти, вход элемента ИЛИ-НЕ соединен с выходом коммутатора, первая и вторая группы информационных входов которого подключены к выходам первого и

второго регистров, группа выходов коммутатора подключена кинформационным входам первой группы блока суммирования, счетчик по модулю К, информационные входы которого соединены с выходами второго

регистра, синхровход счетчика по модулю К является инверсным входом синхронизации устройства и соединен с инверсным синхровходом блока суммирования,, счетный вход счетчика по модулю К подключен к выходу элемента ИЛИ-НЕ, а разрядные выходы счетчика по модулю К - к информационным входам второй группы блока суммирования, прямой синхровход которого является прямым входом синхронизации устройства, входы управления занесением и суммированием блока суммирования подключены соответственно к прямому и инверсному выходам первого триггера, выход переноса блока суммирования соединен со счетным входом второго счетчика и первым входом элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля путем увеличения количества переборов адресных

цепей при считывании, в yqтpoйcтвo введены элемент И, второй триггер, мультиплексор, группа элементов НЕ, причем счетный вход второго триггера соединен с прямым входом синхронизации устройства, прямой

выход второго триггера - с первым входом элемента И и счетным входом первого счетчика, разрядные выходы которого соединены с входами элементов НЕ группы .и первыми информационными входами мультиплексорг, выходы элементов НЕ группы с вторыми информационными входами мультиплексора, выходы блока суммирования подключены к третьим информационным входам мультиплексора, выходы

которого являются адресными выходами устройства для подключения к адресным.входам тестируемого блока памяти, прямой выход первого триггера соединен с вторым входом элемента И, выход которого подключей к первому управляющему входу мультиплексора, второй управляющий вход которого соединен с инверсным выходом первого триггера.

.з

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования теста оперативной памяти | 1985 |

|

SU1302322A1 |

| Устройство для адресации памяти на цилиндрических магнитных доменах | 1984 |

|

SU1185395A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Устройство адресации | 1987 |

|

SU1418712A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля ОЗУ. Цель изобретения - повышег ниё достоверности контроля за счет увеличения количества переборов адресных цепей при считывании. Устройство содержит триггеры 1, 2. счетчики 3, 4. злемент ИЛИ- НЕ 5, счетчик 6 по модулю К, блок 7 суммирования, коммутатор] 8, регистры 9, 10. злемент ИЛИ 11. группу злёментов НЕ 12. элемент И 13, мультиплексор 14, прямой и инверсный входы 15, 16 синхронизации, контролируемое ОЗУ 17. Информация считывается из адресов не подряд, последовательный перебор производится только для половины адресов, после каждого адреса считывается информация из адреса, полученного инверсией всех разрядов данного адреса. Изменение порядка усугубляет помехи, и инверсия всех разрядов каждого адреса ставит цепи выбора адреса в наиболее тяжелые условия. 5 ил.

Фиг.4

J J

М

«

1 «о 5

V)

«|

Ч

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| кл | |||

| Солесос | 1922 |

|

SU29A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| -ч | |||

Авторы

Даты

1992-02-23—Публикация

1990-01-02—Подача