: zv/a/

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказоустойчивых устройств управления и контро- ля управляющих и вычислительных комплексов, а также локальных микроконтроллеров АСУ ТП.

В связи с этим, целью изобретения является повышение надежности и достоверности контроля.

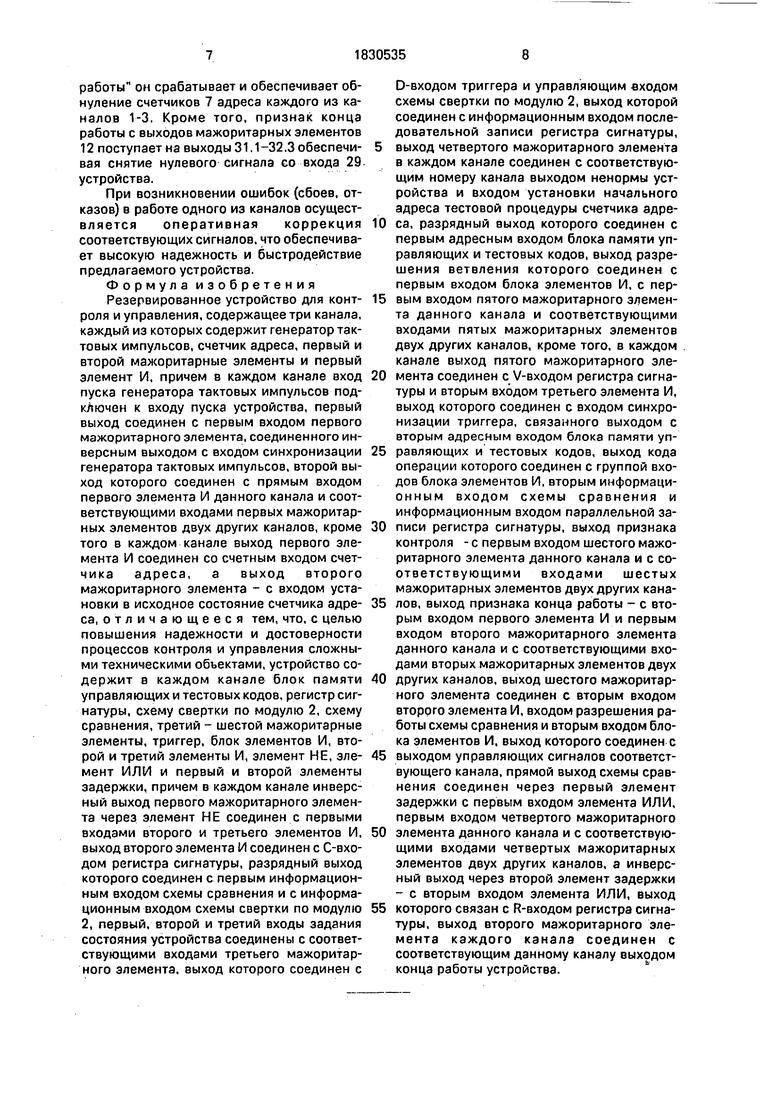

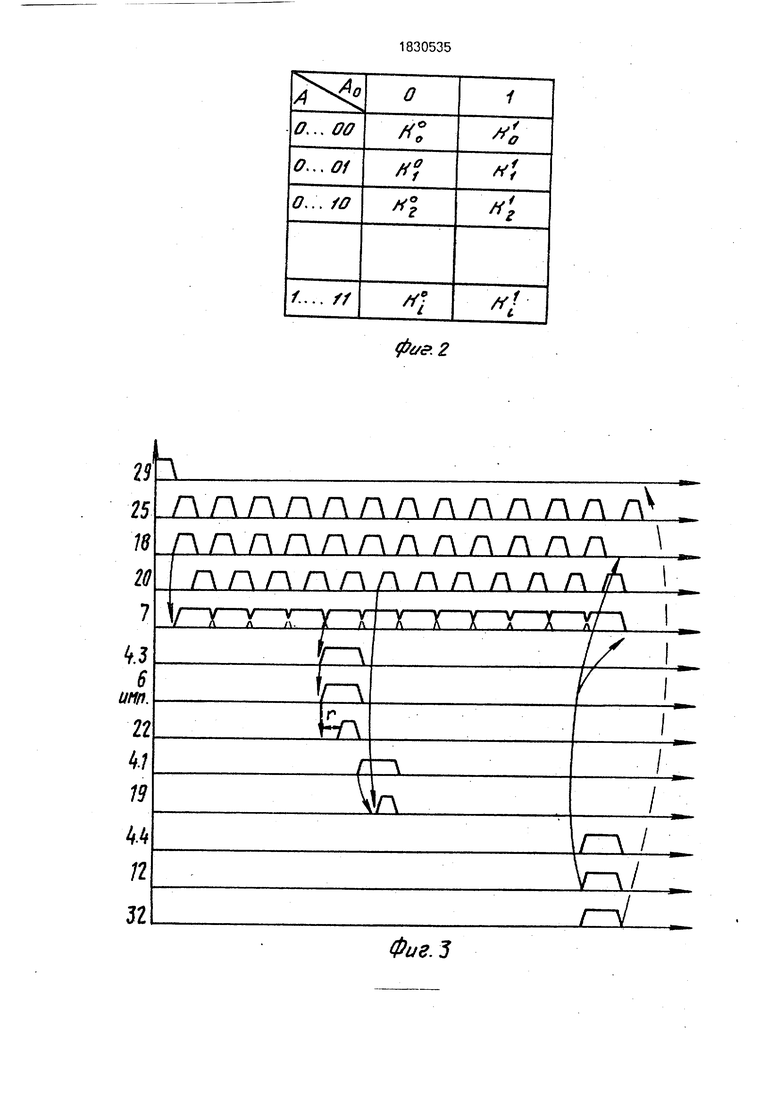

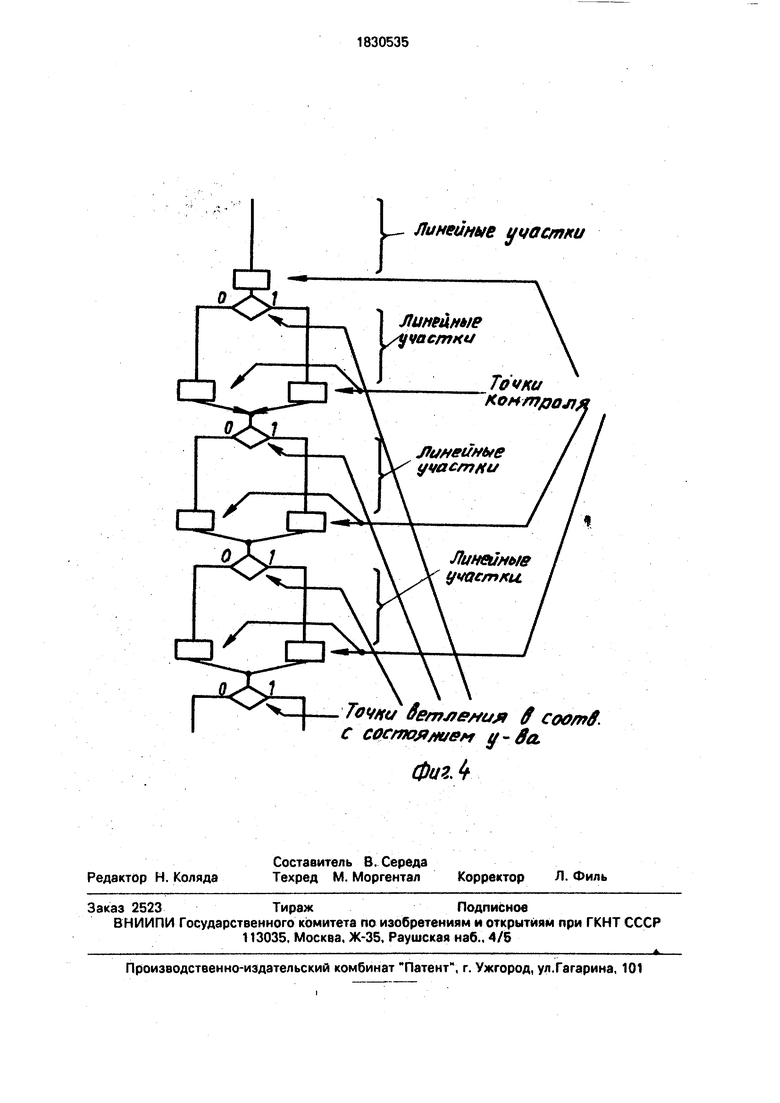

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - вариант упаковки кодов в блоке 4 памяти; на фиг. 3 - временная диаграмма работы устройства; на фиг. 4 - общий вид программы работы устройства.

Устройство (фиг. содержит первый 1. второй 2, третий 3 идентичные каналы, каждый канал содержит блок 4 памяти управляющих и тестовых кодов, регистр 5 сигнатуры, схему б сравнения, счетчик 7 адреса, схему 8 свертки, по модулю 2, первый 9, третий 10, пятый 11, второй 12, четвертый 13, шестой 14 мажоритарные элементы, триггер 15, блок 16 элементов И, второй 17, первый 18 и третий 19 элементы И, элемент НЕ 20, элемент ИЛИ 21, второй 22 и первый 23 элементы задержки. Кроме того, в каждом канале есть генератор синхроимпульсов, состоящий из элемента ИЛИ-НЕ 24, кварцевого резонатора 25, первого 26 и второго 27 резисторов. На фиг. 1 также показаны: первый 28.1, второй 28.2, третий 28.3 входы состояний устройства; - вход 29 пуска; - первый 30.1, второй 30.2 и третий 30.3 выходы управляющих сигналов; первый 31.1, второй 31.2 и третий 31.3 выходы ненормы; - первый 32.1, второй 32.2 и третий 32.3 выходы конца работы.

Устройство содержит три идентичных канала 1-3, предназначенных для формирования требуемых последовательностей управляющих сигналов или тестов.

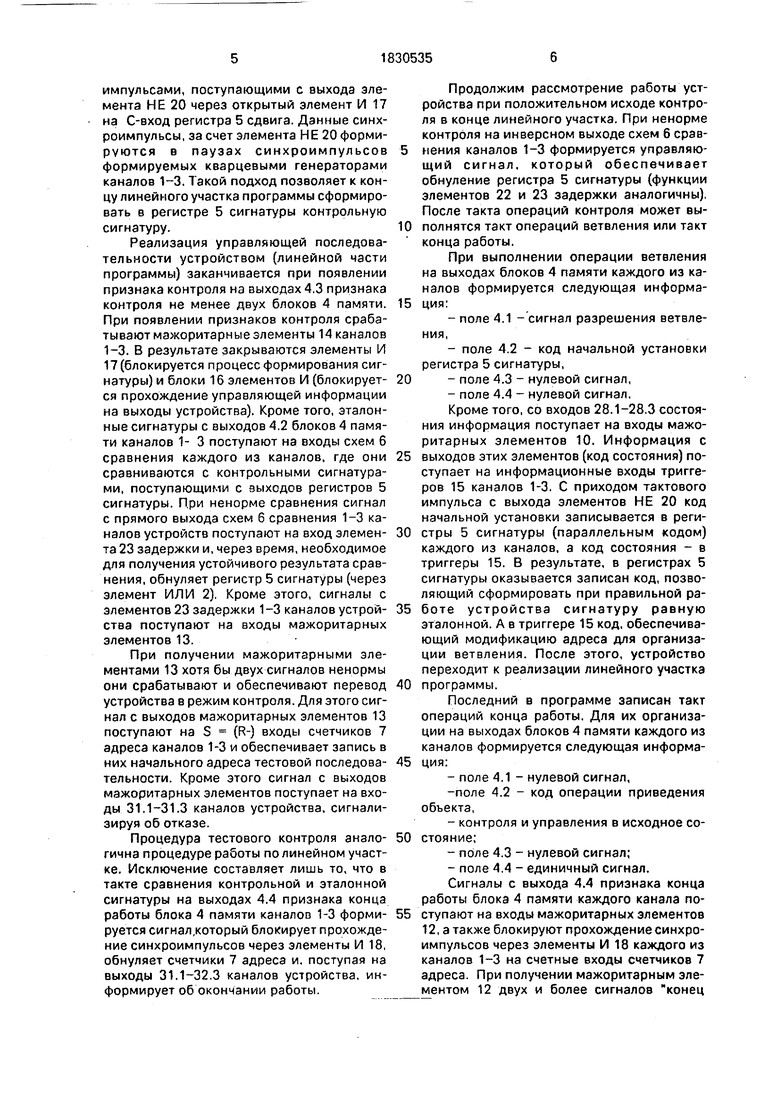

Блок 4 памяти предназначен для хранения кодов управляющих сигналов и кодов тестовых последовательностей. Вариант упаковки кодов в блоке 4 памяти представлен на фиг. 2.

Блок 4 памяти имеет четыре выхода: выход 4.1 разрешения ветвления и начальной установки регистра 5 сигнатуры; - выход 4.2 кода операций; - выход 4.3 признака контроля; - выход 4.4 признака конца работы. При единичном сигнале на выходе 4.1 на выходе 4.2 формируется код начальной установки регистра 5 сигнатуры, при единичном сигнале на выходе 4.4 - код эталонной сигнатуры, во всех остальных слунаях - код операции (код управления работой объектом).

Регистр 5 сигнатуры совместно со схемой 8 свертки по модулю 2 образуют средства формирования сигнатуры. Сигнатура формируется из последовательности сигналов о состоянии объекта, контроля и управления, поступающих на вход 28 состояния устройства.

Схема 6 сравнения предназначена для сравнения контрольной сигнатуры, сформи0 рованной средствами формирования сигнатуры и эталонной сигнатуры (записанной в блок 4 памяти).

Счетчик 7 адреса предназначен для формирования адреса очередной микроко5 манды.

Мажоритарные элементы 9-14 предназначены для мажоритирования ряда сигна- ловлоступающих с одноименных элементов 1-3 блоков устройства.

0 Триггер 15 предназначен для формирования одного разряда адреса при ветвлении в соответствии с признаком состояния.

Элементы 24, 25, 26, 27 образуют кварцевый генератор тактовых импульсов, кото5 рый формирует импульсы, управляющие работой счетчика 7 адреса и синхронизирует работу устройства в целом.

Перед началом работы в счетчики 7 каналов 1-3 по цепям начальной установки

0 заносится код, соответствующий требуемой последовательности управляющих воздействий, а регистр 5 сигнатуры и триггер 15 обнуляются (цепи установки в исходное состояние условно не показаны).

5 Работа устройства начинается с поступления нулевого сигнала на входы элементов ИЛИ-НЕ 24 каналов 1-3 через вход 29 пуска устройства (фиг. 3). По этому сигналу квар цевые генераторы каналов 1-3 начинают

0 формировать тактовые импульсы, которые через элементы И 18 последовательно поступают на счетные входы (+1) счетчиков 7 адреса каналов 1-3. Формируемые счетчиками адреса поступают на входы блоков 4

5 памяти, на выходах которых формируются требуемые последовательности управляющих сигналов. Управляющие сигналы с выхода 4.2 кода операции блоков 4 памяти через блоки 16 элементов И поступают на

0 выходы 30.1 - 30.3 управляющих сигналов устройства. В таком порядке формируются управляющие сигналы на линейном участке программы. В процессе реализации линейного участка программы на входы мажори5 тарных элементов 10 каналов 1-3 поступают коды состояний объекта. Коды состояний объекта поступают на вход схемы 8 свертки по модулю 2, где они складываются по модулю 2 с кодом, записанным в регистре 5

сигнатуры. Запись осуществляется синхроимпульсами, поступающими с выхода элемента НЕ 20 через открытый элемент И 17 на С-вход регистра 5 сдвига. Данные синхроимпульсы, за счет элемента НЕ 20 формируются в паузах синхроимпульсов формируемых кварцевыми генераторами каналов 1-3. Такой подход позволяет к концу линейного участка программы сформировать в регистре 5 сигнатуры контрольную сигнатуру.

Реализация управляющей последовательности устройством (линейной части программы) заканчивается при появлении признака контроля на выходах 4.3 признака контроля не менее двух блоков 4 памяти. При появлении признаков контроля срабатывают мажоритарные элементы 14 каналов 1-3. В результате закрываются элементы И 17 (блокируется процесс формирования сигнатуры) и блоки 16 элементов И (блокирует- ся прохождение управляющей информации на выходы устройства). Кроме того, эталонные сигнатуры с выходов 4.2 блоков 4 памяти каналов 1- 3 поступают на входы схем 6 сравнения каждого из каналов, где они сравниваются с контрольными сигнатурами, поступающими с выходов регистров 5 сигнатуры. При ненорме сравнения сигнал с прямого выхода схем 6 сравнения 1-3 каналов устройств поступают на вход элемен- та 23 задержки и, через время, необходимое для получения устойчивого результата сравнения, обнуляет регистр 5 сигнатуры (через элемент ИЛИ 2). Кроме этого, сигналы с элементов 23 задержки 1-3 каналов устрой- ства поступают на входы мажоритарных элементов 13.При получении мажоритарными элементами 13 хотя бы двух сигналов ненормы они срабатывают и обеспечивают перевод устройства в режим контроля. Для этого сигнал с выходов мажоритарных элементов 13 поступают на S (R-) входы счетчиков 7 адреса каналов 1-3 и обеспечивает запись в них начального адреса тестовой последова- тельности. Кроме этого сигнал с выходов мажоритарных элементов поступает на входы 31.1-31.3 каналов устройства, сигнализируя об отказе.

Процедура тестового контроля знало- гична процедуре работы по линейном участке. Исключение составляет лишь то, что в такте сравнения контрольной и эталонной сигнатуры на выходах 4.4 признака конца работы блока 4 памяти каналов 1-3 форми- руется сигнал .который блокирует прохождение синхроимпульсов через элементы И 18, обнуляет счетчики 7 адреса и, поступая на выходы 31.1-32.3 каналов устройства, информирует об окончании работы.

Продолжим рассмотрение работы устройства при положительном исходе контроля в конце линейного участка. При ненорме контроля на инверсном выходе схем б сравнения каналов 1-3 формируется управляющий сигнал, который обеспечивает обнуление регистра 5 сигнатуры (функции элементов 22 и 23 задержки аналогичны). После такта операций контроля может выполнятся такт операций ветвления или такт конца работы.

При выполнении операции ветвления на выходах блоков 4 памяти каждого из каналов формируется следующая информация:

-поле 4.1 -сигнал разрешения ветвления,

-поле 4.2 - код начальной установки регистра 5 сигнатуры,

-поле 4.3 - нулевой сигнал,

-поле 4.4 - нулевой сигнал.

Кроме того, со входов 28.1-28.3 состояния информация поступает на входы мажоритарных элементов 10. Информация с выходов этих элементов (код состояния) поступает на информационные входы триггеров 15 каналов 1-3. С приходом тактового импульса с выхода элементов НЕ 20 код начальной установки записывается в регистры 5 сигнатуры (параллельным кодом) каждого из каналов, а код состояния - в триггеры 15. В результате, в регистрах 5 сигнатуры оказывается записан код, позволяющий сформировать при правильной работе устройства сигнатуру равную эталонной. А в триггере 15 код, обеспечивающий модификацию адреса для организации ветвления. После этого, устройство переходит к реализации линейного участка программы.

Последний в программе записан такт операций конца работы. Для их организации на выходах блоков 4 памяти каждого из каналов формируется следующая информация:

-поле 4.1 - нулевой сигнал,

-поле 4.2 - код операции приведения объекта,

-контроля и управления в исходное состояние;

-поле 4.3 - нулевой сигнал;

-поле 4.4 - единичный сигнал. Сигналы с выхода 4.4 признака конца

работы блока 4 памяти каждого канала поступают на входы мажоритарных элементов 12, а также блокируют прохождение синхроимпульсов через элементы И 18 каждого из каналов 1-3 на счетные входы счетчиков 7 адреса. При получении мажоритарным элементом 12 двух и более сигналов конец

работы он срабатывает и обеспечивает обнуление счетчиков 7 адреса каждого из каналов 1-3. Кроме того, признак конца работы с выходов мажоритарных элементов 12 поступает на выходы 31.1-32.3 обеспечивая снятие нулевого сигнала со входа 29 устройства.

При возникновении ошибок (сбоев, отказов) в работе одного из каналов осуществляется оперативная коррекция соответствующих сигналов, что обеспечивает высокую надежность и быстродействие предлагаемого устройства.

Формула изобретения Резервированное устройство для контроля и управления, содержащее три канала, каждый из которых содержит генератор тактовых импульсов, счетчик адреса, первый и второй мажоритарные элементы и первый элемент И, причем в каждом канале вход пуска генератора тактовых импульсов подключен к входу пуска устройства, первый выход соединен с первым входом первого мажоритарного элемента, соединенного инверсным выходом с входом синхронизации генератора тактовых импульсов, второй выход которого соединен с прямым входом первого элемента И данного канала и соответствующими входами первых мажоритарных элементов двух других каналов, кроме того в каждом канале выход первого элемента И соединен со счетным входом счетчика адреса, а выход второго мажоритарного элемента - с входом установки в исходное состояние счетчика адреса, отличающееся тем, что, с целью повышения надежности и достоверности процессов контроля и управления сложными техническими объектами, устройство содержит в каждом канале блок памяти управляющих и тестовых кодов, регистр сигнатуры, схему свертки по модулю 2, схему сравнения, третий - шестой мажоритарные элементы, триггер, блок элементов И, второй и третий элементы И, элемент НЕ, элемент ИЛИ и первый и второй элементы задержки, причем в каждом канале инверсный выход первого мажоритарного элемента через элемент НЕ соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с С-вхо- дом регистра сигнатуры, разрядный выход которого соединен с первым информационным входом схемы сравнения и с информационным входом схемы свертки по модулю 2, первый, второй и третий входы задания состояния устройства соединены с соответствующими входами третьего мажоритарного элемента, выход которого соединен с

D-входом триггера и управляющим входом схемы свертки по модулю 2, выход которой соединен с информационным входом последовательной записи регистра сигнатуры,

выход четвертого мажоритарного элемента в каждом канале соединен с соответствующим номеру канала выходом ненормы устройства и входом установки начального адреса тестовой процедуры счетчика адреса, разрядный выход которого соединен с первым адресным входом блока памяти управляющих и тестовых кодов, выход разрешения ветвления которого соединен с первым входом блока элементов И, с первым входом пятого мажоритарного элемента данного канала и соответствующими входами пятых мажоритарных элементов двух других каналов, кроме того, в каждом канале выход пятого мажоритарного элемента соединен с V-входом регистра сигнатуры и вторым входом третьего элемента И, выход которого соединен с входом синхронизации триггера, связанного выходом с вторым адресным входом блока памяти управляющих и тестовых кодов, выход кода операции которого соединен с группой входов блока элементов И, вторым информаци- онным входом схемы сравнения и информационным входом параллельной записи регистра сигнатуры, выход признака контроля - с первым входом шестого мажоритарного элемента данного канала и с соответствующими входами шестых мажоритарных элементов двух других каналов, выход признака конца работы - с вторым входом первого элемента И и первым входом второго мажоритарного элемента данного канала и с соответствующими входами вторых мажоритарных элементов двух

других каналов, выход шестого мажоритарного элемента соединен с вторым входом второго элемента И, входом разрешения работы схемы сравнения и вторым входом блока элементов И, выход которого соединен с

выходом управляющих сигналов соответствующего канала, прямой выход схемы сравнения соединен через первый элемент задержки с первым входом элемента ИЛИ, первым входом четвертого мажоритарного

элемента данного канала и с соответствующими входами четвертых мажоритарных элементов двух других каналов, а инверсный выход через второй элемент задержки - с вторым входом элемента ИЛИ, выход

которого связан с R-входом регистра сигнатуры, выход второго мажоритарного элемента каждого канала соединен с соответствующим данному каналу выходом конца работы устройства.

Ф&&.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления диагностированием и восстановлением цифровых систем | 1984 |

|

SU1624456A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Дублированная вычислительная система | 1990 |

|

SU1783528A1 |

| Устройство для контроля резервированной системы | 1984 |

|

SU1256028A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

Использование: в сложных технических объектах для повышения надежности и достоверности процессов их контроля и управления. Сущность изобретения: устройство содержит 3 канала 1-3, каждый из которых содержит 1 блок памяти управляющих и те- стовыхкодов4,1 регистр сигнатуры 5,1 схему сравнения б, 1 счетчик адреса 7, 1 схему свертки по модулю 2 8, 6 мажоритарных элементов 9 - 14, 1 триггер 15, 1 блок элементов И 16, 3 элемента И 17 - 19, элемент НЕ 20, 1 элемент ИЛ И 21,2 элемента задержки 22, 23, 1 генератор синхроимпульсов, состоящий из 1 элемента ИЛИ-НЕ 24, 1 кварцевого резонатора 25, 2 резисторов 26, 27. 4 ил.

Фив.

Точки бетлеяия 0 соетб. с состояние ц у - Лг

Фиг. 4.

Линейные участки

| Мажоритарно-резервированное устройство | 1982 |

|

SU1042217A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления с коррекцией ошибок | 1985 |

|

SU1368881A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-07-30—Публикация

1991-02-15—Подача