Изобретение относится к вычислительной технике и может быть использовано при построении специализированных устройств для упорядоченного хранения и выдачи информации по безадресному принципу.

Цель изобретения повышение быстродействия устройства.

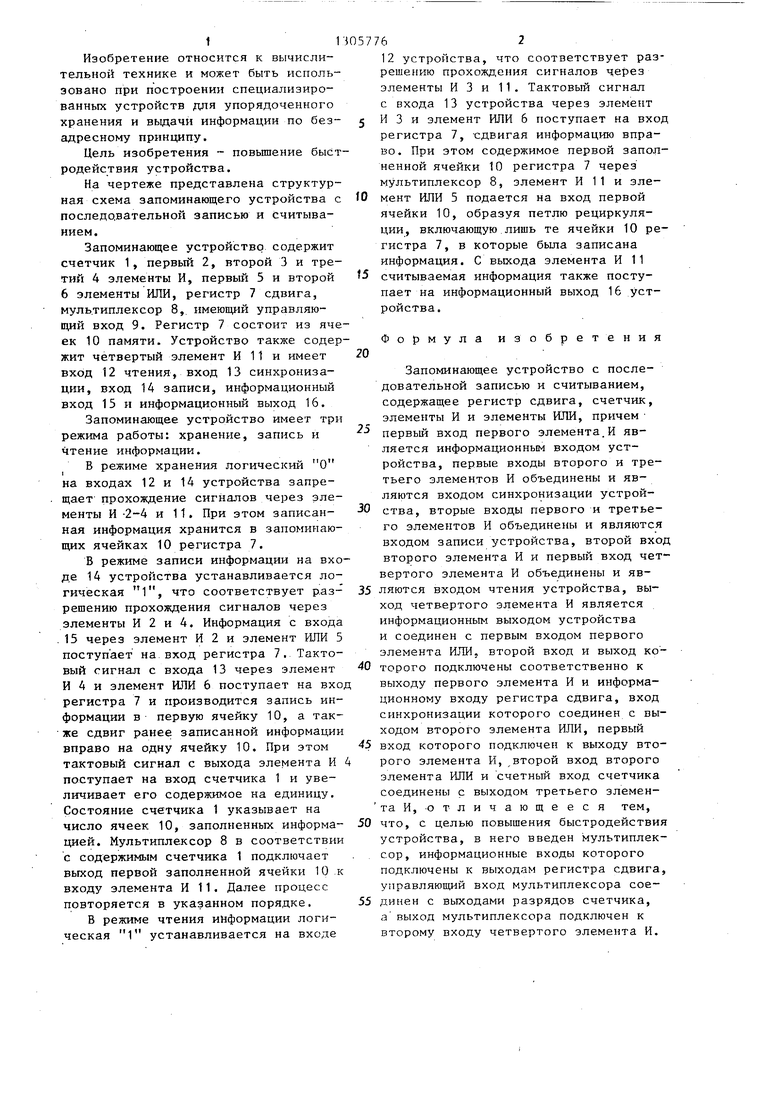

На чертеже представлена структурная схема запоминающего устройства с последовательной записью и считыванием.

Запоминающее устройство содержит счетчик 1, первьш 2, второй 3 и третий 4 элементы И, первый 5 и второй 6 элементы ИЛИ, регистр 7 сдвига, мультиплексор 8, имеющий управляющий вход 9. Регистр 7 состоит из ячеек 10 памяти. Устройство также содержит четвертый элемент И 11 и имеет вход 12 чтения, вход 13 синхронизации, вход 14 записи, информационный вход 15 и информационный выход 16.

Запоминающее устройство имеет три режима работы: хранение, запись и чтение информации.

В режиме хранения логический О на входах 12 и 14 устройства запре- щает прохождение сигналов через элементы И -2-4 и It. При этом записанная информация хранится в запоминающих ячейках 10 регистра 7.

В режиме записи информации на входе 14 устройства устанавливается логическая 1, что соответствует разрешению прохождения сигналов через элементы И 2 и 4. Информация с входа 15 через элемент И 2 и элемент ИЛИ 5 поступает на вход регистра 7. Тактовый сигнал с входа 13 через элемент И 4 и элемент ИЛИ 6 поступает на вход регистра 7 и производится запись информации в первую ячейку 10, а так- же сдвиг ранее записанной информации вправо на одну ячейку 10. При этом тактовый сигнал с выхода элемента И 4 поступает на вход счетчика 1 и увеличивает его содержимое на единицу. Состояние счетчика 1 указывает на число ячеек 10, заполненных информацией. Мультиплексор 8 в соответствии с содержимым счетчика 1 подключает выход первой заполненной ячейки 10 к входу элемента И 11. Далее процесс повторяется в указанном порядке.

В режиме чтения информации логическая 1 устанавливается на входе

12 устройства, что соответствует разрешению прохожд,ения сигналов через элементы И 3 и 11. Тактовый сигнал с входа 13 устройства через элемент

И 3 и элемент ИЛИ 6 поступает на вход регистра 7, х;двигая информацию вправо. При этом содержимое первой заполненной ячейки 10 регистра 7 через мультиплексор 8, элемент И 11 и элемент ИЛИ 5 подается на вход первой ячейки 10, образуя петлю рециркуляции, включающую лишь те ячейки 10 регистра 7, в которые бьша записана информация. С выхода элемента И 11

считываемая информация также поступает на информационный выход 16 устройства.

Формула изобретения

Запоминающее устройство с последовательной записью и считыванием, содержащее регистр сдвига, счетчик, элементы И и элементы ИЛИ, причем первый вход первого элемента.И является информационным входом устройства, первые входы второго и третьего элементов И объединены и являются входом синхронизации устрой- ства, вторые входы первого и третьего элементов И объединены и являются входом записи устройства, второй вход второго элемента И и первый вход четвертого элемента И объединены и яв- ляются входом чтения устройства, выход четвертого элемента И является информационным выходом устройства и соединен с первым входом первого элемента ИЛИ. второй вход и выход ко- торого подключены соответственно к выходу первого элемента И и информационному входу регистра сдвига, вход синхронизации которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к выходу второго элемента И, второй вход второго элемента Ш1И и счетный вход счетчика соединены с выходом третьего элемен- та И, -о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введен мультиплексор, информационные входы которого подключены к выходам регистра сдвига, управляющий вход мультиплексора сое- динен с выходами разрядов счетчика, а выход мультиплексора подключен к второму входу четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1575237A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Запоминающее устройство | 1989 |

|

SU1711229A1 |

| Запоминающее устройство | 1987 |

|

SU1520592A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Запоминающее устройство | 1987 |

|

SU1472910A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1532965A1 |

| Фотоэлектрическое считывающее устройство | 1988 |

|

SU1674181A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

Изобретение относится к вычислительной технике-и может быть ис- , пользовано при построении специализированных устройств для упорядоченного хранения и выдачи информации по безадресному принципу. Цель изобретения - повышение быстродействия устройства. Устройство содержит счетчик 1, элементы И 2-4, элементы ИЛИ 5 и 6, регистр 7 сдвига, мультиплексор 8 и элемент И 11. Регистр 7 состоит из ячеек 10 памяти. В устройстве при вводе информации автоматически устанавливается петля рециркуляции, включающая лишь заполненные ячейки 10 памяти, что сокращает время выборки запоминающего устройства и дает возможность регенерации считываемой информации. 1 ил. (Л со о сд к 05

| Г | 0 |

|

SU377887A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3992699, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1987-04-23—Публикация

1985-06-18—Подача