4Ь 1 ю

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения модулей вычислительной системы с общей шиной | 1984 |

|

SU1179357A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1705832A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1990 |

|

SU1784985A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1515167A1 |

| Процессор для мультипроцессорной системы | 1989 |

|

SU1688252A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Изобретение относится к вычислительной технике и может быть использовано для отладки программ и диагностики аппаратуры. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения синхронной безадресной записи состояний магистрали. Устройство работает в режиме адресного обмена и режиме безадресной записи состояний магистрали. Режим адресного обмена - стандартный режим работы запоминающего устройства с обменом данными по интерфейсу.Адресный обмен производится с помощью блока 1 памяти, регистра 2 адреса и блока 5 управления адресным обменом. В режиме безадресной записи устройство выполняет в полном объеме функции адресного обмена и,дополнительно,записывает в заданную область блока 1 памяти последовательность состояний магистрали в моменты истинности передаваемых адресов и данных.Адрес для блока 1 памяти наряду с регистром 2 формируется и на счетчике 3, а триггер 8, блок 7 фиксации данных и элемент И-НЕ 9, элемент 10 сопряжения и элемент 11 задержки обеспечивают сохранение информации в магистрали на время записи. Управляющие сигналы в режиме безадресной записи формируют блок 5 управления адресным обменом и блок 6 управления безадресной записью. Выделенная для записи состояний магистрали область памяти доступна чтению в адресном режиме, что обеспечивает возможность программными средствами анализировать по записанной магистрали ход программы,ее промежуточные и конечные результаты. 4 ил.

блок 7 фиксации данных, элемент И-НЕ 9, элемент 10 сопряжения и элемент 11 задержки обеспечивают сохранение информации в магистрали на время записи. Управляющие сигналы в режиме безадресной записи формируют блок 5 управления адресным обменом и блок 6 управления безадресной записью.

1

Изобретение относится к вычислительной технике и может быть использовано для отладки программ и диагностики аппаратуры в вычислительных системах общего назначения и специ- ализированных отладочных устройствах

Цель изобретения - расширение функциональных возможностей за счет обеспечения синхронной безадресной записи состояний магистрали.

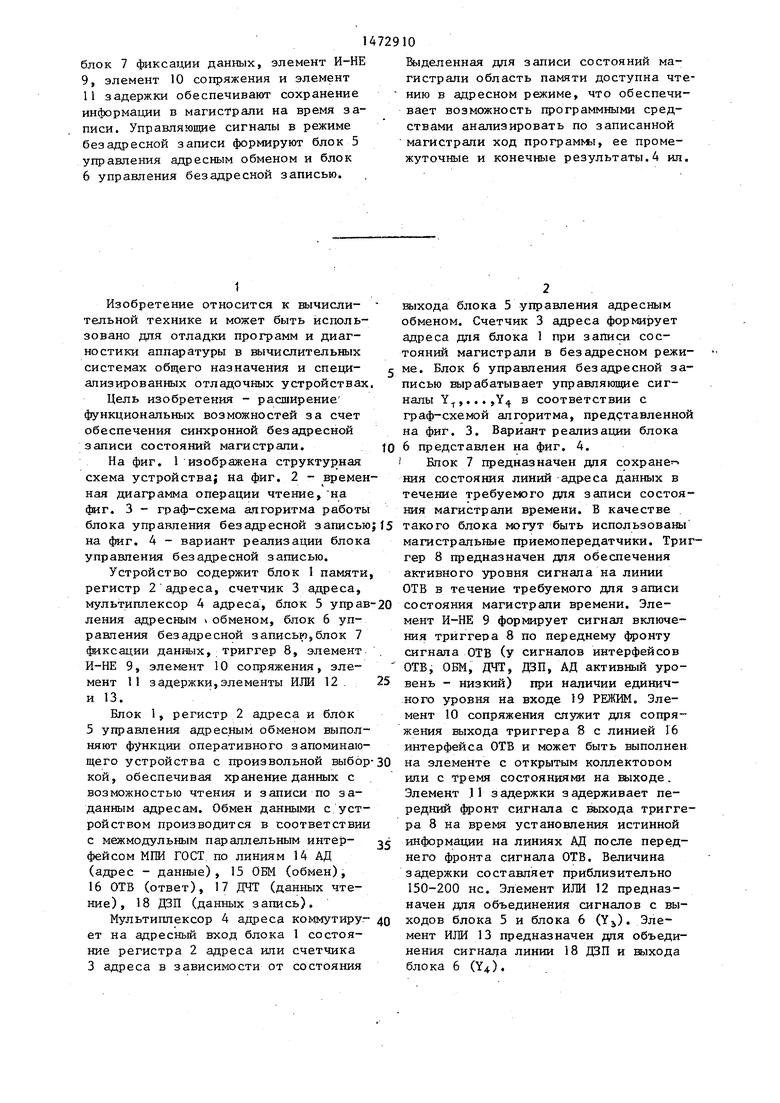

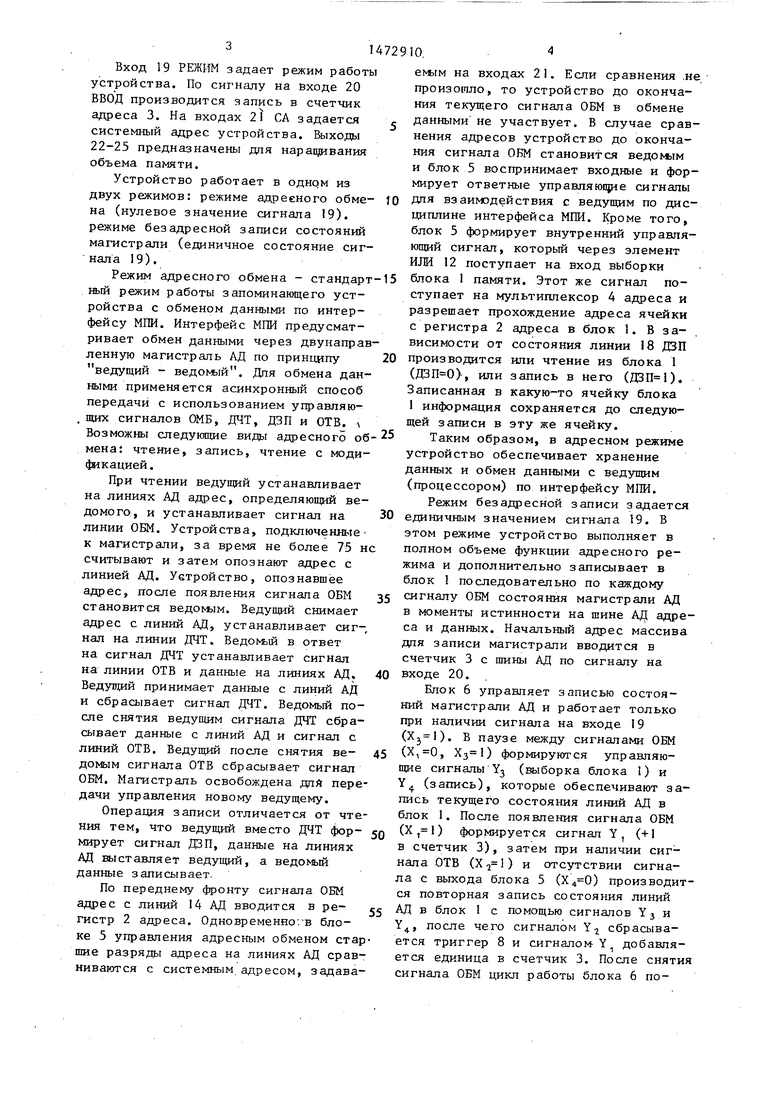

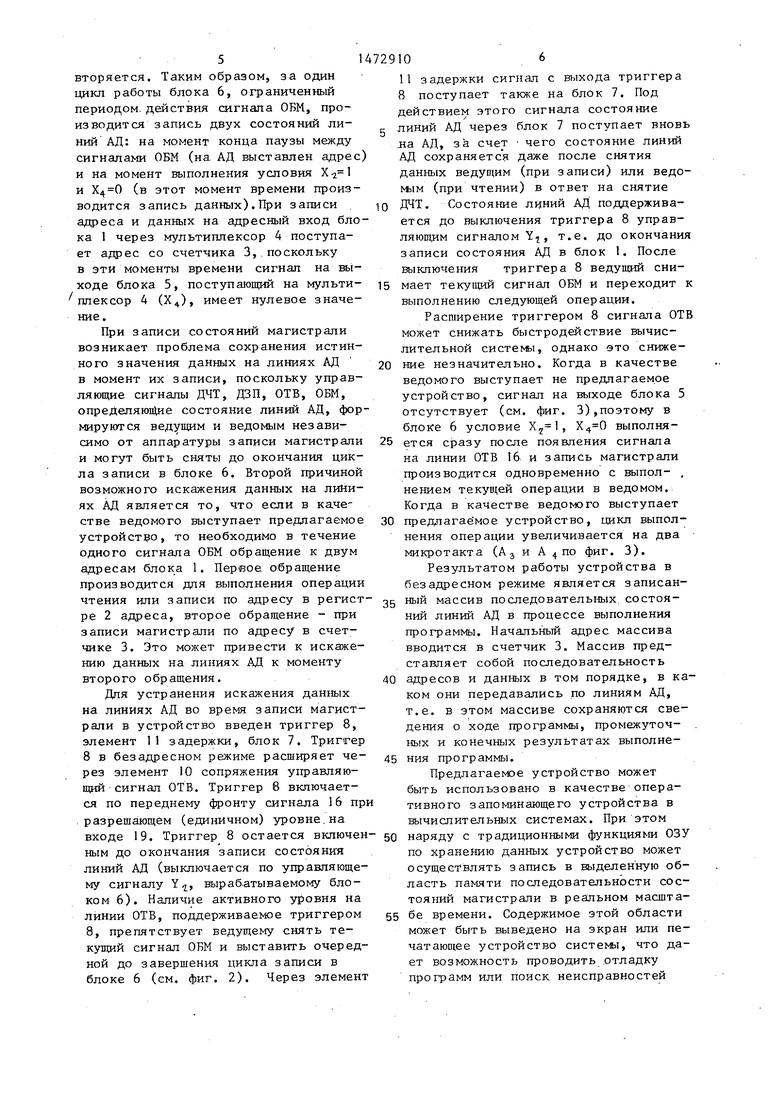

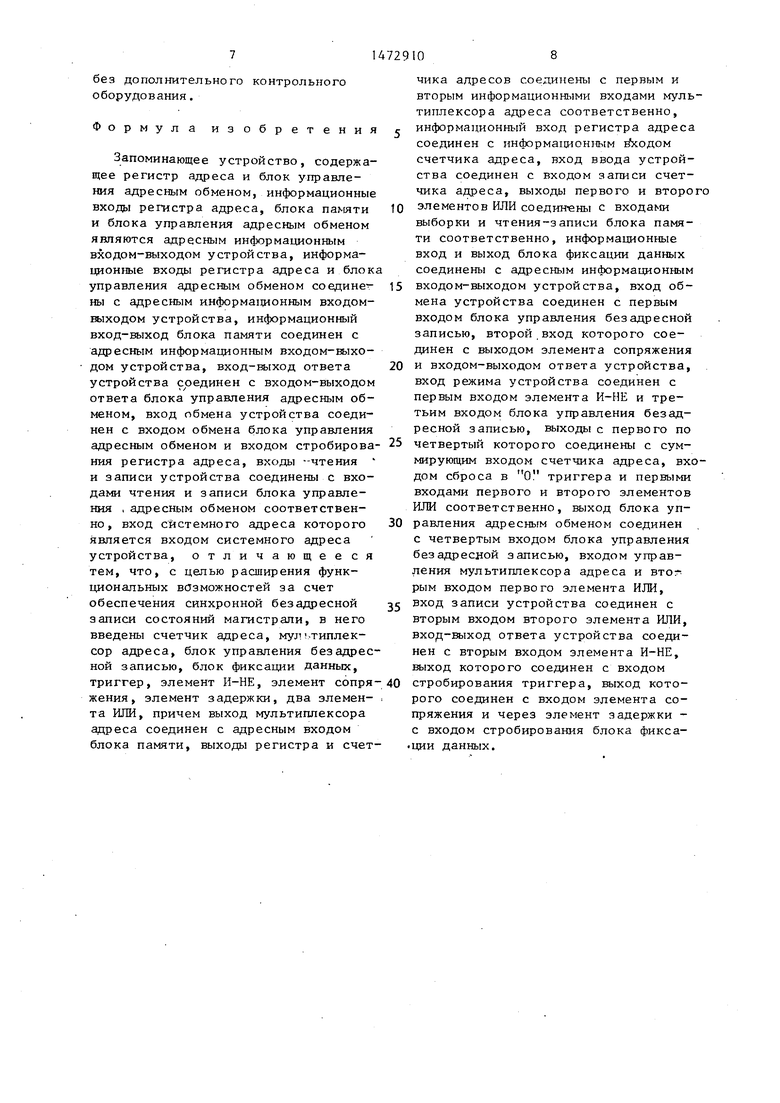

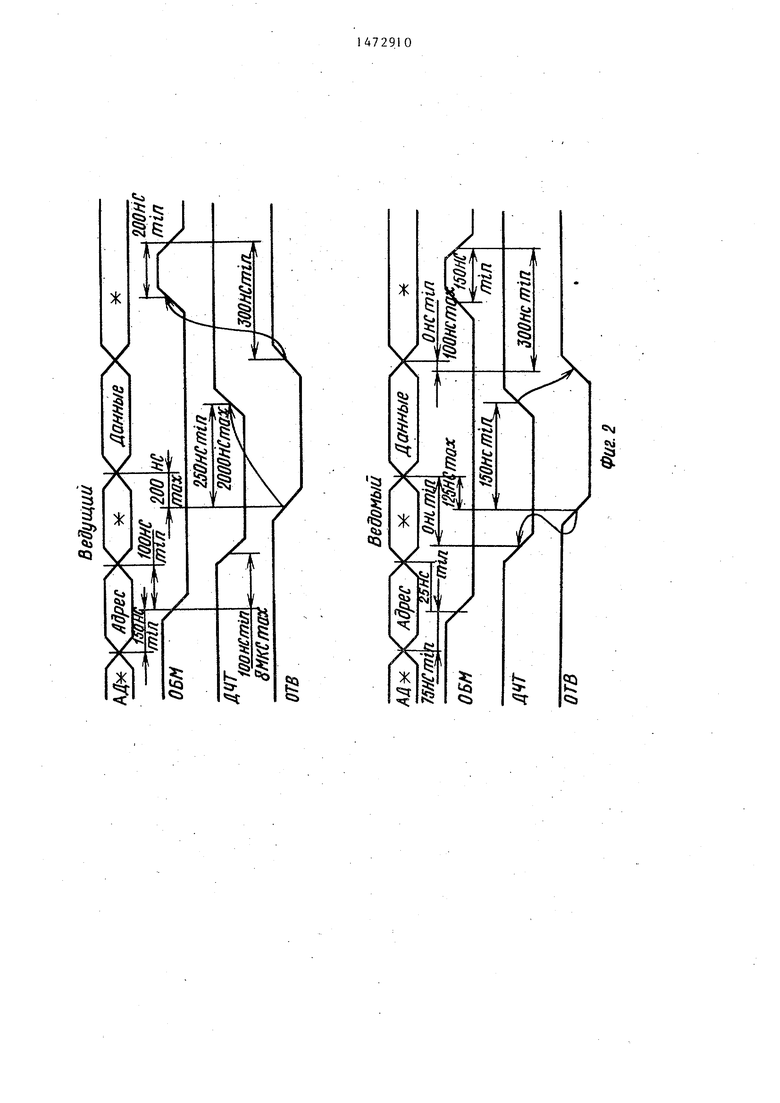

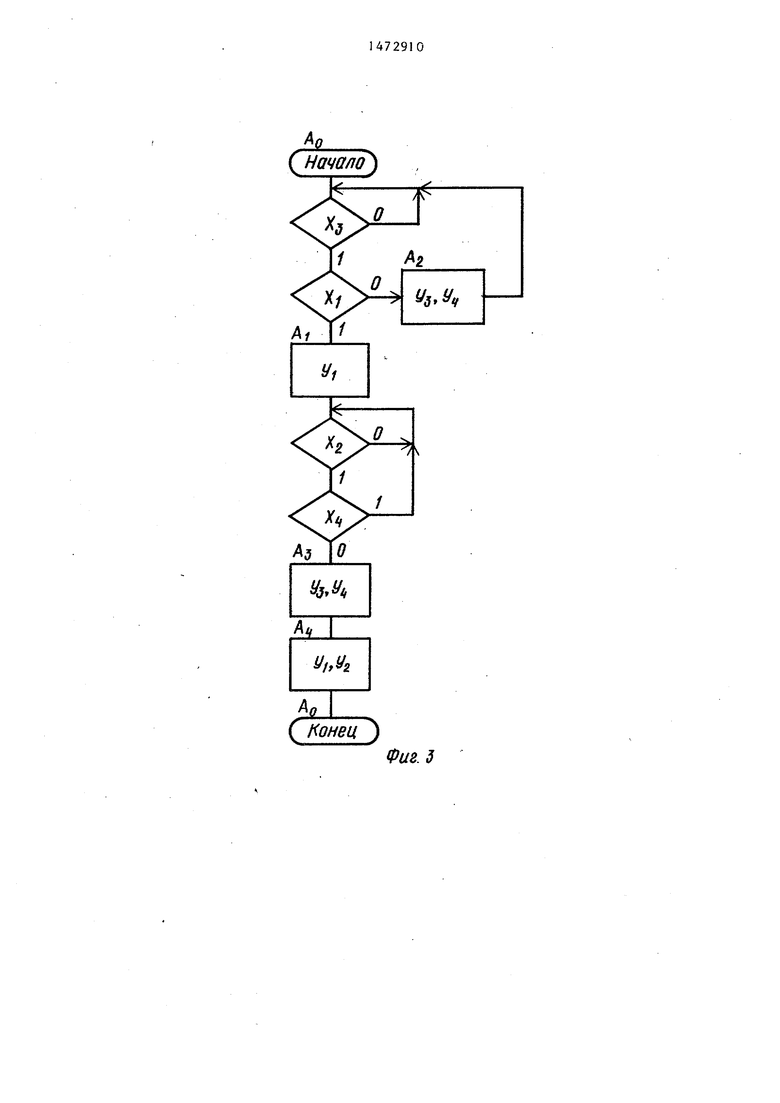

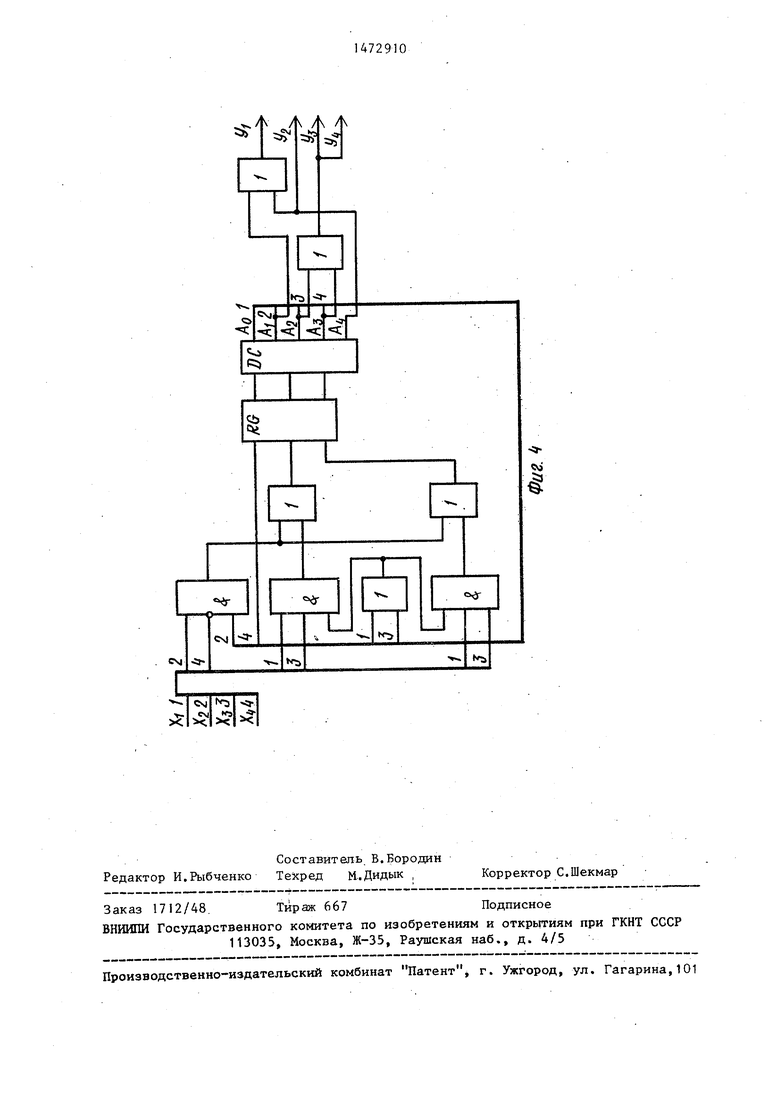

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временная диаграмма операции чтение, на фиг. 3 - граф-схема алгоритма работы блока управления безадресной записью на фиг. 4 - вариант реализации блока управления безадресной записью.

Устройство содержит блок 1 памяти, регистр 2 адреса, счетчик 3 адреса, мультиплексор 4 адреса, блок 5 управ ления адресным обменом, блок 6 управления безадресной записью,блок 7 фиксации данных, триггер 8, элемент И-НЕ 9, элемент 10 сопряжения, элемент 11 задержки,элементы ИЛИ 12 и 13.

Блок 1, регистр 2 адреса и блок 5 управления адресным обменом выполняют функции оперативного запоминающего устройства с произвольной выбор кой, обеспечивая хранение данных с возможностью чтения и записи по заданным адресам. Обмен данными с устройством производится в соответствии с межмодульным параллельным интерфейсом МПИ ГОСТ по линиям 14 АД (адрес - данные), 15 ОБМ (обмен), 16 ОТВ (ответ), 17 ДЧТ (данных чтение), 18 ДЗП (данных запись).

Мультиплексор 4 адреса коммутиру- ет на адресный вход блока 1 состояние регистра 2 адреса или счетчика 3 адреса в зависимости от состояния

Выделенная для записи состояний магистрали область памяти доступна чтению в адресном режиме, что обеспечивает возможность программными средствами анализировать по записанной магистрали ход программы, ее промежуточные и конечные результаты.4 ил.

с

JQ

15

20 5

0

0

5

выхода блока 5 управления адресным обменом. Счетчик 3 адреса формирует адреса для блока 1 при записи состояний магистрали в безадресном режиме. Блок 6 управления безадресной записью вырабатывает управляющие сигналы Y.,,...,Y4 в соответствии с граф-схемой алгоритма, представленной на фиг. 3. Вариант реализации блока 6 представлен на фиг. 4. Блок 7 предназначен для сохране-- ния состояния линий адреса данных в течение требуемого для записи состояния магистрали времени. В качестве такого блока могут быть использованы магистральные приемопередатчики. Триггер 8 предназначен для обеспечения активного уровня сигнала на линии ОТВ в течение требуемого для записи состояния магистрали времени. Элемент И-НЕ 9 формирует сигнал включения триггера 8 по переднему фронту сигнала ОТВ (у сигналов интерфейсов ОТВ, ОБМ, ДЧТ, ДЗП, АД активный уровень - низкий) при наличии единичного уровня на входе 19 РЕЖИМ. Элемент 10 сопряжения служит для сопряжения выхода триггера 8 с линией 16 интерфейса ОТВ и может быть выполнен на элементе с открытым коллектором или с тремя состояниями на выходе. Элемент 11 задержки задерживает передний фронт сигнала с выхода триггера 8 на время установления истинной информации на линиях АД после переднего фронта сигнала ОТВ. Величина задержки составляет приблизительно 150-200 не. Элемент ИЛИ 12 предназначен для объединения сигналов с выходов блока 5 и блока 6 (Yb). Элемент ИЛИ 13 предназначен для объединения сигнала линии 18 ДЗП и выхода блока 6 (Y4).

314

Вход 19 РЕЖИМ задает режим работы устройства. По сигналу на входе 20 ВВОД производится запись в счетчик адреса 3. На входах 21 СА задается системный адрес устройства. Выходы 22-25 предназначены для наращивания объема памяти.

Устройство работает в одном из двух режимов: режиме адресного обме- на (нулевое значение сигнала 19). режиме безадресной записи состояний магистрали (единичное состояние сигнала 19).

Режим адресного обмена - стандартный режим работы запоминающего устройства с обменом данными по интерфейсу МПИ. Интерфейс МПИ предусматривает обмен данными через двунаправленную магистраль АД по принципу ведущий - ведомый. Для обмена данными применяется асинхронный способ передачи с использованием управляющих сигналов 0МБ, ДЧТ, ДЗП и ОТВ. Возможны следующие виды адресного обмена: чтение, запись, чтение с модификацией.

При чтении ведущий устанавливает на линиях АД адрес, определяющий ведомого, и устанавливает сигнал на линии ОБМ. Устройства, подключенные- к магистрали, за время не более 75 не считывают и затем опознают адрес с линией АД. Устройство, опознавшее адрес, после появления сигнала ОБМ становится ведомым. Ведущий снимает адрес с линий АД, устанавливает сигнал на линии ДЧТ. Ведомый в ответ на сигнал ДЧТ устанавливает сигнал на линии ОТВ и данные на линиях АД. Ведущий принимает данные с линий АД и сбрасывает сигнал ДЧТ. Ведомый после снятия ведущим сигнала ДЧТ сбрасывает данные с линий АД и сигнал с линий ОТВ. Ведущий после снятия ве- домым сигнала ОТВ сбрасывает сигнал ОБМ. Магистраль освобождена дли передачи управления новому ведущему.

Операция записи отличается от чтения тем, что ведущий вместо ДЧТ фор- мирует сигнал ДЗП, данные на линиях АД выставляет ведущий, а ведомый данные записывает

По переднему фронту сигнала ОБМ адрес с линий 14 АД вводится в ре- гистр 2 адреса. Одновременно в блоке 5 управления адресным обменом старшие разряды адреса на линиях АД сравниваются с системным адресом, задава104

емым на входах 21. Если сравнения не произошло, то устройство до окончания текущего сигнала ОБМ в обмене данными не участвует. В случае сравнения адресов устройство до окончания сигнала OHM становится ведомом и блок 5 воспринимает входные и формирует ответные управляющие сигналы для взаимодействия с ведущим по дисциплине интерфейса МПИ. Кроме того, блок 5 формирует внутренний управляющий сигнал, который через элемент ИЛИ 12 поступает на вход выборки блока 1 памяти. Этот же сигнал поступает на мультиплексор 4 адреса и разрешает прохождение адреса ячейки с регистра 2 адреса в блок 1. В зависимости от состояния линии 18 ДЗП производится или чтение из блока 1 (), или запись в него (). Записанная в какую-то ячейку блока 1 информация сохраняется до следующей записи в эту же ячейку.

Таким образом, в адресном режиме устройство обеспечивает хранение данных и обмен данными с ведущим (процессором) по интерфейсу МПИ.

Режим безадресной записи задается единичным значением сигнала 19. В этом режиме устройство выполняет в полном объеме функции адресного режима и дополнительно записывает в блок 1 последовательно по каждому сигналу ОБМ состояния магистрали АД в моменты истинности на шине АД адреса и данных. Начальный адрес массива для записи магистрали вводится в счетчик 3 с шины АД по сигналу на входе 20.

Блок 6 управляет записью состояний магистрали АД и работает только при наличии сигнала на входе 19 (). В паузе между сигналами ОБМ (Х,0, ) формируются управляющие сигналы Y3 (выборка блока 1) и Y4 (запись), которые обеспечивают запись текущего состояния линий АД в блок 1. После появления сигнала ОБМ (Х, 1) формируется сигнал Y, (+1 в счетчик 3), затем при наличии сигнала ОТВ () и отсутствии сигнала с выхода блока 5 () производится повторная запись состояния линий АД в блок 1 с помощью сигналов Y3 и Y4, после чего сигналом Чг сбрасывается триггер 8 и сигналом-Y1 добавляется единица в счетчик 3. После сняти сигнала ОБМ цикл работы блока 6 по514729

вторяется. Таким образом, за один цикл работы блока 6, ограниченный периодом действия сигнала ОБМ, производится запись двух состояний линий АД: на момент конца паузы между сигналами ОБМ (на АД выставлен адрес) и на момент выполнения условия и (в этот момент времени производится запись данных).При записиIQ адреса и данных на адресный вход блока 1 через мультиплексор 4 поступает адрес со счетчика 3, поскольку в эти моменты времени сигнал на выходе блока 5, поступающий на мульти- 15 ппексор 4 (Х4), имеет нулевое значение.

При записи состояний магистрали возникает проблема сохранения истинного значения данных на линиях АД20 в момент их записи, поскольку управляющие сигналы ДЧТ, ДЗП, ОТВ, ОБМ, определяющие состояние линий АД, формируются ведущим и ведомым независимо от аппаратуры записи магистрали 25 и могут быть сняты до окончания цикла записи в блоке 6. Второй причиной возможного искажения данных на линиях АД является то, что если в качестве ведомого выступает предлагаемое 30 устройство, то необходимо в течение одного сигнала ОБМ обращение к двум адресам блока 1. Первое обращение производится для выполнения операции чтения или записи по адресу в регист- у- ре 2 адреса, второе обращение - при записи магистрали по адресу в счетчике 3. Это может привести к искажению данных на линиях АД к моменту второго обращения.40

Для устранения искажения данных на линиях АД во время записи магистрали в устройство введен триггер 8, элемент 11 задержки, блок 7. Триггер 8 в безадресном режиме расширяет че- 45 рез элемент 10 сопряжения управляющий сигнал ОТВ. Триггер 8 включается по переднему фронту сигнала 16 при разрешающем (единичном) уровне на входе 19. Триггер 8 остается включен- 50 ным до окончания записи состояния линий АД (выключается по управляющему сигналу Y1( вырабатываемому блоком 6). Наличие активного уровня на линии ОТВ, поддерживаемое триггером 55 8, препятствует ведущему снять текущий сигнал ОБМ и выставить очередной до завершения цикла записи в блоке 6 (см. фиг. 2). Через элемент

106

11задержки сигнал с выхода триггера 8 поступает также на блок 7. Под действием этого сигнала состояние линий АД через блок 7 поступает вновь да АД, за счет чего состояние линий АД сохраняется даже после снятия данных ведущим (при записи) или ведомым (при чтении) в ответ на снятие ДЧТ. Состояние линий АД поддерживается до выключения триггера 8 управляющим сигналом Y.J , т.е. до окончания записи состояния АД в блок I. После выключения триггера 8 ведущий снимает текущий сигнал ОБМ и переходит выполнению следующей операции.

Расширение триггером 8 сигнала ОТ может снижать быстродействие вычислительной системы, однако это снижение незначительно. Когда в качестве ведомого выступает не предлагаемое устройство, сигнал на выходе блока 5 отсутствует (см. фиг. 3),поэтому в блоке 6 условие , выполняется сразу после появления сигнала на линии ОТВ 16 и запись магистрали производится одновременно с выпол- . нением текущей операции в ведомом. Когда в качестве ведомого выступает предлагаемое устройство, цикл выполнения операции увеличивается на два микротакта (Аэ и А 4по фиг. 3).

Результатом работы устройства в безадресном режиме является записанный массив последовательных состояний линий АД в процессе выполнения программы. Начальный адрес массива вводится в счетчик 3. Массив представляет собой последовательность адресов и данных в том порядке, в каком они передавались по линиям АД, т.е. в этом массиве сохраняются сведения о ходе программы, промежуточных и конечных результатах выполнения программы.

Предлагаемое устройство может быть использовано в качестве оперативного запоминающего устройства в вычислительных системах. При этом наряду с традиционными функциями ОЗУ по хранению данных устройство может осуществлять запись в выделенную область памяти последовательности состояний магистрали в реальном масштабе времени. Содержимое этой области может быть выведено на экран или печатающее устройство системы, что дает возможность проводить отладку программ или поиск неисправностей

без дополнительного контрольного оборудования.

Формула изобретения

Запоминающее устройство, содержащее регистр адреса и блок управления адресным обменом, информационные входы регистра адреса, блока памяти и блока управления адресным обменом являются адресным информационным входом-выходом устройства, информационные входы регистра адреса и блок управления адресным обменом соединены с адресным информационным входом- выходом устройства, информационный вход-выход блока памяти соединен с адресным информационным входом-выходом устройства, вход-выход ответа устройства соединен с входом-выходом ответа блока управления адресным обменом, вход обмена устройства соединен с входом обмена блока управления адресным обменом и входом стробирова ния регистра адреса, входы -чтения и записи устройства соединены с входами чтения и записи блока управления , адресным обменом соответственно , вход системного адреса которого является входом системного адреса устройства, отличающее ся тем, что, с целью расширения функциональных возможностей за счет обеспечения синхронной безадресной записи состояний магистрали, в него введены счетчик адреса, мул -типлек- сор адреса, блок управления безадресной записью, блок фиксации данных, триггер, элемент И-НЕ, элемент сопряжения, элемент задержки, два элемен- та ИЛИ, причем выход мультиплексора адреса соединен с адресным входом блока памяти, выходы регистра и счетчика адресов соединены с первым и вторым информационными входами мультиплексора адреса соответственно, информационный вход регистра адреса соединен с информационным вводом счетчика адреса, вход ввода устройства соединен с входом записи счетчика адреса, выходы первого и второго

Q элементов ИЛИ соединены с входами выборки и чтения-записи блока памяти соответственно, информационные вход и выход блока фиксации данных соединены с адресным информационным

5 входом-выходом устройства, вход обмена устройства соединен с первым входом блока управления безадресной записью, второй.вход которого соединен с выходом элемента сопряжения

0 и входом-выходом ответа устройства, вход режима устройства соединен с первым входом элемента И-НЕ и третьим входом блока управления безадресной записью, выходы с первого по

5 четвертый которого соединены с суммирующим входом счетчика адреса, входом сброса в триггера и первыми входами первого и второго элементов ИЛИ соответственно, выход блока уп0 равления адресным обменом соединен с четвертым входом блока управления безадресной записью, входом управления мультиплексора адреса и втог рым входом первого элемента ИЛИ,

5 вход записи устройства соединен с вторым входом второго элемента ИЛИ, вход-выход ответа устройства соединен с вторым входом элемента И-НЕ, выход которого соединен с входом

0 стробирования триггера, выход которого соединен с входом элемента сопряжения и через элемент задержки - с входом стробирования блока фикса- ции данных.

{Начало

С Конец

Фиг. 3

I q:kkk

| Авторское свидетельство СССР № 1206787, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| М | |||

| : Энер- гоатомиздат, 1985, с | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-04-15—Публикация

1987-08-04—Подача