Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и телемеханики.

Цель изобретения - расширение функциональных возможностей путем расширения количества формируемых выходных последовательностей.

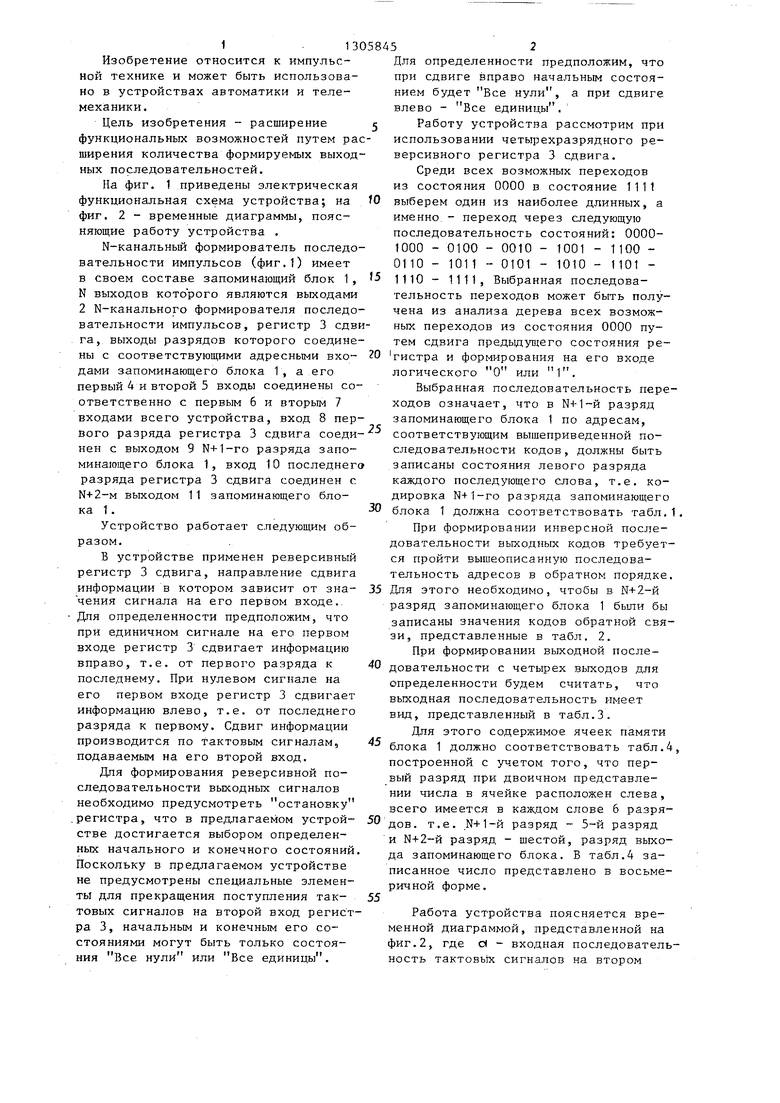

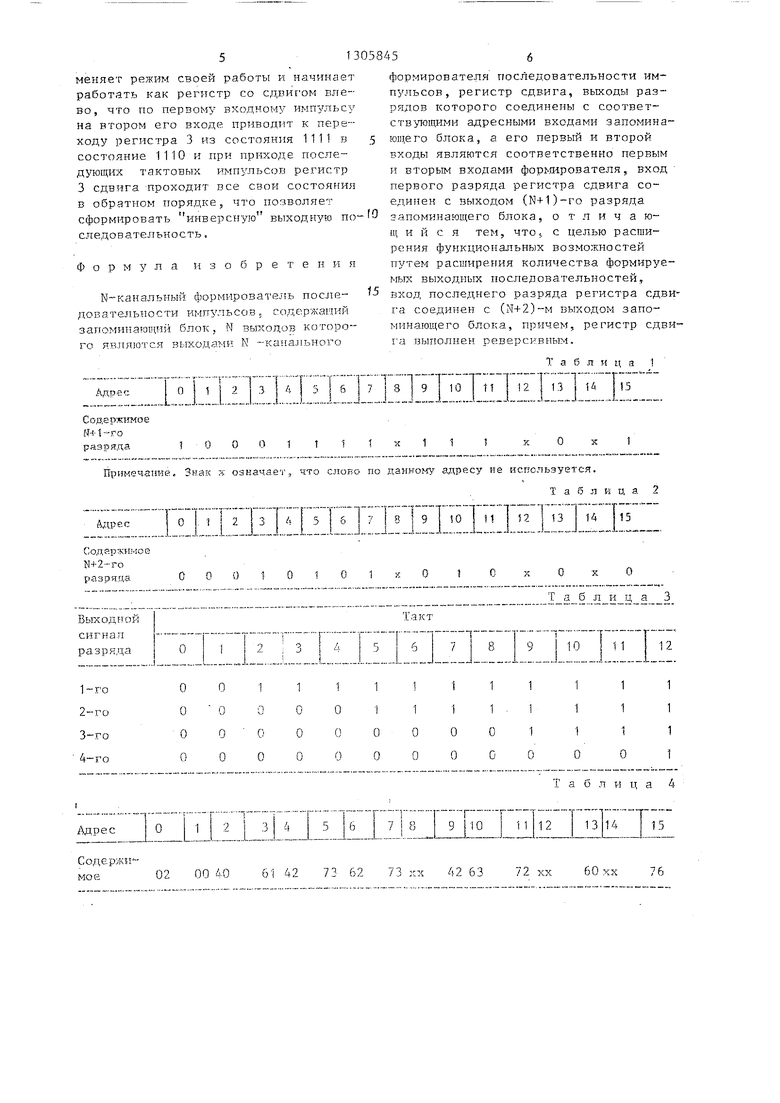

На фиг. 1 приведены электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства .

N-канальньй формирователь последовательности импульсов (фиг.1) имеет

в своем составе запоминающий блок 1, -5 1110-1111, Выбранная последова- N выходов которого являются выходами тельность переходов может быть полу- 2 N-канального формирователя последовательности импульсов, регистр 3 сдвига, выходы разрядов которого соединечена из анализа дерева всех возможных переходов из состояния 0000 путем сдвига предыдущего состояния рены с соответствующими адресными вхо- 0 гистра и формирования на его входе

дами запоминающего блока 1, а его первый 4 и второй 5 входы соединены соответственно с первым 6 и вторым 7 входами всего устройства, вход 8 первого разряда регистра 3 сдвига соединен с выходом 9 N+1-го разряда запоминающего блока 1, вход 10 последнего разряда регистра 3 сдвига соединен с N+2-M выходом 11 запоминающего бло- ка 1.

Устройство работает следующим образом.

В устройстве применен реверсивный регистр 3 сдвига, направление сдвига

информации в котором зависит от зна- 35 Для зтого необходимо, чтобы в N+2-й

чения сигнала на его первом входе..

Для определенности предположим, что при единичном сигнале на его первом входе регистр 3 сдвигает информацию вправо, т.е. от первого разряда к последнему. При нулевом сигнале на его первом входе регистр 3 сдвигает информацию влево, т.е. от последнего разряда к первому. Сдвиг информации производится по тактовым сигналам, подаваемым на его второй вход.

Для формирования реверсивной последовательности выходных сигналов необходимо предусмотреть остановку

регистра, что в пред.пагаемом устройстве достигается выбором определенных начального и конечного состояний. Поскольку в предлагаемом устройстве не предусмотрены специальные элементы для прекращения поступления тактовых сигналов на второй вход регистра 3, начальным и конечным его состояниями могут быть только состояния Все нули или Все единицы.

Для определенности предположим, что при сдвиге вправо начальным состоянием будет Все нули, а при сдвиге влево - Все единицы.

Работу устройства рассмотрим при использовании четырехразрядного реверсивного регистра 3 сдвига.

Среди всех возможных переходов из состояния 0000 в состояние 1111 выберем один из наиболее длинных, а именно. - переход через следующую последовательность состояний: 0000- 1000 - 0100 - 0010 - 1001 - 1100 - 0110 - 1011 - 0101 - 1010 - 1101 1110-1111, Выбранная последова- тельность переходов может быть полу-

чена из анализа дерева всех возможных переходов из состояния 0000 путем сдвига предыдущего состояния релогического О или 1.

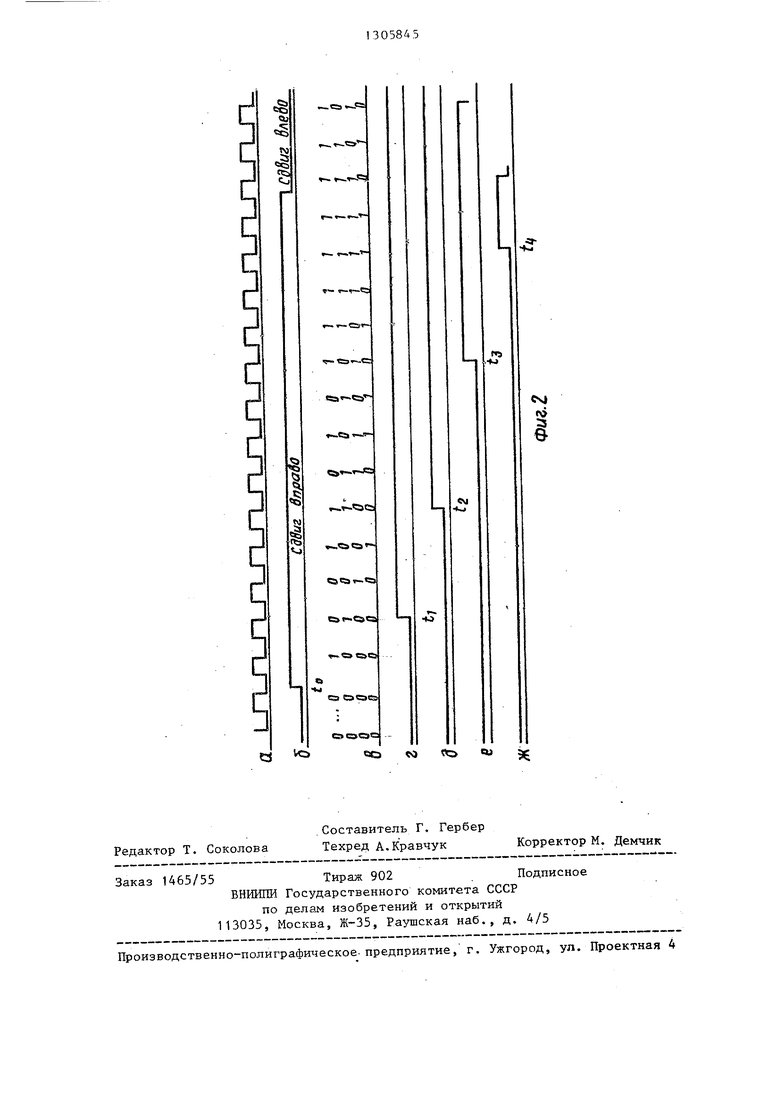

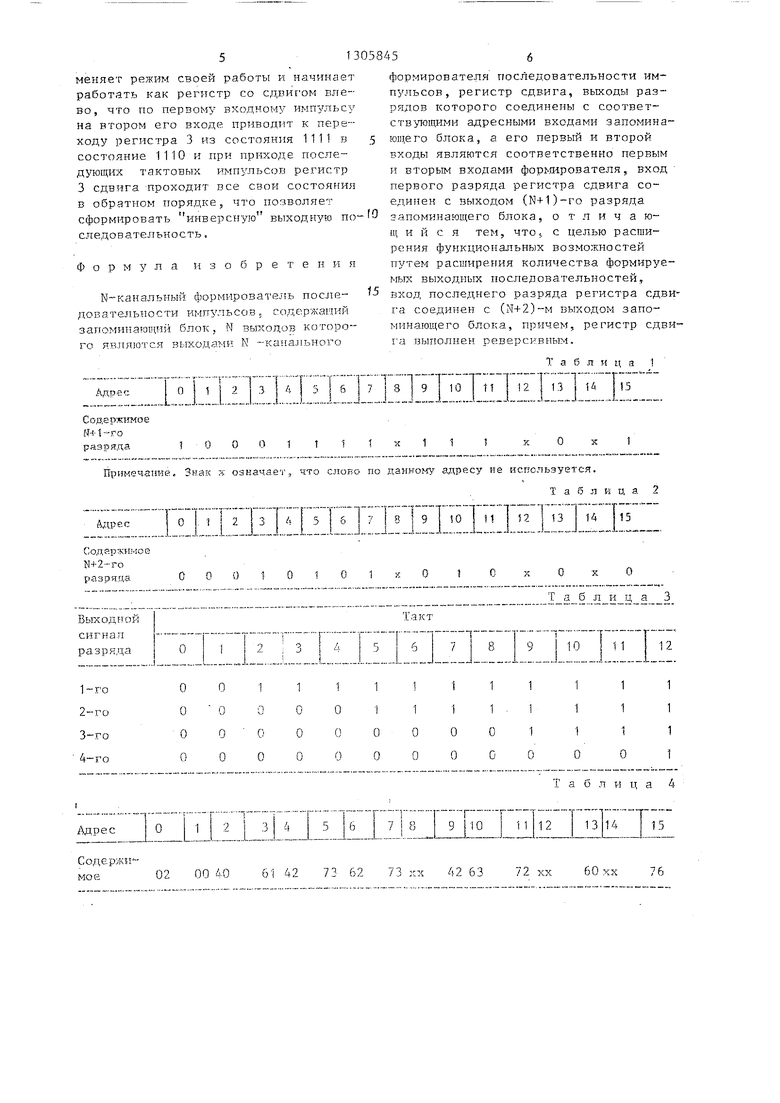

Выбранная последовательность переходов означает, что в N-l-1 й разряд запоминающего блока 1 по адресам, соответствующим вышеприведенной последовательности кодов, должны быть записаны состояния левого разряда каждого последующего слова, т.е. кодировка N-f1-ro разряда запоминающего блока 1 должна соответствовать табл.1

При формировании инверсной последовательности выходных кодов требуется пройти вышеописанную последовательность адресов в обратном порядке.

разряд запоминающего блока 1 быпи бы записаны значения кодов обратной связи, представленные в табл. 2.

При формировании выходной последовательности с четырех выходов для определенности будем считать, что выходная последовательность имеет вид, представленный в табл.3.

Для этого содержимое ячеек памяти блока 1 должно соответствовать табл.4, построенной с учетом того, что первый разряд при двоичном представлении числа в ячейке расположен слева, всего имеется в каж,дом слове 6 разрядов, т.е. N+1-й разряд - 5-й разряд и N+2-й разряд - шестой, разряд выхоа запоминающего блока. В табл.4 записанное число представлено в восьмеричной форме.

Работа устройства поясняется временной диаграммой, представленной на фиг.2, где а - входная последовательность тактовъ1х сигналов на втором

313058

входе 7 устройства, 6- состояние входа управления режимом работы регистра 3 сдвига, т.е. на его первом входе, B- запись текущего значения адреса (левый разряд сверху) i , 3 , е . и - значения выходных сигналов с первого, второго, третьет о и четвертого выходов 2 соответственно.

Предположим, что начальное состояние устройства характеризуется наличием низкого Потенциала на втором входе 5 регистра сдвига. В этом случае регистр 3 сдвига работает в режиме сдвига влево, т.е. в режиме сдвига от последнего разряда к первому. Допустим, что регистр 3 находится в состоянии 0000. Как следует из табл. 4, в ячейке памяти с адреW

f5

сом О записано число 02 (восьмерич25

30

ная запись), что соответствует двоич-20 g регистре 3 записано состояние 1100, ному представлению 000010, т.е. в N+1-м разряде () находится 1 и н N+2-M находится О. Поскольку регистр 3 работает в режиме сдвига влево, в последний разряд по тактам на первом входе записывается состояние О и, песмотря на то, что регистр 3 сдвигает информацию, его выходное состояние не изменяется, т.е. состояние GOOD является устойчивым. Допустим, что в некоторый момент времени С (фиг.2 5) на первый вход регистра 3 сдвига приходит высокий потенциал, т.е. регистр 3 переключается в режим сдвига вправо. Поскольку в N+1-м разряде записана 1, по первому после прихода сигнала на первый вход тактовому импульсу на втором входе регистр 3 принимает состояние 1000, что соответствует подключению к выходам

устройства ячейки памяти с адресом 1, где согласно табл.4 записано 00, что соответствует отсутствию сигналов на всех выходах устройства. По приходу следующего тактового импульса в первый разряд регистра записывается состояние 0100, так как произошел сдвиг на один разряд вправо с записью О в первый разряд регистра, т.е. на выходе 2 устройства появляются сигналы из ячейки запоминающего блока 1 с адресом 2, где согласно табл.4 записано число 40, что соотт.е. адрес 3, где записано число 61, что соответствует появлению высокого потенциала на втором выходе устройства t (фиг.2 3). В ячейке с адресом 3 в N+1-м разряде записано состояние О, т.е. по следующему такту он переходит в состояние 0110 или 6 и соответственно к выходу запоминающего блока 1 подключена шестая ячейка с содержимым 62 и так далее. В моменты времени, соответствующие подключению к выходам запоминающего блока 1 ячеек с адресами соответственно 5 и 15, происхо- 35 дят изменения на соответственно третьем и четвертом выходах формирователя импульсов tj и t (фиг.2 г , Ж.) соответственно.

При достижении регистром сдвига состояния 1111 и неизменном, состоянии на его первом входе к выходу устг ройства подключена ячейка памяти с адресом 15, где записано число 76, что соответствует наличию логической единицы на входе первого и логического нуля на входе последнего разряда регистра сдвига. До тех пор, пока стояние управляющего сигнала на первом входе регистра 3 сдвига не изменится, не изменяется и его выходное состояние, поскольку на его первый разряд подается высокий потенциал, и, несмотря на то, что регистр сдвигает информацию, его состояние,остается 1111, т.е. это состояние устройства устойчиво.

40

45

50

55

ветствует появлению высокого потенци ала на первом выходе устройства t (фиг.2 г). В этот момент на N+1-м выходе зaпo данaюlцeгo блока 1 имеет .

5

ся потендиал логического нуля, т.е. по следующему тактовому импульсу в регистр 3 запишется состояние 0010, т.е. к выходу устройства ггодключе- на ячейка памяти с числом 42, что соответствует наличию логической единицы на первом и N+1-м выходах запоминающего блока 1. По следующему такту в первый разряд регистра 3 записывается единица и с учетом сдвига на один разряд регистр принимает состояние 1001, т.е. к выходам запоминающего блока 1 подключается ячейка с адресом 9. В ячейке по зтому

адресу согласно табл.4 записано число 42, что соответствует отсутствию изменения состояния выходов запоминающего блока 1. Однако по следующему входному тактовому импульсу

25

30

20 g регистре 3 записано состояние 1100,

т.е. адрес 3, где записано число 61, что соответствует появлению высокого потенциала на втором выходе устройства t (фиг.2 3). В ячейке с адресом 3 в N+1-м разряде записано состояние О, т.е. по следующему такту он переходит в состояние 0110 или 6 и соответственно к выходу запоминающего блока 1 подключена шестая ячейка с содержимым 62 и так далее. В моменты времени, соответствующие подключению к выходам запоминающего блока 1 ячеек с адресами соответственно 5 и 15, происхо- 35 дят изменения на соответственно третьем и четвертом выходах формирователя импульсов tj и t (фиг.2 г , Ж.) соответственно.

При достижении регистром сдвига состояния 1111 и неизменном, состоянии на его первом входе к выходу устг ройства подключена ячейка памяти с адресом 15, где записано число 76, что соответствует наличию логической единицы на входе первого и логического нуля на входе последнего разряда регистра сдвига. До тех пор, пока стояние управляющего сигнала на первом входе регистра 3 сдвига не изменится, не изменяется и его выходное состояние, поскольку на его первый разряд подается высокий потенциал, и, несмотря на то, что регистр сдвигает информацию, его состояние,остается 1111, т.е. это состояние устройства устойчиво.

При приходе на первый вход регистра 3 сдвига низкого потенциала он из40

45

50

55

меняет режим своей работы и начинает работать как регистр со сдвигом влево, что по первому входному инпульс у на втором его входе приводит к переходу регистра 3 из состояния 1111 в состояние 1110 и при приходе последующих тактовых Р мпупьсов регистр 3 сдвига проходит все свои состояния в обратном порядке, что позволяет сформировать инверсную выходную по следовательность.

Формула и 3 о б р е т е н и я

К канальный формировате.тгь последовательности импульсов; содержаний запоминаюп1И 1 блок, N выходов которого являются выходами N -канального

Адрес

О j 1 j 2 3 Д I 5 I 6 7 1 3 1 9 10 1 11 12 I 13 1 1i 15

L.. ..J.- -. I.,-Л-.t-.-„.L....J J-J:- i-.-...-.1....-. J- J.-...-,

1

0 0

0

1

Примечание, Знак jt означает,, что слово по данному адресу не используется.

Т а б л к ц а

top ее

ШЕНЕГЕСЕЕЕ

Содержимое

NH-2-го

разряда

О О

1--ГО

2-го 3-го

Адрес

,

Содержимое02 00 i-0

D i 42 73 62 73 ;сх 42 63

58456

формироватедя последовательности импульсов, регистр сдвига, выходы разрядов которого соединены с соответ- ств ующими адресными входами запомина- 5 ющего блока, а его первый и второй входы являются соответственно первым vi вторым входами формирователя, вход первого разряда регистра сдвига соединен с выходом (N+1)-ro разряда запоминающего блока, о т л и ч а ю(0

щ инея тем, что5 с целью расширения функциональных возможностей путем расширения количества формируемых выходных последовательностей, вход последнего разряда регистра сдвига соединен с (М+2)-м выходом запоминающего блока, причем, регистр сдви- 1 а выполнен реверсивным.

Т а б л и ц а 1

1

1

1

0

и

13 13

14

ПИ,

Т а блица 3

Т а б л и ц а 4

....J-,.„.,..„.....„

9 |j О j 11 11 2 I 13114

15

72 XX

60 XX

76

Ц VOОСЭ VO tb «U

Редактор Т. Соколова

Составитель Г. Гербер Техред А.Кравчук

Заказ 1465/55Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое-предприятие, г. Ужгород, ул. Проектная 4

Корректор М. Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Канальный формирователь последовательности импульсов | 1984 |

|

SU1200417A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Устройство для задержки сигналов | 1985 |

|

SU1345325A1 |

| Генератор шкалы частот электромузыкального инструмента | 1984 |

|

SU1234878A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1314388A1 |

Изобретение может быть исполь- ювано в устройствах автоматики и телемеханики. Цель изобретения - расширение функциональных возможностей устройства. Формирователь содержит запоминающий блок 1 с N выходами и регистр 3 сдвига. Выполнение последнего реверсивным и соединение входа последнего разряда регистра 3 сдвига с (N+2)-M выходом запоминающего блока 1 расширяют количество формируемых выходных последовательностей. 4 табл. 2 ил. Фиг.1

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОПТИЧЕСКИХ ХАРАКТЕРИСТИК СВЕТОРАССЕЯНИЯ В ДВУХФАЗНЫХ ГАЗОДИНАМИЧЕСКИХ ПОТОКАХ | 2012 |

|

RU2504754C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| @ -Канальный формирователь последовательности импульсов | 1984 |

|

SU1200417A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-27—Подача