Изобретение относится к импульсной технике, в частности к устройствам. предназначенным для управления многоканальными усилителями мощности с двухтактным выходом, и может быть использовано в устройствах возбуждения многоэлементных антенных решеток, а также в устройствах автоматического управления.

Цель изобретения - расширение функциональных возможностей устройства для задержки сигналов за счет формирования дополнительной серии выходных импульсов и повышение быстродействия устройства.

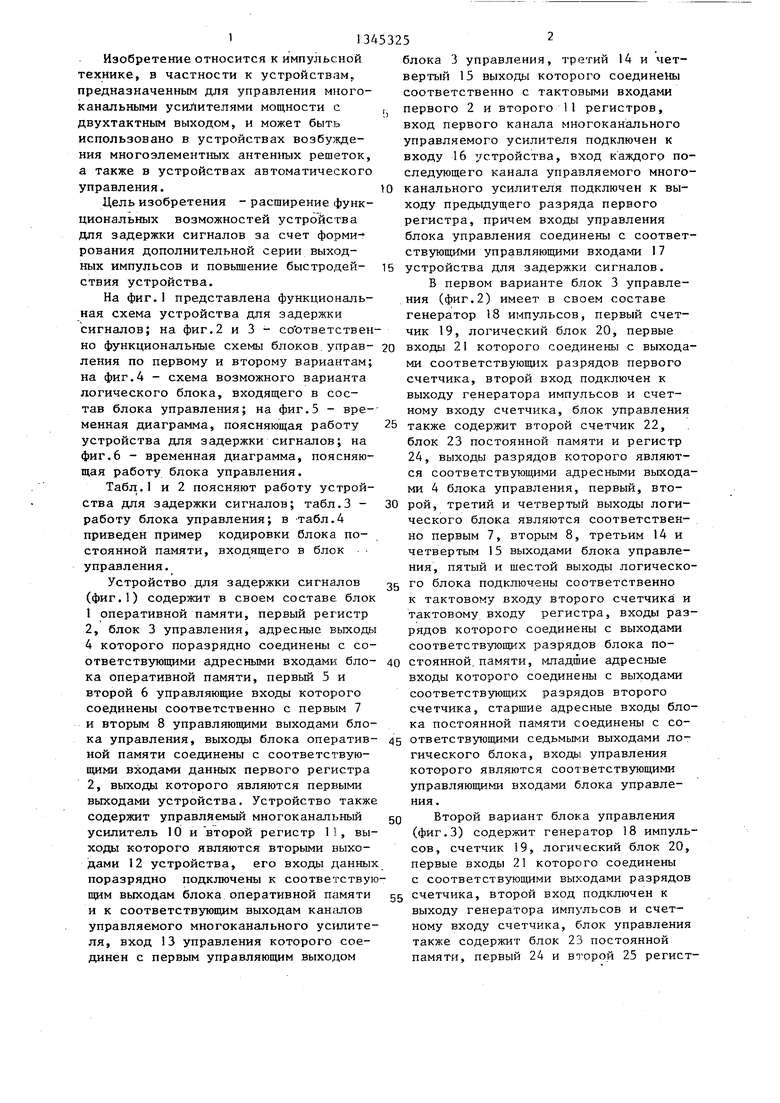

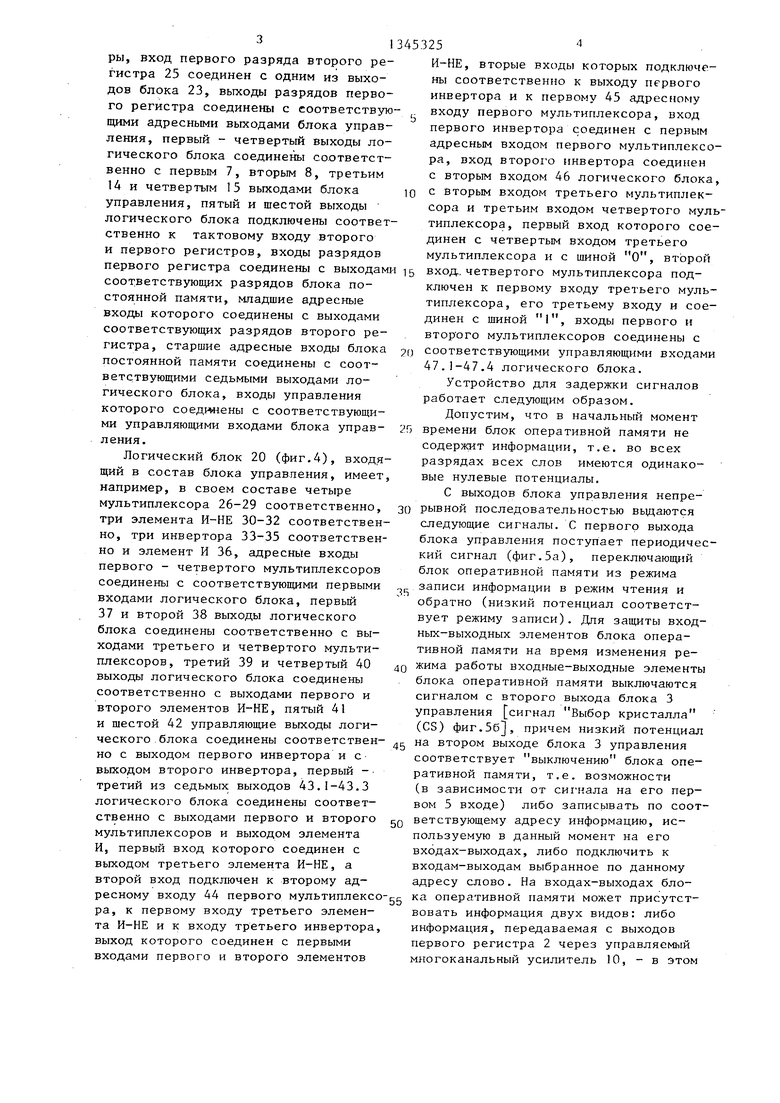

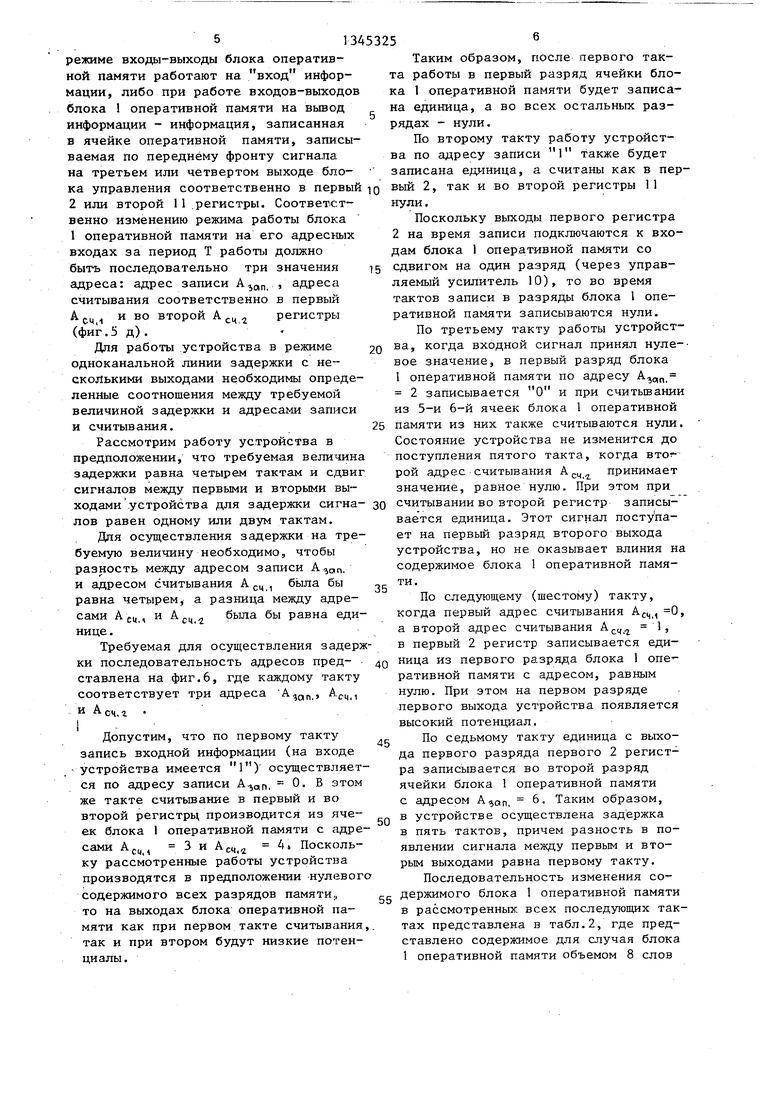

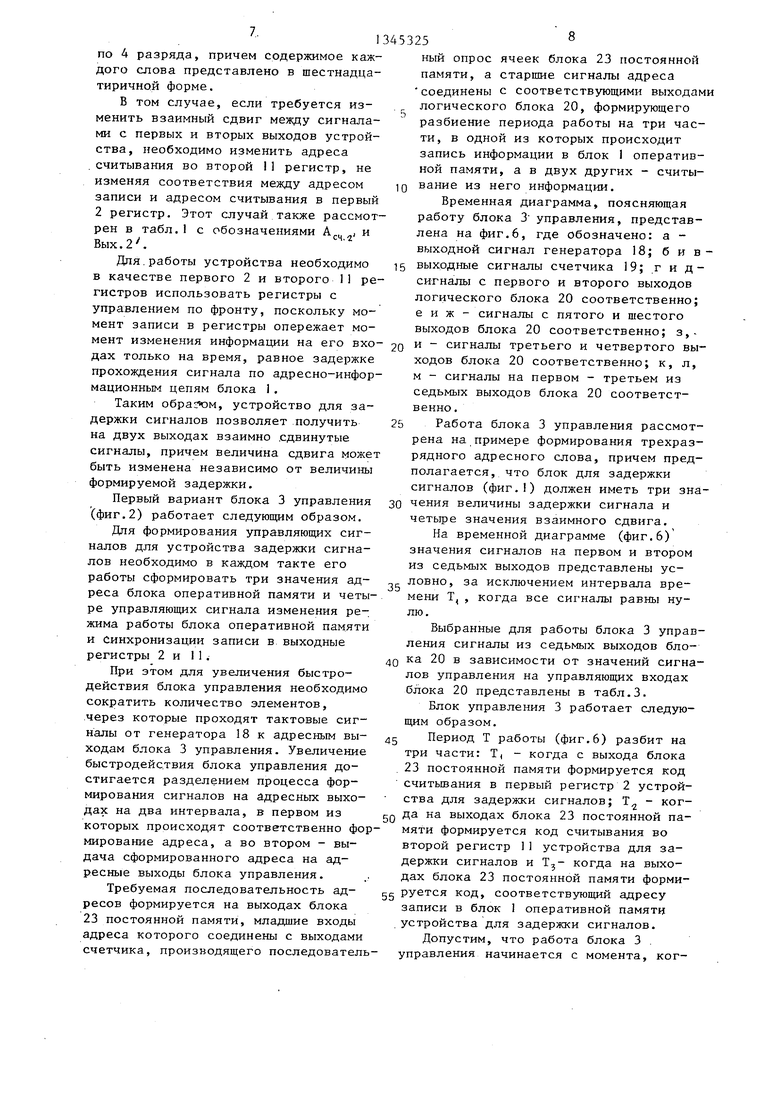

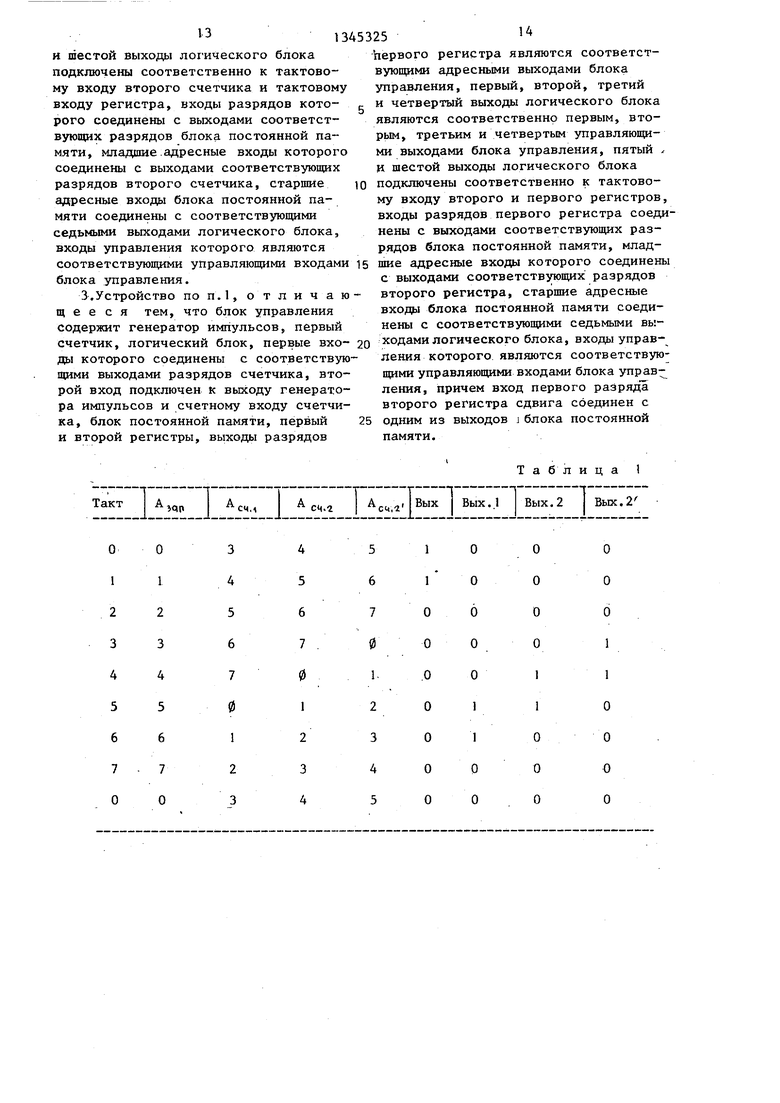

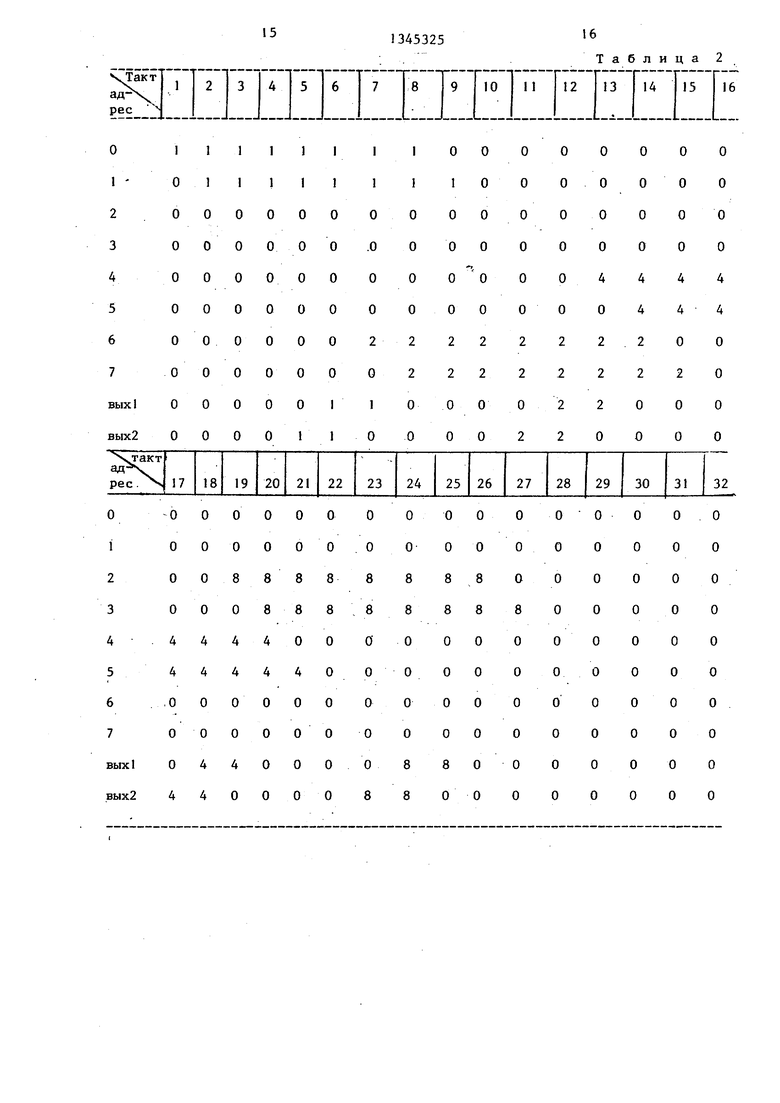

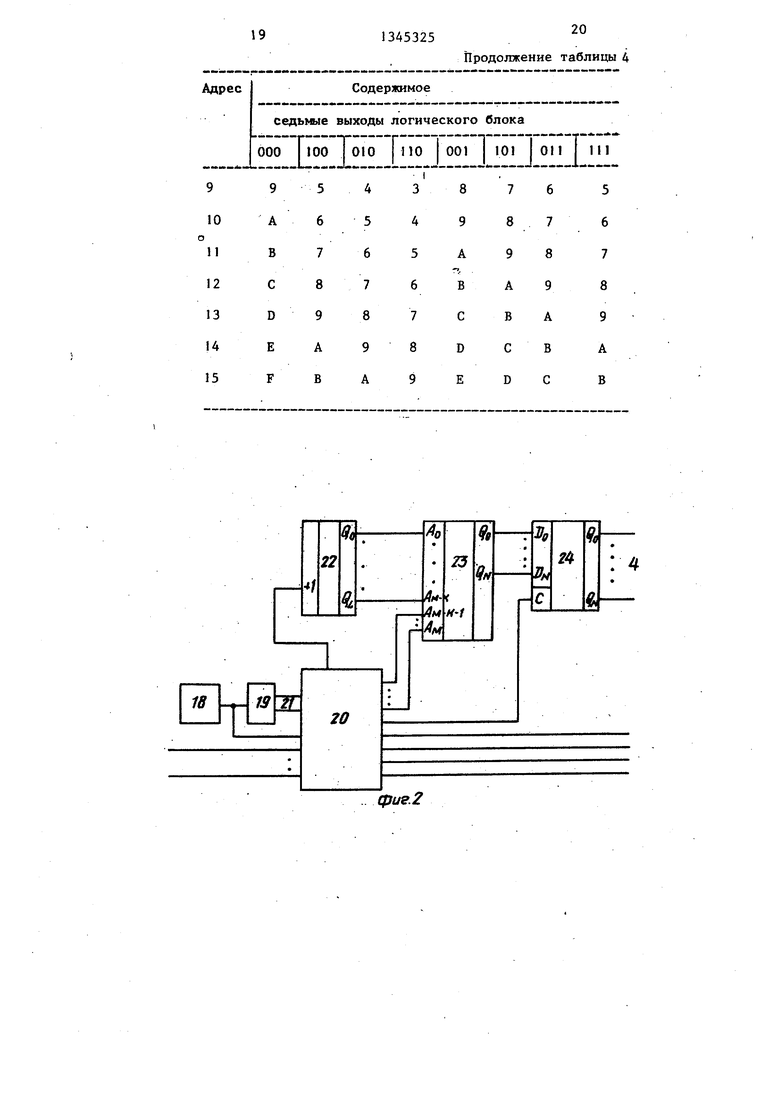

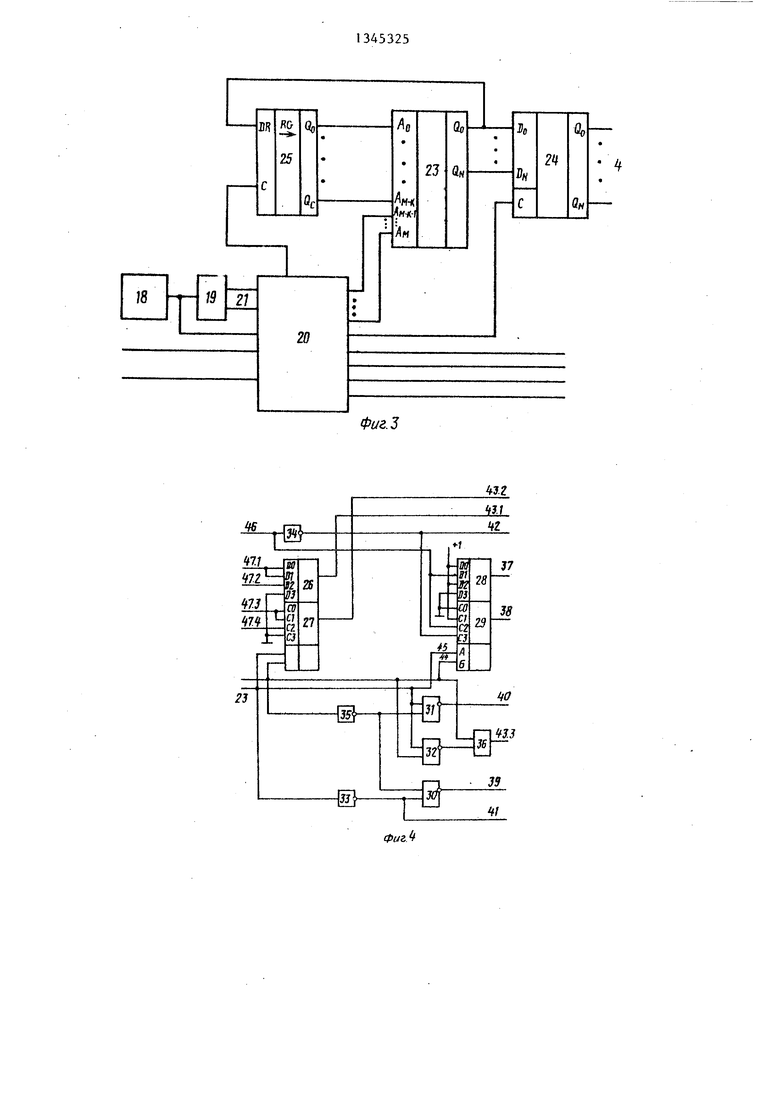

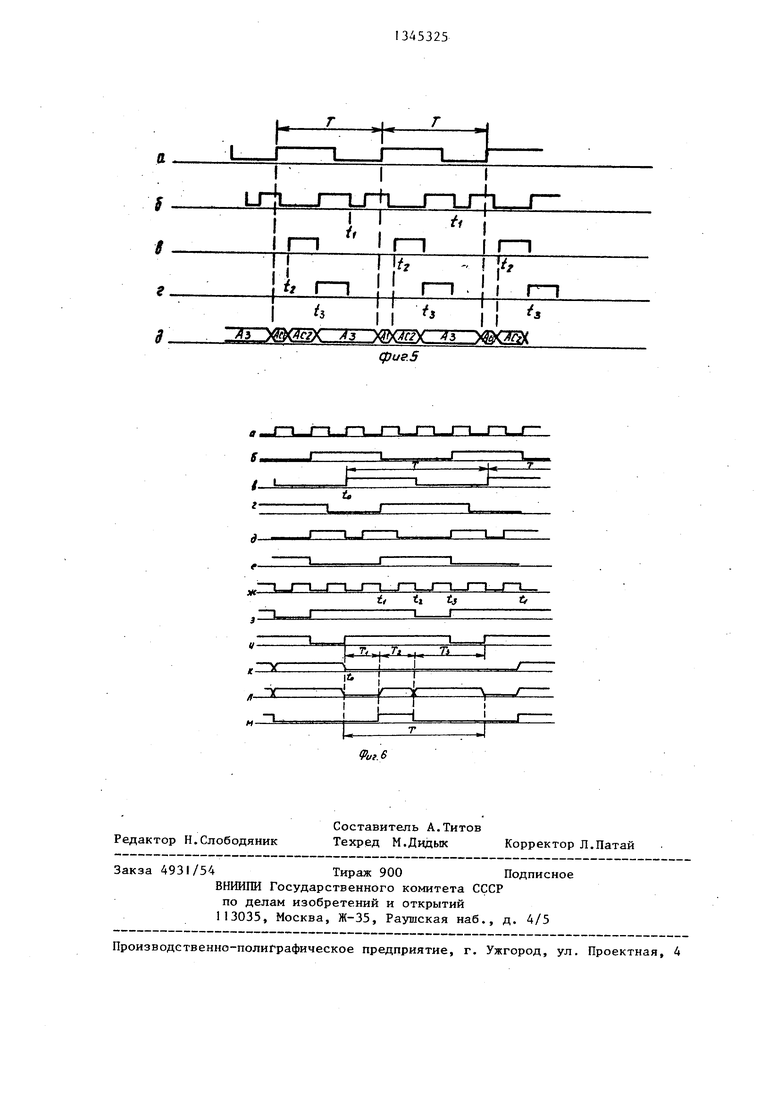

На фиг.1 представлена функциональная схема устройства для задержки сигналов; на фиг.2 и 3 - со ответственно функциональные схемы блоков управ- 20 входы 21 которого соединены с выходаления по первому и второму вариантам; на фиг.4 - схема возможного варианта логического блока, входящего в состав блока управления; на фиг.5 - временная диаграмма, поясняющая работу устройства для задержки сигналов; на фиг.6 - временная диаграмма, поясняющая работу блока управления.

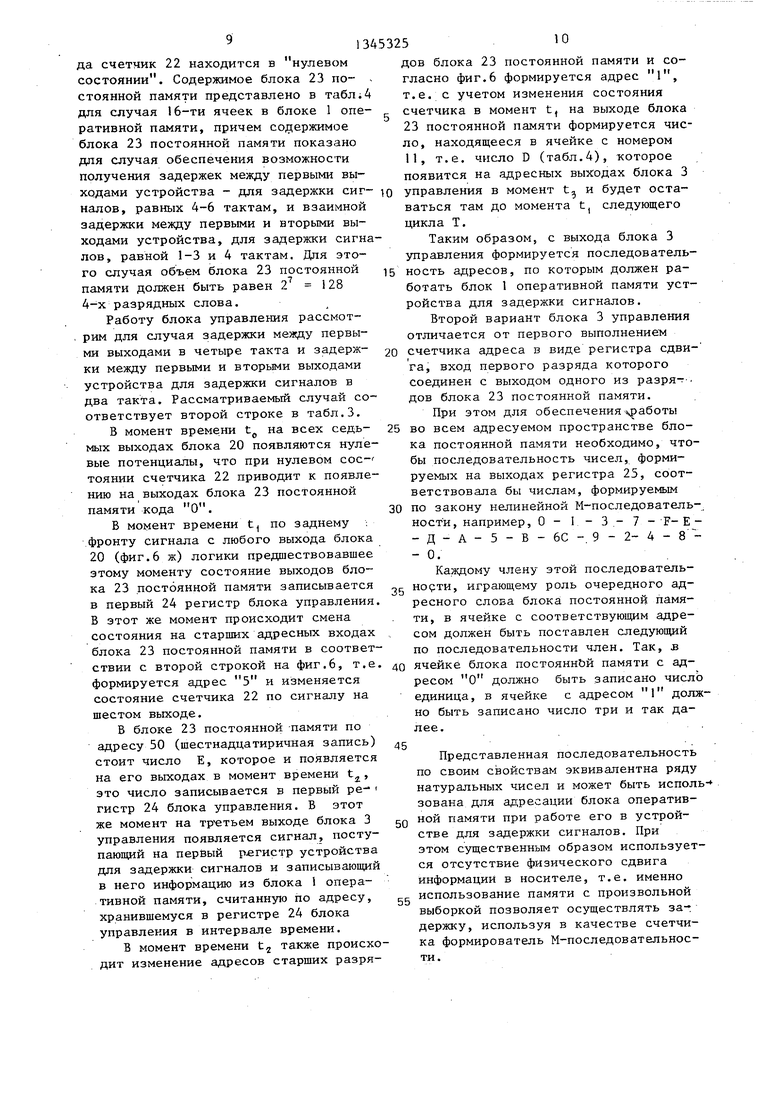

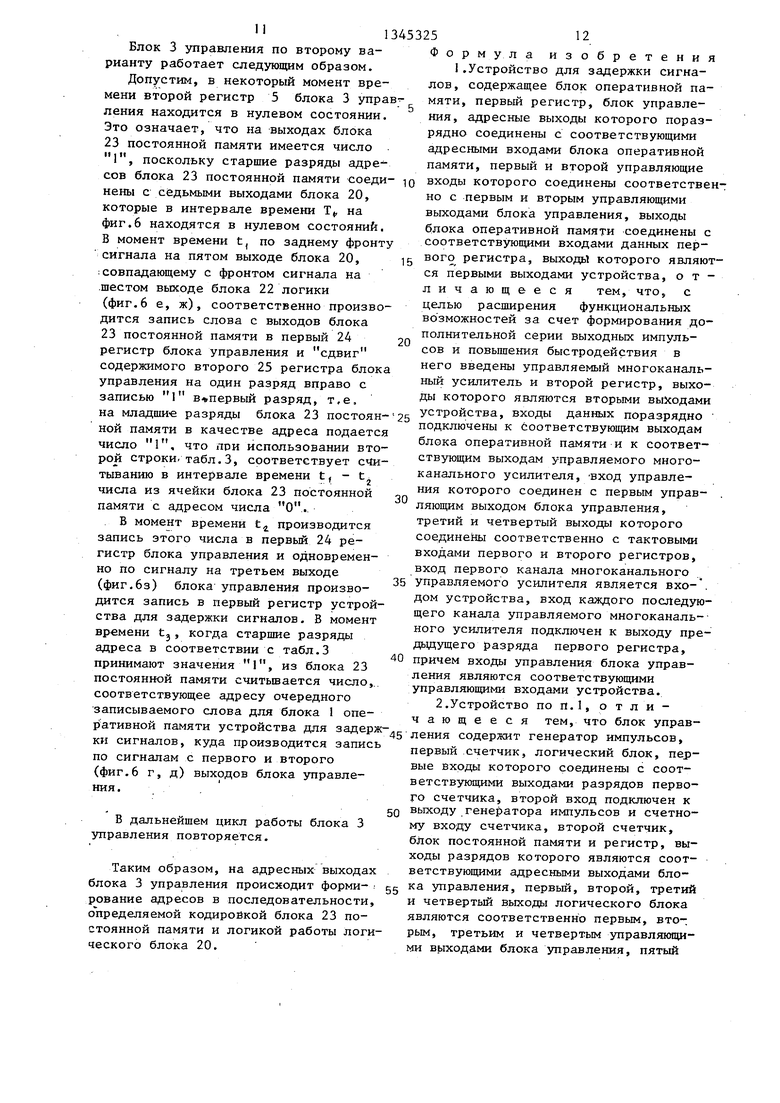

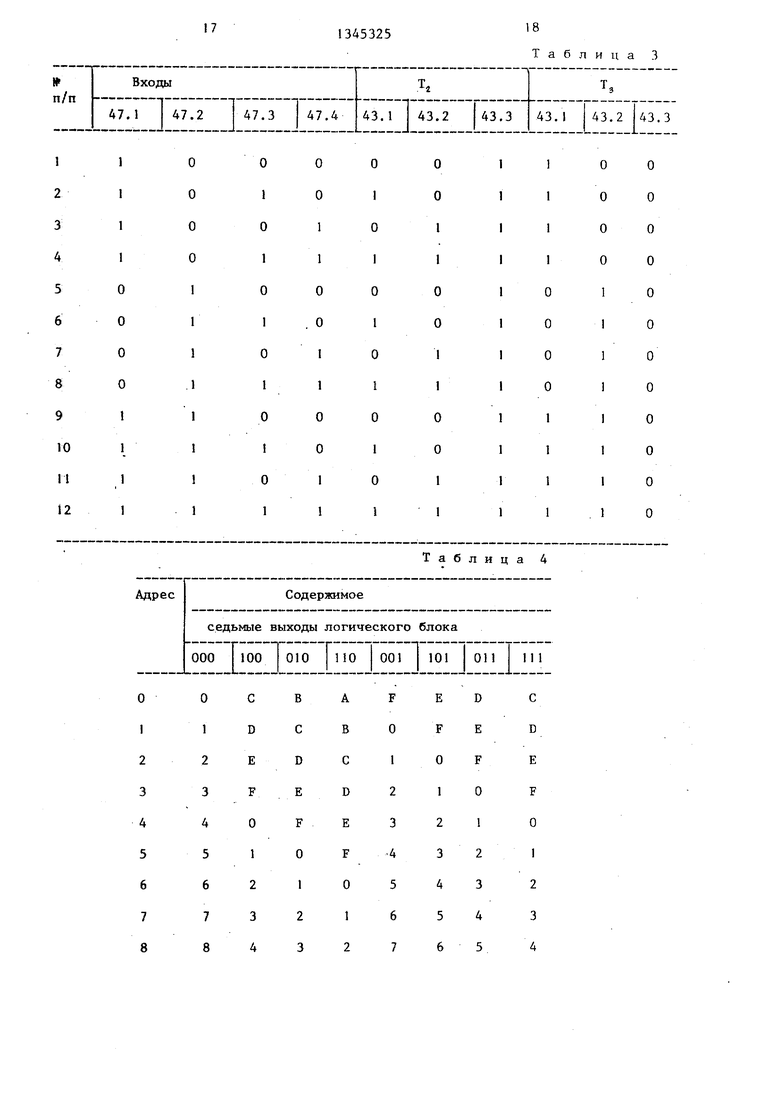

Табл.1 и 2 поясняют работу устройства для задержки сигналов; табл.3 - работу блока управления; в табл.4 приведен пример кодировки блока постоянной памяти, входящего в блок управления.

Устройство для задержки сигналов (фиг.1) содержит в своем составе блок 1 оперативной памяти, первый регистр 2, блок 3 управления, адресные выходы 4 которого поразрядно соединены с соответствующими адресными входами блока оперативной памяти, первьш 5 и второй 6 управляющие входы которого соединены соответственно с первым 7 и вторым 8 управляющими выходами бломи соответствующих разрядов первого счетчика, второй вход подключен к выходу генератора импульсов и счетному входу счетчика, блок управления

25 также содержит второй счетчик 22, блок 23 постоянной памяти и регистр 24, выходы разрядов которого являются соответствующими адресными выходами 4 блока управления, первый, вто30 рой, третий и четвертый выходы логического блока являются соответственно первым 7, вторым 8, третьим 14 и четвертым 15 выходами блока управления, пятый и шестой выходы логическо35 го блока подключены соответственно к тактовому входу второго счетчика и тактовому входу регистра, входы разрядов которого соединены с выходами соответствующих разрядов блока по40 стоянной. памяти, младшие адресные входы которого соединены с выходами соответствующих разрядов второго счетчика, старшие адресные входы блока постоянной памяти соединены с сока управления, выходы блока оператив- 45 ответствующими седьмыми выходами ло- ной памяти соединены с соответствую- гического блока, входы управления

щими входами данных первого регистра 2, выходы которого являются первыми выходами устройства. Устройство также содержит управляемый многоканальный усилитель 10 и второй регистр 11, выходы которого являются вторыми выходами 12 устройства, его входы данных поразрядно подключены к соответствующим выходам блока оперативной памяти и к соответствующим выходам кангшов управляемого многоканального усилителя, вход 13 управления которого соединен с первым управляющим выходом

блока 3 управления, третий 14 и четвертый 15 выходы которого соединены соответственно с тактовыми входами

первого 2 и второго 1 1 регистров, вход первого канала многоканального управляемого усилителя подключен к входу 16 устройства, вход каждого последующего канала управляемого многоканального усилителя подключен к выходу предьщущего разряда первого регистра, причем входы управления блока управления соединены с соответствующими управляющими входами 17

устройства для задержки сигналов.

В первом варианте блок 3 управления (фиг.2) имеет в своем составе генератор 18 импульсов, первый счетчик 19, логический блок 20, первые

ми соответствующих разрядов первого счетчика, второй вход подключен к выходу генератора импульсов и счетному входу счетчика, блок управления

также содержит второй счетчик 22, блок 23 постоянной памяти и регистр 24, выходы разрядов которого являются соответствующими адресными выходами 4 блока управления, первый, второй, третий и четвертый выходы логического блока являются соответственно первым 7, вторым 8, третьим 14 и четвертым 15 выходами блока управления, пятый и шестой выходы логического блока подключены соответственно к тактовому входу второго счетчика и тактовому входу регистра, входы разрядов которого соединены с выходами соответствующих разрядов блока постоянной. памяти, младшие адресные входы которого соединены с выходами соответствующих разрядов второго счетчика, старшие адресные входы блокоторого являются соответствующими управляющими входами блока управления.

50 Второй вариант блока управления (фиг.З) содержит генератор 18 импульсов, счетчик 19, логический блок 20, первые входы 21 которого соединены с соответствующим выходами разрядов

55 счетчика, второй вход подключен к выходу генератора импульсов и счетному входу счетчика, блок управления также содержит блок 23 постоянной памяти, первый 24 и второй 25 регист

ры, вход первого разряда второго регистра 25 соединен с одним из выходов блока 23, выходы разрядов первого регистра соединены с соответствующими адресными выходами блока управ- , первый - четвертый выходы логического блока соединены соответственно с первым 7, вторым 8, третьим 14 и четвертым 15 выходами блока управления, пятый и шестой выходы логического блока подключены соответственно к тактовому входу второго и первого регистров, входы разрядов первого регистра соединены с выходам соответствующих разрядов блока постоянной памяти, младшие адресные входы которого соединены с выходами соответствующих разрядов второго регистра, старшие адресные входы блока постоянной памяти соединены с соответствующими седьмыми выходами логического блока, входы управления которого соединены с соответствующими управляющими входами блока управления.

Логический блок 20 (фиг.4), входящий в состав блока управления, имеет например, в своем составе четыре мультиплексора 26-29 соответственно, три элемента И-НЕ 30-32 соответственно, три инвертора 33-35 соответственно и элемент И 36, адресные входы первого - четвертого мультиплексоров соединены с соответствующими первыми входами логического блока, первый 37 и второй 38 выходы логического блока соединены соответственно с выходами третьего и четвертого мультиплексоров, третий 39 и четвертый 40 выходы логического блока соединены соответственно с выходами первого и второго элементов И-НЕ, пятый 41 и шестой 42 управляющие выходы логи

ческого блока соединены соответствен- на втором выходе блока 3 управления

но с выходом первого инвертора и с выходом второго инвертора, первый - третий из седьмых выходов 43.1-43.3 логического блока соединены соответственно с выходами первого и второго мультиплексоров и выходом элемента И, первьш вход которого соединен с выходом третьего элемента И-НЕ, а второй вход подключен к второму адресному входу 44 первого мультиплексо- ка оперативной памяти может присутст ра, к первому входу третьего элемен- вовать информация двух видов: либо та И-НЕ и к входу третьего инвертора, выход которого соединен с первыми входами первого и второго элементов

информация, передаваемая с выходов первого регистра 2 через управляемый многоканальный усилитель 10, - в этом

10

0

15

И-НЕ, вторые входы которых подключены соответственно к выходу первого инвертора и к первому 45 адресному входу первого мультиплексора, вход первого инвертора соединен с первым адресным входом первого мультиплексора, вход второг о инвертора соединен с вторым входом 46 логического блока, с Вторым входом третьего мультиплексора и третьим входом четвертого мультиплексора, первый вход которого соединен с четвертым входом третьего мультиплексора и с шиной О, второй вход, четвертого мультиплексора подключен к первому входу третьего мультиплексора, его третьему входу и соединен с шиной 1, входы первого и второго мультиплексоров соединены с соответствующими управляющими входами 47.1-47.4 логического блока.

Устройство для задержки сигналов работает следующим образом.

Допустим, что в начальный момент 5 времени блок оперативной памяти не содержит информации, т.е. во всех разрядах всех слов имеются одинаковые нулевые потенциалы,

С выходов блока управления непрерывной последовательностью выдаются следующие сигналы. С первого выхода блока управления поступает периодический сигнал (фиг.5а), переключающий блок оперативной памяти из режима записи информации в режим чтения и обратно (низкий потенциал соответствует режиму записи). Для защиты входных-выходных элементов блока оперативной памяти на время изменения ре- Q жима работы входные-выходные элементы блока оперативной памяти выключаются сигналом с второго выхода блока 3 управления сигнал Выбор кристалла (CS) фиг.5б, причем низкий потенциал

0

0

соответствует выключению блока оперативной памяти, т.е. возможности (в зависимости от сиг нала на его первом 5 входе) либо записывать по соответствующему адресу информацию, используемую в данный момент на его входах-выходах, либо подключить к входам-выходам выбранное по данному адресу слово. На входах-выходах блока оперативной памяти может присутст вовать информация двух видов: либо

информация, передаваемая с выходов первого регистра 2 через управляемый многоканальный усилитель 10, - в этом

режиме входы-выходы блока оперативной памяти работают на вход информации, либо при работе входов-выходов блока 1 оперативной памяти на вывод информации - информация, записанная в ячейке оперативной памяти, записываемая по переднему фронту сигнала на третьем или четвертом выходе бло-

ка управления соответственно в первый ю ш 2, так и во второй регистры 11

2 или второй 11 .регистры. Соответственно изменению режима работы блока I оперативной памяти на его адресных входах за период Т работы должно быть последовательно три значения адреса: адрес записи А,,дп , адреса считывания соответственно в первый

15

нули.

Поскольку выходы первого регистр 2 на время записи подключаются к вх дам блока 1 оперативной памяти со сдвигом на один разряд (через управ ляемый усилитель 10), то во время тактов записи в разряды блока I опе ративной памяти записываются нули.

А,Ц И ВО второй А .ц регистры (фиг.5 д).Для работы устройства в режиме одноканальной линии задержки с не- сколькиьш выходами необходимы определенные соотношения между требуемой величиной задержки и адресами записи и считывания.

Рассмотрим работу устройства в предположении, что требуемая величина задержки равна четырем тактам и сдвиг сигналов между первыми и вторыми выходами .устройств а для задержки сигналов равен одному или двум тактам.

Для осуществления задержки на требуемую величину необходимо, чтобы разность между адресом записи А,an.

И адресом считывания А

СЧ,1

была бы

равна четырем, а разница между адреА

СМИ

И А

сч.-г

была бы равна единице.

Требуемая для осуществления задержки последовательность адресов представлена на фиг.6, где каждому такту

три адреса А

д Jan. ,1

Допустим, что по первому такту запись входной информации (на входе устройства имеется 1) осуществляется по адресу записи , 0. В этом же такте считывание в первый и во второй регистру производится из ячеек блока 1 оперативной памяти с адресами А

СМИ

3 и А

еч.й

41 Поскольку рассмотренные работы устройства производятся в предположении нулевого содержимого всех разрядов памяти,, то на выходах блока оперативной памяти как при первом такте считывания,, так и при втором будут низкие потенциалы.

Таким образом, после первого такта работы в первый разряд ячейки блока 1 оперативной памяти будет записана единица, а во всех остальных разрядах - нули.

По второму такту работу устройства по адресу записи 1 также будет записана единица, а считаны как в пер5

0

5

0

35

40

45

50

55

нули.

Поскольку выходы первого регистра 2 на время записи подключаются к входам блока 1 оперативной памяти со сдвигом на один разряд (через управляемый усилитель 10), то во время тактов записи в разряды блока I оперативной памяти записываются нули.

По третьему такту работы устройства, когда входной сигнал принял нуле-- вое значение, в первый разряд блока 1 оперативной памяти по адресу Азд, 2 записывается О и при считьшании из 5-и 6-й ячеек блока 1 оперативной памяти из них также считываются нули. Состояние устройства не изменится до поступления пятого такта, когда рой адрес считывания принимает значение, равное, нулю. При этом при считывании во вто.рой регистр записывается единица. Этот сигнал посту па- ет на первый разряд второго выхода устройства, но не оказывает влиния на содержимое блока 1 оперативной памяти.

По следующему (шестому) такту, когда первый адрес считывания . 0 а второй адрес считывания 1, в первый 2 регистр записывается единица из первого разряда блока 1 опе- ративной памяти с адресом, равным нулю. При этом на первом разряде первого выхода устройства появляется высокий потенциал.

По седьмому такту единица с выхода первого разряда первого 2 регистра записывается во второй разряд ячейки блока 1 оперативной памяти с адресом , 6, Таким образом, в устройстве осуществлена задержка в пять тактов, причем разность в появлении сигнала между первым и вто- рьм выходами равна первому такту.

Последовательность изменения содержимого блока 1 оперативной памяти в рассмотренных всех последующих тактах представлена в табл.2, где представлено содержимое для случая блока 1 оперативной памяти объемом 8 слов

обозначениями А. , и

по 4 разряда, причем содержимое каждого слова представлено в шестнадцатиричной форме.

В том случае, если требуется изменить взаимный сдвиг между сигналами с первых и вторых выходов устройства, необходимо изменить адреса считывания во второй И регистр, не изменяя соответствия между адресом записи и адресом считывания в первый 2 регистр. Этот случай также рассмотрен в табл.1 с Вых.2.

Для,работы устройства необходимо в качестве первого 2 и второго II регистров использовать регистры с управлением по фронту, поскольку момент записи в регистры опережает момент изменения информации на его входах только на время, равное задержке прохождения сигнала по адресно-информационным цепям блока 1.

Таким обра:№м, устройство для задержки сигналов позволяет получить на двух выходах взаимно сдвинутые сигналы, причем величина сдвига може быть изменена независимо от величины формируемой задержки.

Первый вариант блока 3 управления (фиг.2) работает следующим образом.

Для формирования управляющих сигналов для устройства задержки сигналов необходимо в каждом такте его работы сформировать три значения адреса блока оперативной памяти и четыре управляющих сигнала изменения режима работы блока оперативной памяти и Синхронизации записи в выходные регистры 2 и 11.

При этом для увеличения быстродействия блока управления необходимо сократить количество элементов, через которые проходят тактовые сигналы от генератора 18 к адресным выходам блока 3 управления. Увеличение быстродействия блока управления достигается разделением процесса формирования сигналов на адресных выходах на два интервала, в первом из которых происходят соответственно формирование адреса, а во втором - выдача сформированного адреса на адресные выходы блока управления.

Требуемая последовательность адресов формируется на выходах блока 23 постоянной памяти, младшие входы адреса которого соединены с выходами счетчика, производящего последователь0

5

0

5

0

5

ный опрос ячеек блока 23 постоянной памяти, а старшие сигналы адреса соединены с соответствующими выходами логического блока 20, формирующего разбиение периода работы на три части, в одной из которых происходит запись информации в блок 1 оперативной памяти, а в двух других - считывание из него информации.

Временная диаграмма, поясняющая работу блока 3 управления, представлена на фиг.6, где обозначено: а - выходной сигнал генератора 18; б и в- выходнью сигналы счетчика 19; г и д- сигналы с первого и второго выходов логического блока 20 соответственно; е и ж - сигналы с пятого и шестого выходов блока 20 соответственно; з,- и - сигналы третьего и четвертого выходов блока 20 соответственно; к, л, м - сигналы на первом - третьем из седьмых выходов блока 20 соответственно.

Работа блока 3 управления рассмотрена на примере формирования трехразрядного адресного слова, причем предполагается, что блок для задержки сигналов (фиг.1) должен иметь три значения величины задержки сигнала и четыре значения взаимного сдвига.

На временной диаграмме (фиг.6) значения сигналов на первом и втором из седьмых выходов представлены условно, за исключением интервала вре

когда все сигналы равны ну0

мени лю.

Выбранные для работы блока 3 управления сигналы из седьмых выходов блока 20 Б зависимости от значений сигналов управления на управляющих входах блока 20 представлены в табл.3.

Блок управления 3 работает следующим образом.

5 Период Т работы (фиг.6) разбит на три части: Т( - когда с выхода блока 23 постоянной памяти формируется код считывания в первый регистр 2 устройства для задержки сигналов; Т - когда на выходах блока 23 постоянной памяти формируется код считывания во второй регистр 11 устройства для задержки сигналов и когда на выходах блока 23 постоянной памяти форми5 РУется код, соответствующий адресу записи в блок 1 оперативной памяти устройства для задержки сигналов. Допустим, что работа блока 3 . управления начинается с момента, ког0

да счетчик 22 находится в нулевом состоянии. Содержимое блока 23 по- стоянкой памяти представлено в табл;4 для случая 16-ти ячеек в блоке 1 оперативной памяти, причем содержимое блока 23 постоянной памяти показано для случая обеспечения возможности получения задержек между первыми выходами устройства - для задержки сиг- IQ управления в момент t, и будет останалов, равных 4-6 тактам, и взаимной задержки между первыми и вторыми выходами устройства, для задержки сигналов, равной 1-3 и 4 тактам. Для этого случая объем блока 23 постоянной памяти должен быть равен 2 128 4-х разрядных слова.

Работу блока управле1-шя рассмотрим для случая задержки между первыми выходами в четыре такта и задержки между первыми и вторыми выходами устройства для задержки сигналов в два такта. Рассматриваемый случай соответствует второй строке в табл.3.

В момент времени t на всех седьмых выходах блока 20 появляются нулевые потенциалы, что при нулевом сое- тоянии счетчика 22 приводит к появлению на выходах блока 23 постоянной памяти кода О.

В момент времени t, по заднему фронту сигнала с любого выхода блока 20 (фиг.6 ж) логики предшествовавшее этому моменту состояние выходов блока 23 постоянной памяти записывается в первый 24 регистр блока управления. В этот же момент происходит смена состояния на старших адресных входах блока 23 постоянной памяти в соответствии с второй строкой на фиг.6, т.е. формируется адрес 5 и изменяется состояние счетчика 22 по сигналу на шестом выходе.

В блоке 23 постоянной памяти по адресу 50 (шестнадцатиричная запись) стоит число Е, которое и появляется на его выходах в момент времени t, это число записывается в первый ре- гистр 24 блока управления. В этот же момент на тр етьем выходе блока 3 управления появляется сигнал, поступающий на первый регистр устройства для задержки сигналов и записывающий в него информацию из блока 1 оперативной памяти, считанну о по адресу, хранившемуся в регистре 24 блока управления в интервале времени.

В момент времени t также происходит изменение адресов старших разря15

20

25

30

35

40

45

50

55

ваться там до момента t, следующего цикла Т.

Таким образом, с выхода блока 3 управления формируется последовательность адресов, по которым должен работать блок 1 оперативной памяти устройства для задержки сигналов.

Второй вариант блока 3 управления отличается от первого выполнением счетчика адреса в виде регистра сдвига, вход первого разряда которого соединен с выходом одного из разря-- дов блока 23 постоянной памяти.

При этом для обеспечениячработы во всем адресуемом пространстве блока постоянной памяти необходимо, чтобы последовательность чисел, формируемых на выходах регистра 25, соответствовала бы числам, формируемым по закону нелинейной М-последователь- ност и, например, 0-1-3 -7- F- Е - -Д-А-5-В-6С-. 9-2-4-8- - 0.

Каждому члену этой последователь- норти, играющему роль очередного адресного слова блока постоянной памяти, в ячейке с соответствующим адресом должен быть поставлен следующий по последовательности член. Так, в ячейке блока постояннЬй памяти с адресом О должно быть записано число единица, в ячейке с адресом 1 долж но быть записано число три и так далее.

Представленная последовательность по своим свойствам эквивалентна ряду натуральных чисел и может быть исполь зована для адресации блока оперативной памяти при работе его в устройстве для задержки сигналов. При этом существенным образом используется отсутствие физического сдвига информации в носителе, т.е. именно использование памяти с произвольной выборкой позволяет осуществлять задержку, используя в качестве счетчика формирователь М-последовательнос- ти.

дов блока 23 постоянной памяти и согласно фиг.6 формируется адрес 1, т.е. с учетом изменения состояния счетчика в момент t, на выходе блока 23 постоянной памяти формируется число, находящееся в ячейке с номером 11, т.е. число D (табл.4), которое появится на адресных выходах блока 3

0

5

0

5

0

5

0

55

ваться там до момента t, следующего цикла Т.

Таким образом, с выхода блока 3 управления формируется последовательность адресов, по которым должен работать блок 1 оперативной памяти устройства для задержки сигналов.

Второй вариант блока 3 управления отличается от первого выполнением счетчика адреса в виде регистра сдви га, вход первого разряда которого соединен с выходом одного из разря-- дов блока 23 постоянной памяти.

При этом для обеспечениячработы во всем адресуемом пространстве блока постоянной памяти необходимо, чтобы последовательность чисел, формируемых на выходах регистра 25, соответствовала бы числам, формируемым по закону нелинейной М-последователь- ност и, например, 0-1-3 -7- F- Е - -Д-А-5-В-6С-. 9-2-4-8- - 0.

Каждому члену этой последователь- норти, играющему роль очередного адресного слова блока постоянной памяти, в ячейке с соответствующим адресом должен быть поставлен следующий по последовательности член. Так, в ячейке блока постояннЬй памяти с адресом О должно быть записано число единица, в ячейке с адресом 1 должно быть записано число три и так далее.

Представленная последовательность по своим свойствам эквивалентна ряду натуральных чисел и может быть исполь- зована для адресации блока оперативной памяти при работе его в устройстве для задержки сигналов. При этом существенным образом используется отсутствие физического сдвига информации в носителе, т.е. именно использование памяти с произвольной выборкой позволяет осуществлять задержку, используя в качестве счетчика формирователь М-последовательнос- ти.

Блок 3 управления по второму варианту работает следующим образом.

Допустим, в некоторый момент времени второй регистр 5 блока 3 управления находится в нулевом состоянии. Это означает, что на выходах блока 23 постоянной памяти имеется число 1, поскольку старшие разряды адре сов блока 23 постоянной памяти соеди- ю нены с седьмыми выходами блока 20, которые в интервале времени Т,, на фиг.6 находятся в нулевом состояний, В момент времени t, по заднему фронту сигнала на пятом выходе блока 20, ig :совпадающему с фронтом сигнала на .шестом выходе блока 22 логики (фиг,6 е, ж), соответственно производится запись слова с выходов блока 23 постоянной памяти в первый 24 20 регистр блока управления и сдвиг содержимого второго 25 регистра блока управления на один разряд вправо с записью 1 в- первый разряд, т.е. на младшие разряды блока 23 постоян 25 ной памяти в качестве адреса подается число 1, что ПРИ использовании второй строки, табл.3, соответствует считыванию в интервале времени t, - t,j числа из ячейки блока 23 постоянной памяти с адресом числа О..

В момент времени t производится запись зтого числа в первьй 24 регистр блока управления и одновременно по сигналу на третьем выходе (фиг.бз) блока управления производится запись в первый регистр устройства для задержки сигналов, В момент времени t адреса в

принимают значения 1, из блока 23 постоянной памяти считьшается число,, соответствующее адресу очередного записываемого слова для блока 1 опеФ

30

35

UJ, когда старшие разряды соответствии с табл.З

40

ормула изобретения

I.Устройство для задержки сигналов, содержащее блок оперативной памяти, первый регистр, блок управления, адресные выходы которого поразрядно соединены с соответствующими адресными входами блока оперативной памяти, первый и второй управляющие входы которого соединены соответствен но с первым и вторым управляющими выходами блока управления, выходы

блока оперативной памяти соединены с соответствующими входами данных первого регистра, выходь1 которого являют ся первыми выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования дополнительной серии выходных импульсов и повьшения быстродействия в него введены управляемый многоканальный усилитель и второй регистр, выходы которого являются вторыми выходами устройства, входы данных поразрядно подключены к соответствующим выходам блока оперативной памяти и к соответствующим выходам управляемого многоканального усилителя, ВХОД управления которого соединен с первым управ- ляющим выходом блока управления, третий и четвертый выходы которого соединены соответственно с тактовыми входами первого и второго регистров, вход первого канала многоканального управляемого усилителя является вхо- . дом устройства, вход каждого последующего канала управляемого многоканального усилителя подключен к выходу пре- дьщущего разряда первого регистра, причем входы управления блока управления являются соответствующими управляющими входами устройства, 2,Устройство по п,1, отличающееся тем, что блок управ- ративной памяти устройства для задерж- д ения содержит генератор импульсов,

первый счетчик, логический блок, первые входы которого соединены с соответствующими выходами разрядов первого счетчика, второй вход подключен к 50 выходу генератора импульсов и счетному входу счетчика, второй счетчик, блок постоянной памяти и регистр, выходы разрядов которого являются соответствующими адресными выходами блока управления, первый, второй, третий и четвертый выходы логического блока являются соответственно первым, вто-: рым, третьим и четвертым управляющими выходами блока управления, пятый

ки сигналов, куда производится запись по сигналам с первого и второго (фиг,6 г, д) выходов блока управления .

В дальнейшем цикл работы блока 3 управления повторяется.

Таким образом, на адресных выходах блока 3 управления происходит форми- 55 рование адресов в последовательности, определяемой кодировкой блока 23 постоянной памяти и логикой работы логического блока 20.

юig 0 25

Ф

0

5

0

ормула изобретения

I.Устройство для задержки сигналов, содержащее блок оперативной памяти, первый регистр, блок управления, адресные выходы которого поразрядно соединены с соответствующими адресными входами блока оперативной памяти, первый и второй управляющие входы которого соединены соответственно с первым и вторым управляющими выходами блока управления, выходы

блока оперативной памяти соединены с соответствующими входами данных первого регистра, выходь1 которого являются первыми выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования дополнительной серии выходных импульсов и повьшения быстродействия в него введены управляемый многоканальный усилитель и второй регистр, выходы которого являются вторыми выходами устройства, входы данных поразрядно подключены к соответствующим выходам блока оперативной памяти и к соответствующим выходам управляемого многоканального усилителя, ВХОД управления которого соединен с первым управ- . ляющим выходом блока управления, третий и четвертый выходы которого соединены соответственно с тактовыми входами первого и второго регистров, вход первого канала многоканального управляемого усилителя является вхо- . дом устройства, вход каждого последующего канала управляемого многоканаль ного усилителя подключен к выходу пре- дьщущего разряда первого регистра, причем входы управления блока управления являются соответствующими управляющими входами устройства, 2,Устройство по п,1, отли13

и шестой выходы логического блока подключены соответственно к тактовому входу второго счетчика и тактовому входу регистра, входы разрядов которого соединены с выходами соответствующих разрядов блока постоянной памяти, младшие.адресные входы которого соединены с выходами соответствующих разрядов второго счетчика, старшие адресньш входы блока постоянной памяти соединены с соответствующими седьмыми выходами логического блока, входы управления которого являются

13453251

первого регистра являются соответствующими адресными выходами блока управления, первый, второй, третий

,. и четвертый выходы логического блока

о

являются соответственно первым, вторым, третьим и четвертым управляющими выходами блока управления, пятый , К шестой выходы логического блока

)0 подключены соответственно к тактовому входу второго и первого регистров, входы разрядов первого регистра соединены с выходами соответствующих разрядов блока постоянной памяти, младсоответствующими управляющими входами 15 шие адресные входы которого соединены

с выходами соответствующих разрядов второго регистра, старшие адресные входы блока постоянной памяти соединены с соответствующими седьмыми выблока управления.

З.Устройство по п. 1, отличающееся тем, что блок управления содержит генератор импульсов, первый счетчик, логический блок, первые вхо- 20 ходами логического блока, входы управ- ды которого соединены с соответствую- пения которого являются соответствующими выходами разрядов счетчика, вто- щими управляющими входами блока управ- рой вход подключен к выходу генерато- ления, причем вход первого разряда ра импульсов и счетному входу счетчи- второго регистра сдвига соединен с

ка, блок постоянной памяти, первый и второй регистры, выходы разрядов

Такт А рАСЦ,А. сц. I Ар, Вых Вых..1 Вых.2 Вых.2

с выходами соответствующих разрядов второго регистра, старшие адресные входы блока постоянной памяти соединены с соответствующими седьмыми выходами логического блока, входы управ- пения которого являются соответствующими управляющими входами блока управ- ления, причем вход первого разряда второго регистра сдвига соединен с

25 одним из выходов J блока постоянной памяти,

I

Таблица 1

Таблица 2

Таблица 3

Таблица 4

в

S,

г

фиг 5

t.

F

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2013 |

|

RU2540818C1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

Изобретение может быть использовано, например, в устройствах возбуждения многоэлементных антенных решеток и позволяет расширить функциональные возможности устройства и его быстродействие. Устройство со- держит блок 1 оперативной памяти, ре- гистр 2 и блок 3 управления. Введение управляемого многоканального усилителя ГО и регистра 11 позволяет сформировать дополнительную серию выходных импульсов. Величина сдвига получаемых на двух выходах взаимно сдвинутых сигналов может быть изменена независимо от величины формируемой задержки. В описании приведены примеры выполнения блока 3 управления. 2 з.п. ф-лы, 6 ил. 4 табл. с

Редактор Н.Слободяник

Составитель А.Титов Техред М.Дидык

Закза 4931/54Тираж 900Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Патай

| Устройство для задержки импульсов | 1980 |

|

SU875607A1 |

| Устройство для задержки сигналов | 1978 |

|

SU824191A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1987-10-15—Публикация

1985-12-29—Подача