1;

(21)433Й73/24-24

(22)20.11.87

(46) 28.02.90. Бюл. VF 8

(71)Пензенский политехнический институт

(72)А.А.Ломовцев, В.П.Сафронов, Б.П.Сибринин и С.В.Трубицков (53) 621.385 (088.8)

(56) Федорков Б.Г. и др. Микроэлектронные цифроаналоговые и аналого-цифровые преобразователи. М.: Радио и связь, 1984.

Патент США Vf 4473818, кл. Н 03 М 1/66, опублик, 1984.

(5) УСТРОЙСТВО ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ

Нулебои код

(57) Изобретение относится к автоматике и вычислительной технике и предназначено для построения преооразо- вателей цифровой информации в аналоговую. Цель изобретения - повышение точности. Устройство цифроаналогового преобразования содержит цифровой сумматор 1, первый 2 и второй 3 коммутаторы, первый 4 и второй 5 цифроаналоговые преобразователи и аналоговый сумматор 6. Положительный эффект достигнут за счет введения цифрового сумматора и выполнения первого коммутатора на три положения, что позволило исключить нелинейность характеристики преобразования в середине шкалы 1 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для построения преобразователей цифровой информации в аналоговую. Цель изобретения - повышение точности. Устройство цифроаналогового преобразования содержит цифровой сумматор 1, первый 2 и второй 3 коммутаторы, первый 4 и второй 5 цифроаналоговые преобразователи и аналоговый сумматор 6. Положительный эффект достигнут за счет введения цифрового сумматора и выполнения первого коммутатора на три положения, что позволило исключить нелинейность характеристики преобразования в середине шкалы. 1 ил.

Младшие разрядьП

код

Старший разряд

Я

1

L- Г

Изобретение относится к автоматике и вычислительной технике и предназначено для построения преобразователей цифровой информации в анало- говую.

Цель изобретения - повышение точности .

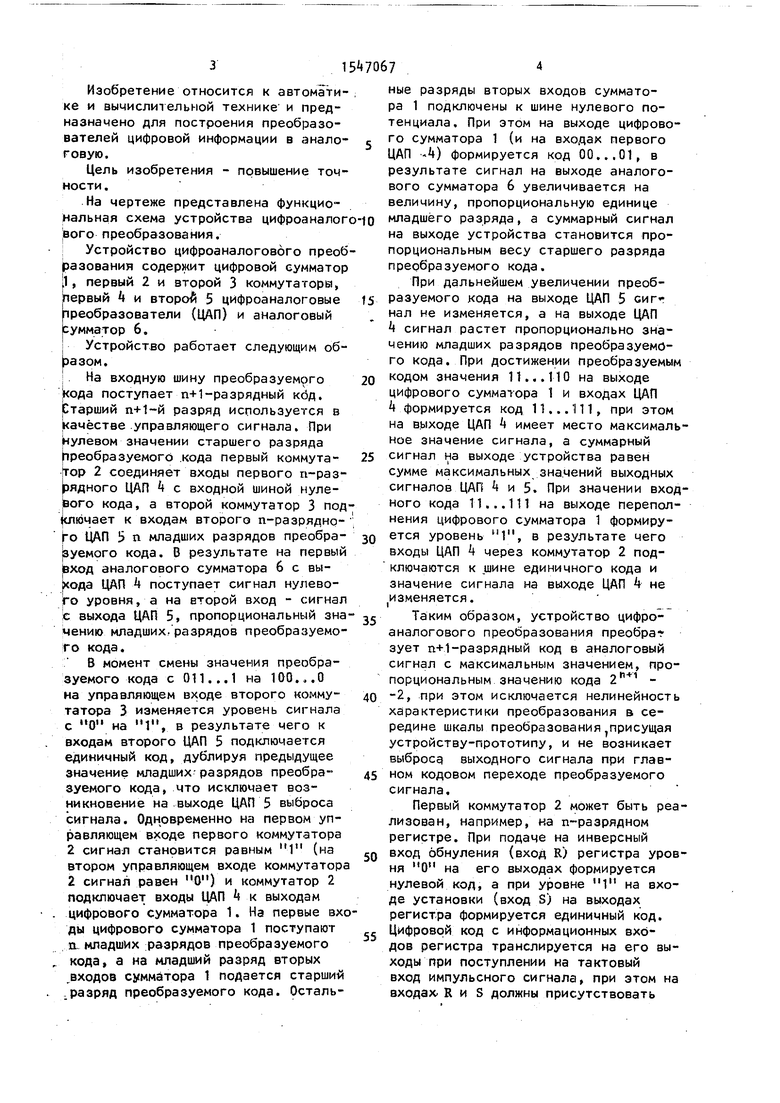

На чертеже представлена функциональная схема устройства цифроаналог вого преобразования.

Устройство цифроаналогового преобразования содержит цифровой сумматор l, первый 2 и второй 3 коммутатора, первый 4 и второй 5 цифроаналоговые преобразователи (ЦАП) и аналоговый сумматор 6.

Устройство работает следующим об- разом.

На входную шину преобразуем9го кода поступает п+1-разрядный кед. Старший n+1-й разряд используется в качестве управляющего сигнала. При Нулевом значении старшего разряда Преобразуемого кода первый коммутатор 2 соединяет входы первого п-раз- |эядного ЦАП 4 с входной шиной нуле- feoro кода, а второй коммутатор 3 подключает к входам второго п-разрядно- fo ЦАП 5 п младших разрядов преобра- |зуемого кода. В результате на первый Ьход аналогового сумматора 6 с выхода ЦАП k поступает сигнал нулевого уровня, а на второй вход - сигнал с выхода ЦАП 5, пропорциональный зна чению младших.разрядов преобразуемого кода.

В момент смены значения преобразуемого кода с 011... 1 на 100... О на управляющем входе второго коммутатора 3 изменяется уровень сигнала с О на И1, в результате чего к входам второго ЦАП 5 подключается единичный код, дублируя предыдущее значение младших разрядов преобразуемого кода, что исключает возникновение на выходе ЦАП 5 выброса сигнала. Одновременно на первом управляющем входе первого коммутатора 2 сигнал становится равным 1 (на втором управляющем входе коммутатора 2 сигнал равен О) и коммутатор 2 подключает входы ЦАП k к выходам цифрового сумматора 1. На первые входы цифрового сумматора 1 поступают п младших разрядов преобразуемого кода, а на младший разряд вторых .входов сумматора 1 подается старший разряд преобразуемого кода. Осталь

5

0

5

5

0

0

5

0

5

ные разряды вторых входов сумматора 1 подключены к шине нулевого потенциала. При этом на выходе цифрового сумматора 1 (и на входах первого ЦАП Л) формируется код 00...01, в результате сигнал на выходе аналогового сумматора 6 увеличивается на величину, пропорциональную единице младшего разряда, а суммарный сигнал на выходе устройства становится пропорциональным весу старшего разряда преобразуемого кода.

При дальнейшем увеличении преобразуемого кода на выходе ЦАП 5 сигнал не изменяется, а на выходе ЦАП k сигнал растет пропорционально значению младших разрядов преобразуемого кода. При достижении преобразуемым кодом значения П...110 на выходе цифрового сумматора 1 и входах ЦАП k формируется код 11... 111, при этом на выходе ЦАП А имеет место максимальное значение сигнала, а суммарный сигнал на выходе устройства равен сумме максимальных значений выходных сигналов ЦАП k и 5. При значении входного кода 11... 111 на выходе переполнения цифрового сумматора 1 формируется уровень 1, в результате чего входы ЦАП k через коммутатор 2 подключаются к шине единичного кода и значение сигнала на выходе ЦАП 4 не (изменяется.

Таким образом, устройство цифро- аналогового преобразования преобра зует n-Н-разрядный код в аналоговый сигнал с максимальным значением, пропорциональным значению кода - -2, при этом исключается нелинейность характеристики преобразования в середине шкалы преобразования присущая устройству-прототипу, и не возникает выброса, выходного сигнала при главном кодовом переходе преобразуемого сигнала.

Первый коммутатор 2 может быть реализован, например, на п-разрядном регистре. При подаче на инверсный вход обнуления (вход R) регистра уровня О на его выходах формируется нулевой код, а при уровне 1 на входе установки (вход S) на выходах регистра формируется единичный код. Цифровой код с информационных входов регистра транслируется на его выходы при поступлении на тактовый вход импульсного сигнала, при этом на входах- R и S должны присутствовать

сигналы 1 и О соответственно. Аналогично может быть реализован и второй коммутатор 3, в данном случае не используется вход R.

Формула изобретения

15

Устройство цифроаналогового преобразования, содержащее первый и второй коммутаторы, первый и второй циф- роаналоговые преобразователи и аналоговый сумматор, выход которого является выходной шиной, а первый и второй входы подключены к выходам соответственно первого и второго цифро- аналоговых преобразователей, входы последнего из которых соединены с соответствующими выходами второго коммутатора, первые информационные входы которого являются входной шиной младших разрядов преобразуемого кода, а вторые информационные входы - входной шиной единичного кода, выходы первого коммутатора соединены с соответствующими входами первого цифроаналогового преобразователя,

-й

5470676

п.ервые информационные входы являются входной шиной нулевого кода, а первый управляющий вход объединен с управляющим входом второго коммутато-. ра, отичающееся тем, что, с целью повышения точности, в него введен цифровой сумматор, первые входы которого объединены с соответЮ ствующими первыми информационными входами второго коммутатора, вторые входы, кроме входа младшего разряда, соединены с шиной нулевого потенциала, а вход младшего разряда вто15 РЫХ входов объединен с управляющим входом второго коммутатора и является старшим разрядом входной шины преобразуемого кода, информационные выходы цифрового сумматора соедине20 ны с соответствующими вторыми информационными входами первого коммутатора, а выход переполнения соединен с вторым управляющим входом первого коммутатора, третьи информационные

25 входы которого подключены к соответствующим входам входной шины единичного кода.

Авторы

Даты

1990-02-28—Публикация

1987-11-20—Подача