Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки сложных логических блоков широкой номенклатуры.

Цель изобретения - расширение функциональных возможностей за счет обеспечения выдачи на контролируемый блок произвольных тестов большой дли- ны с возможностью их зацикливания и программного управления длительностью

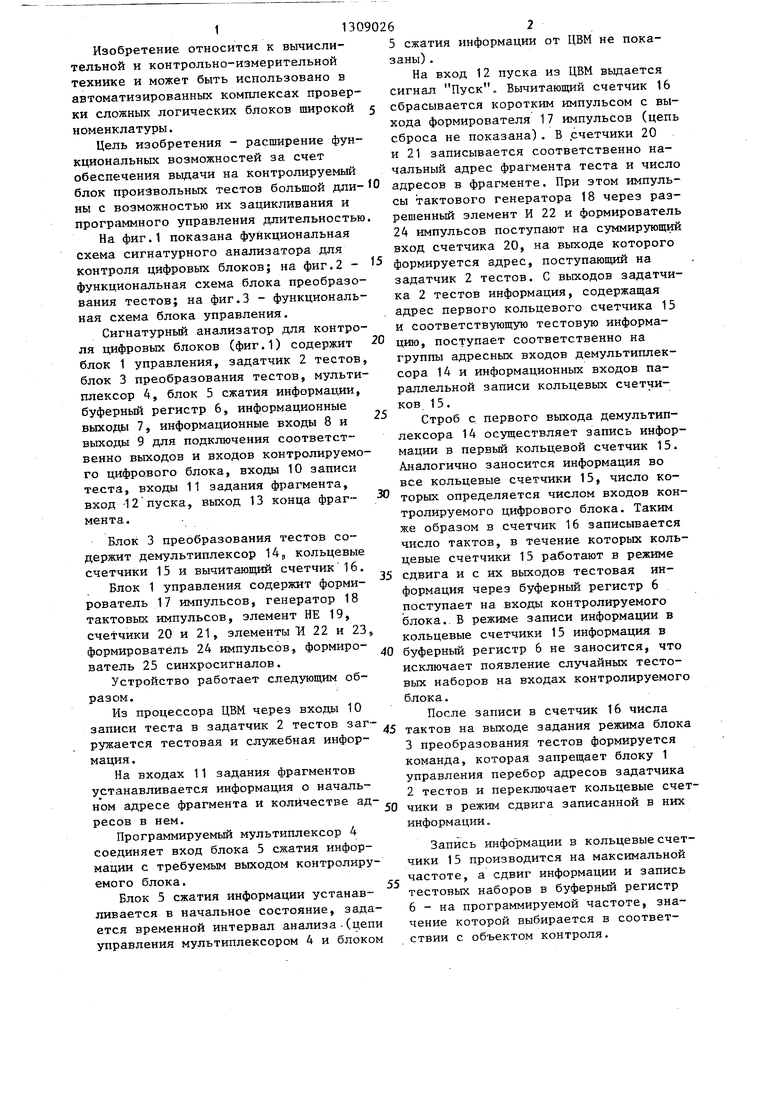

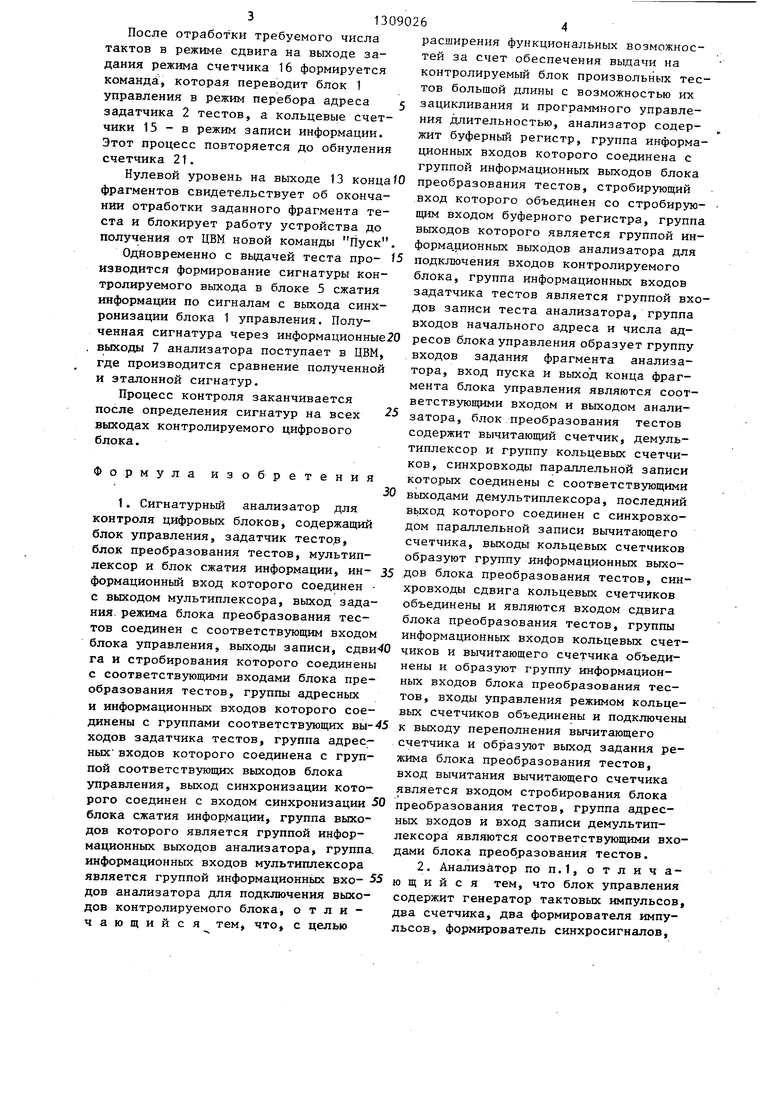

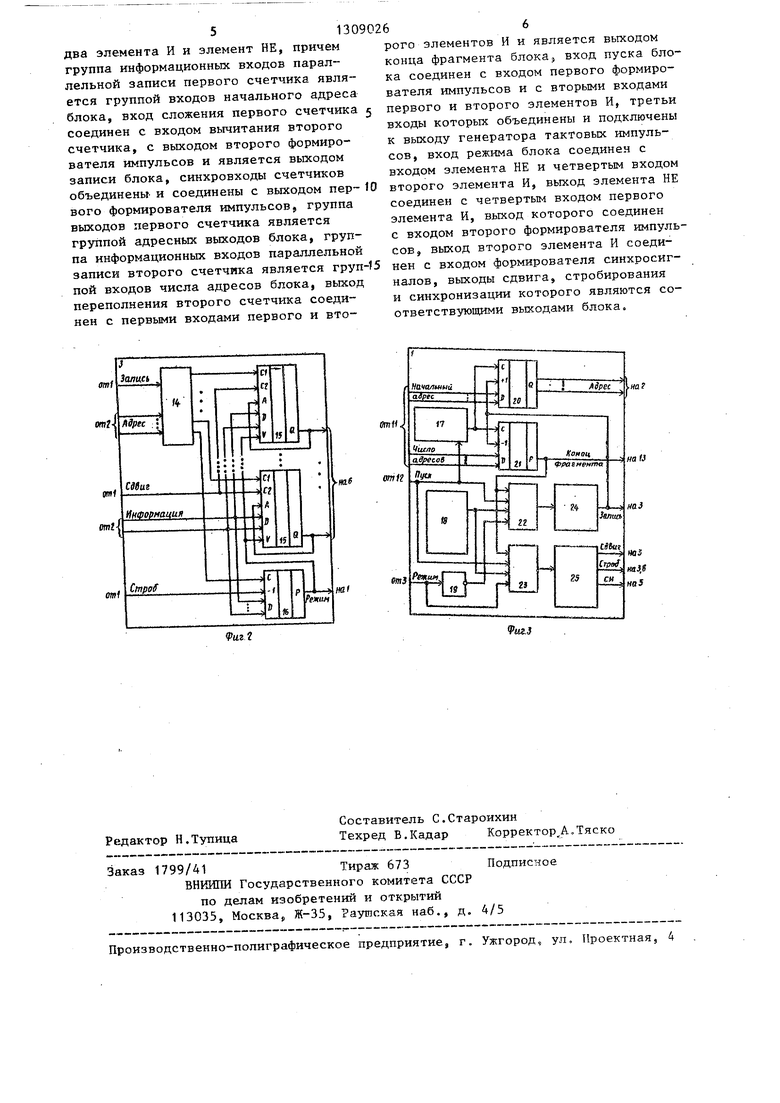

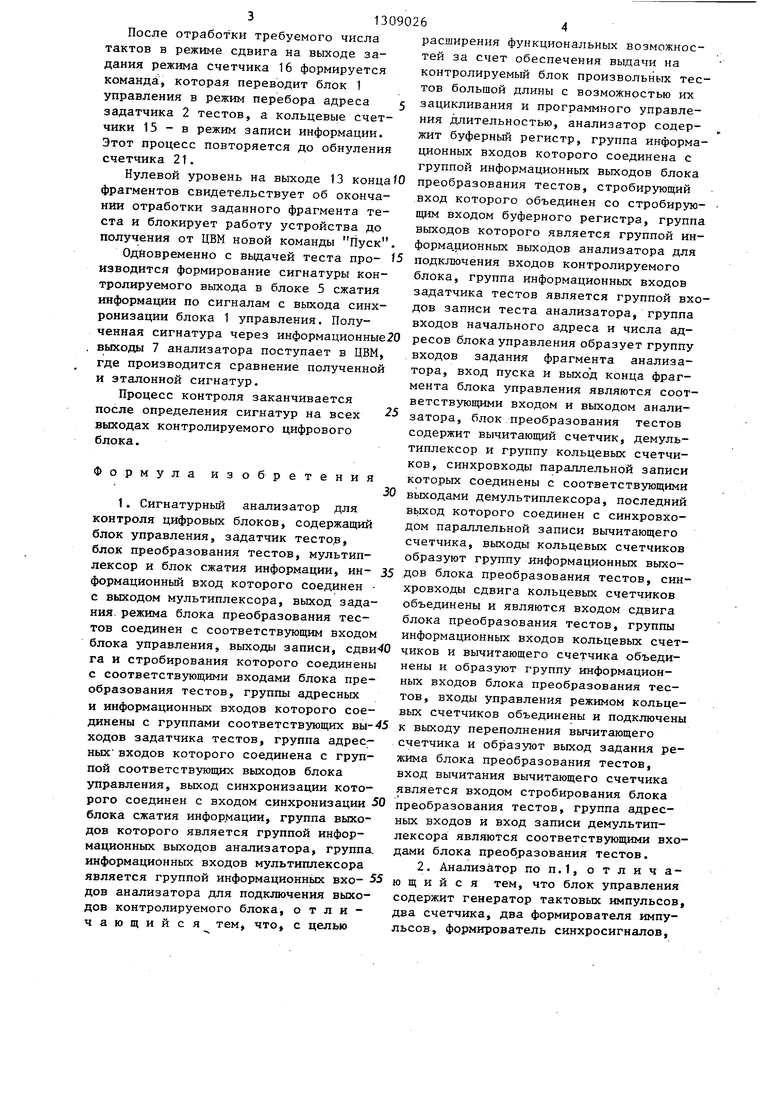

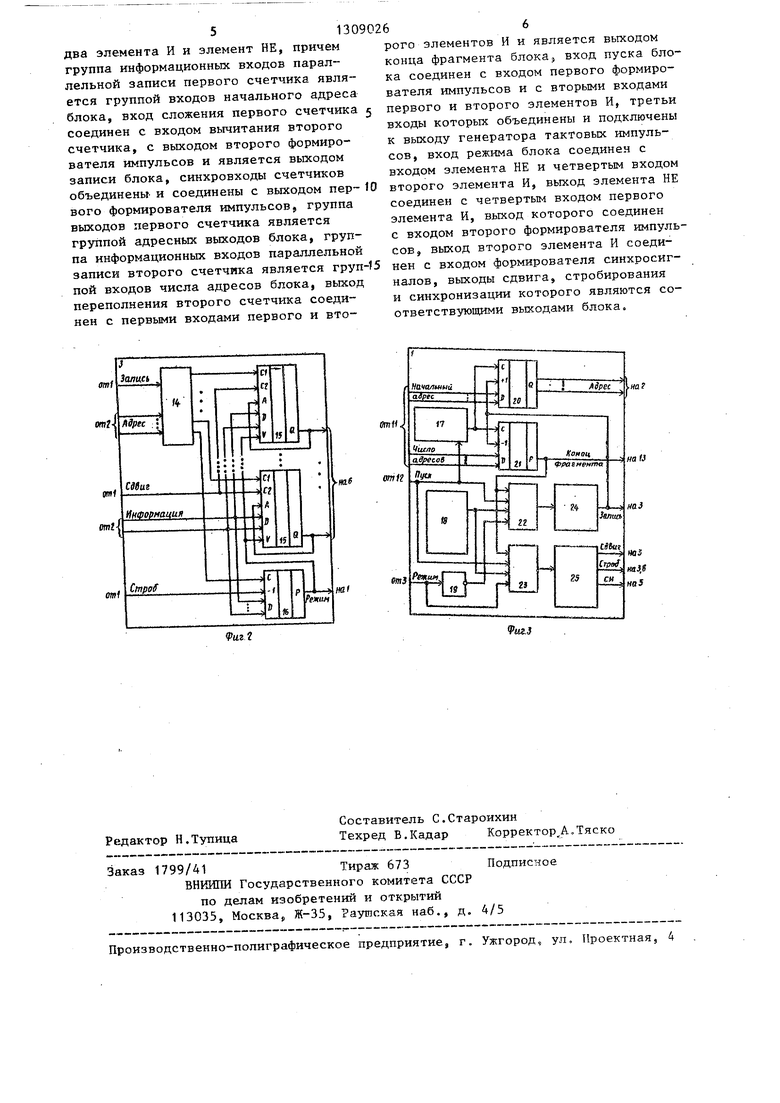

На фиг.1 показана функциональная схема сигнатурного анализатора для контроля цифровых блоков; на фиг.2 - функциональная схема блока преобразования тестов; на фиг.З - функциональная схема блока управления.

Сигнатурный анализатор для контроля цифровых блоков (фиг.1) содержит блок 1 управления, задатчик 2 тестов, блок 3 преобразования тестов, мультиплексор 4, блок 5 сжатия информации, буферный регистр 6, информационные выходы 7, информационные входы 8 и выходы 9 для подключения соответственно выходов и входов контролируемого цифрового блока, входы 10 записи теста, входы 11 задания фрагмента, вход 12 пуска, выход 13 конца фраг- мента.

Блок 3 преобразования тестов содержит демультиплексор 14,, кольцевые счетчики 15 и вычитающий счетчик 16.

Блок 1 управления содержит формирователь 17 импульсов, генератор 18 тактовых импульсов, элемент НЕ 19, счетчики 20 и 21, элементы И 22 и 23, формирователь 24 импульсов, формиро- ватель 25 синхросигналов.

Устройство работает следующим образом.

Из процессора ЦВМ через входы 10 записи теста в задатчик 2 тестов загружается тестовая и служебная информация .

На входах 11 задания фрагментов устанавливается информация о начальном адресе фрагмента и количестве адресов в нем.

Программируемый мультиплексор 4 соединяет вход блока 5 сжатия информации с требуемым выходом контролируемого блока.

Блок 5 сжатия информации устанавливается в начальное состояние, задается временной интервал анализа . (цепи управления мультиплексором 4 и блоком

5

5

О

0

.„

35

45

50

55

5сжатия информации от ЦВМ не показаны) .

На вход 12 пуска из ЦВМ выдается сигнал Цуск., Вычитающий счетчик 16 сбрасывается коротким импульсом с выхода формирователя 17 импульсов (цепь сброса не показана). В счетчики 20 и 21 записывается соответственно начальный адрес фрагмента теста и число адресов в фрагменте. При этом импульсы тактового генератора 18 через разрешенный элемент И 22 и формирователь 24 импульсов поступают на суммирующий вход счетчика 20, на выходе которого формируется адрес, поступающий на задатчик 2 тестов. С выходов задатчи- ка 2 тестов информация, содержащая адрес первого кольцевого счетчика 15 и соответствующую тестовую информацию, поступает соответственно на группы адресных входов демультиплек- сора 14 и информационных входов параллельной записи кольцевых счетчиков 15.

Строб с первого выхода демультип- лексора 14 осуществляет запись информации в первый кольцевой счетчик 15. Аналогично заносится информация во все кольцевые счетчики 15, число которых определяется числом входов контролируемого цифрового блока. Таким же образом в счетчик 16 записывается число тактов, в течение которых кольцевые счетчики 15 работают в режиме сдвига и с их выходов тестовая информация через буферный регистр 6 поступает на входы контролируемого блока.. В режиме записи информации в кольцевые счетчики 15 информация в буферный регистр 6 не заносится, что исключает появление случайных тестовых наборов на входах контролируемого блока.

После записи в счетчик 16 числа тактов на выходе задания режима блока 3 преобразования тестов формируется команда, которая запрещает блоку 1 управления перебор адресов задатчика 2 тестов и переключает кольцевые счетчики в режим сдвига записанной в них информации.

Запись инфо рмации в кольцевые счетчики 15 производится на максимальной частоте, а сдвиг информации и запись тестовых наборов в буферный регистр

6- на программируемой частоте, значение которой выбирается в соответствии с объектом контроля.

После отработки требуемого числа тактов в режиме сдвига на выходе задания режима счетчика 16 формируется команда, которая переводит блок 1 управления в режим перебора адреса 5 задатчика 2 тестов, а кольцевые счетчики 15 - в режим записи информации. Этот процесс повторяется до обнуления счетчика 21.

Нулевой уровень на выходе 13 конца/О фрагментов свидетельствует об окончании отработки заданного фрагмента теста и блокирует работу устройства до получения от ЦВМ новой команды Пуск.

Одновременно с вьщачей теста про- 15 изводится формирование сигнатуры контролируемого выхода в блоке 5 сжатия информации по сигналам с выхода синхронизации блока 1 управления. Полученная сигнатура через информационные20 выходы 7 анализатора поступает в ЦВМ, где производится сравнение полученной и эталонной сигнатур.

Процесс контроля заканчивается после определения сигнатур на всех выходах контролируемого цифрового блока.

25

Формула изобретения

1. Сигнатурный анализатор для контроля цифровых блоков, содержащий блок управления, задатчик тесто.в, блок преобразования тестов, мультиплексор и блок сжатия информации, информационный вход которого соединен с выходом мультиплексора, выход задания, режима блока преобразования тестов соединен с соответствующим входом

блока управления, выходы записи, сдви-40 чиков и вычитающего счетчика объеди- га и стробирования которого соединены с соответствующими входами блока преобразования тестов, группы адресных и информационных входов которого соенены и образуют группу информационных входов блока преобразования тестов, входы управления режимом кольцевых счетчиков объединены и подключены

динены с группами соответствующих вы-45 к выходу переполнения вычитающего

ходов задатчика тестов, группа адрес ных входов которого соединена с группой соответствующих выходов блока управления, выход синхронизации которого соединен с входом синхронизации 50 блока сжатия информации, группа выходов которого является группой информационных выходов анализатора, группа, информационных входов мультиплексора

счетчика и образуют выход задания режима блока преобразования тестов, вход вычитания вычитающего счетчика является входом стробирования блока преобразования тестов, группа адресных входов и вход записи демультиплексора являются соответствующими входами блока преобразования тестов.

2. Анализатор поп.1, отличаявляется группой информационных вхо- 55 ю щ и и с я тем, что блок управления

дов анализатора для подключения выходов контролируемого блока, отличающийся тем, что, с целью

5

/О

5 0

5

0

5

расширения функциональных возможностей за счет обеспечения выдачи на контролируемый блок произвольных тестов большой длины с возможностью их зацикливания и программного управления длительностью, анализатор содержит буферный регистр, группа информационных входов которого соединена с группой информационных выходов блока преобразования тестов, стробирующий вход которого объединен со стробирую- щим входом буферного регистра, группа выходов которого является группой ин- форма.ционных выходов анализатора для подключения входов контролируемого блока, группа информационных входов задатчика тестов является группой входов записи теста анализатора, группа входов начального адреса и числа адресов блока управления образует группу входов задания фрагмента анализатора, вход пуска и выход конца фрагмента блока управления являются соответствующими входом и выходом анализатора, блок преобразования тестов содержит вычитающий счетчик, демуль- типлексор и группу кольцевых счетчиков, синхровходы параллельной записи которых соединены с соответствующими выходами демультиплексора, последний вЬ1ход которого соединен с синхровхо- дом параллельной записи вычитающего счетчика, выходы кольцевых счетчиков образуют группу информационных выходов блока преобразования тестов, синхровходы сдвига кольцевых счетчиков объединены и являются входом сдвига блока преобразования тестов, группы информационных входов кольцевых счетчиков и вычитающего счетчика объеди-

нены и образуют группу информационных входов блока преобразования тестов, входы управления режимом кольцевых счетчиков объединены и подключены

счетчика и образуют выход задания режима блока преобразования тестов, вход вычитания вычитающего счетчика является входом стробирования блока преобразования тестов, группа адресных входов и вход записи демультиплексора являются соответствующими входами блока преобразования тестов.

2. Анализатор поп.1, отличасодержит генератор тактовых импульсов, два счетчика, два формирователя импульсов, формирователь синхросигналов.

два элемента И и элемент НЕ, причем группа информационных входов параллельной записи первого счетчика является группой входов начального адреса блока, вход сложения первого счетчика j соединен с входом вычитания второго счетчика, с выходом второго формирователя импульсов и является выходом записи блока, синхровходы счетчиков объединены- и соединены с выходом пер-tO вого формирователя импульсов, группа выходов первого счетчика является группой адресных выходов блока, группа информационных входов параллельной записи второго счетчика является груп-15 пой входов числа адресов блока, выход переполнения второго счетчика соединен с первыми входами первого и второго элементов И и является выходом конца фрагмента блокаj вход пуска блока соединен с входом первого формирователя импульсов и с вторыми входами первого и второго элементов И, третьи входы которых объединены и подключены к выходу генератора тактовых импульсов, вход режима блока соединен с входом элемента НЕ и четвертым входом второго элемента И, выход элемента НЕ соединен с четвертым входом первого элемента И, выход которого соединен с входом второго формирователя импульсов, выход второго элемента И соединен с входом формирователя синхросигналов, выходы сдвига, стробирования и синхронизации которого являются соответствующими выходами блока.

utt

етИ

впП

Риг.}

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1984 |

|

SU1270773A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных комплексах проверки сложных логических блоков широкой номенклатуры. Цель изоб1112 « 1-1 1 f V w./ ретения - расширение функциональных возможностей за счет обеспечения выдачи на контролируемый блок произво-- льных тестов большой длины с возможностью их зацикливания и программного управления длительностью. Анализатор содержит блок 1 управления, задатчик 2 тестов, блок 3 преобразования тестов, мультиплекстор 4, блок 5 сжатия информации, буферный регистр 6. В устройстве имеется возможность оперативно изменять вьщачу определенного фрагмента теста. 1 з.п. ф-лы, 3 ил. А s (Л i б 4 1:4 со о QD О ьо О5

Редактор Н,Тупица

Составитель С.Староихин

Техред Б.Кадар Корректор,А,Тяско

Заказ 1799/41Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Авторы

Даты

1987-05-07—Публикация

1984-06-14—Подача