. . -.Г ИэобреГениё огносигся к вычиспигель яой технике н может .быть использовано;. пря проектярованяя вычислятельных сно тем, . . .; Известно устройство свяэя шян, со держащее набор пассявных шян, соедянейных двусторонними связями с модулями вычяслятельной системы, блоки управле няя шинамя я блок связи шяя 0- Недостатком этого устройства является момви полязацяя объединенных шин на период передачи сообщения между парой.мойуяой что снижает пропускную способность M«N. дулей. Известно также устройство овяэк оЬ- держащее набор пассивных шяя даяяы01|а|1 реса, управ 1енвя,, соединен«1ое двуего| ои ними связямя с модулями вычисяятеяьйой системы,- при атом передача информадия между модулями выполняются в режяме разделения времени |2. Недостатком устройства является уве- лячеяяе временя ржвпанкя.по мере paouttреияя вычислительной сястемы. Наиболее бпвзквм к предлагаемому по технической сушностя является устройство связи, соедякэнное двустсроннимн информационными и командными СВЯЕЗЯМВ с модулями вычислительной системы,. родерч жашее первые приемные регистры, оервые передающие регистры, первый набор пассявных шин данных, адреса в управления блок синхронизадяи, pacnpeдeляvl reira ямпупьсов, узлы вентилей первые узлы ааализа регистры афеса, утфавпяю(Вие р истры, первые буферные регистры Я первые элементы ИЛИ, первые информа циовиые входы которь(х через первые приемные регистры подключены соответствено к,т рвому управляющему выходу синхронизации первым управляюшим гхо дом распределителей импульсов, первые урравляюшиё выходы которых связаны с., узлами вентилей, первые управляющие ВЦ ходы узлов вентилей подключены « упрапь вляющим входам первых передающих регистров, информа&яонные выходы которых соединены через первый набор пассявных шин данных, адреса я управления связаны соогветсгвейно с последующими первымв приемным регистрами и через первые буферные регистры соединены двусгоронними информационными связями с модулями вычислительной системы, управляющие выходы которых подключены к первым управляющим входам управляющих регистров, вторые управляющие входы которых связаны с узлами вентилей, информационные выходы управляющих регистров подключены к первым информационным вхоДбм узлов, вентилей, вторые управляющие выходы которых связ;аны с управляющими входами первых узлов анализа, первые информационные входы которых подключены к регистрам адреса и первым буферным регистрам, первые управляющие входы которьк соединены с третьими управляющий ми выходами узлов вентилей, четвертые ynравляющие выходы которых связаны с управляющими входами модулей вычислительной системы Однако, несмотря на то, что данное устройство позволяет наращивать проиа-: водительность системы, сохраняя ее регулярность, оно имеет единственный путь передачи информации, что не позволяет обеспечить высокую надежность работы. Последнее очень важно для ряда применений, особенно для системы реального времени. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что в устройство для сопряжения модулей вычислительной системы с контролем, со держащее первую группу приемных регистров, пйрвую передающих регистров блок синхронизации, группу распределителей импульсов, первую группу блоков сравненкп адреса, группу регистров адреса, группу управляющих регистров, первую группу буферньос регистров, первую группу элементов ИЛИ. ГОУППУ блоков вьфаботки управляющих сигналов, причем первый выход блока синхронизации соединён с первыми входами всех распределителей импульсов группы, второй выход блока синхронизации соединен со вторыми входами всех распределителей импульсов группы и с управляющими входами всех приемных регистров первсй группы, первы и второй выходы каждого распределителя импульсов группы соединены с первым и вторым синхронизирующими входами соогветствующего блока вьфаботки управляющих сигналов группы, первый выход кажд го блока выработки управляющих сигналов группы, соединен с управляющим входом соответствующего передающего регистра первой группы, выход каждого -К-го передающего регистра первой группы соеди- . ней с первым информационным входом 1(-го буферного регистра первой группы и с информационным входом (Х+1)-го приемного регистра первой группы, второй информационный вход -k-ro буферного регистра первой группы является первым входом устройства, информационный выход каждого регистра адреса группы соединен с первым информационным входом Соответствующего блока сравнения адреса первой группы н с третьим информационным входом соответствующего буферного регистра первой группы, информационный выход каждсго приемного регистра первой группы соединен с первым входом соответствующего элемента ИЛИ первой группы и со вторым информационным входом соответствующего блока сравнения адреса первой группы, выход каждого элемента ИЛИ перЬой группы соединен с первым информационным входом соответствующего блока выработки управляющих сигналов группы, второй, третий, четвертый н питый выходы каждого блоке выработки управл5лощих сигналов группы соединены соответственно с управляющим входом соответствующих блоков сравнения а/феса первой группы, с первым управляющим «копам управляющего регистра группы, с соответствующим выходом ycTpcrftcTBa, с угфавляюшим входом соответствующего буферного регистра первой группы, информацвониый выход каждого управляющего регистра группы сое-. динен со вторым информационным входом соответствующего блока выработки управл$аощих сигналов, вторые управл5пощие входы каждого управляющего регистра образуют группу управляющих входов устройства, введены блок контроля магистрали, вторая группа приемных регистров. Группа блоков коммутации, вторая группа передающих регистровj первая, вторая и третья группы блоков обнаружения ошибок, вт-орая группа блоков сравнения адреса, вторая группа элементов ИЛИ, группа счетчиков сбоев, группа дешифраторов и вторая группа буферных регистров, причем информационные выходы последних передающих регистров первой и второй групп соединены соответственно с первым и вторым информацисмными входами, блока контроля магистрали, первый и второй управляющие входы которого соезднены соответственно с первым и вторым вькода- , мя блока синхронизации, первый и второй

внформационные выходы басва Koarpota йЪгвстрали соеаинены соотвегсгвеняо с информаанонными входами первых првемных регистров первой и втсфой групп, выход каждого приемного регисгра вторс группы соединен со вторым входом соответствующего элемента ИЛИ первой группы, с первым ннформацксжным входом соответствующего блока сравнения адреса BTqjofl группы, первь1й, , третий н четвертый входы каждого блсжа коммутации группы соединены соответственно с информационными входами соответствующего, 1фиемног«) регистра первой группы, с выходом соответствующего приемного регистра первой группы, с информационным входом соответствующего приемного регистра второй группы, с выходом соответствующего приемного регистра второй группы, управляющие входы всех приемвых регистров второй группы соединены со втqpым выходом блока синхронизации, первый и второй информационные выходы каждого блока коммутации группы со дине11ы соответственно с информационными входами соответствующих передающих реи гистрсхв первой я второй групп, инффма К80ННЫЙ выход -го передающего регистра второй группы соединен с инфс мацвонным входом (it+l)-ro приемного регвстра второй группы,, с информационным входом fc-ro буфернсмго регистра второй группы, информацишный выход каждого буферного регистра второй группы соедв- йен с пятым информационным входом соответствующего буфернсго регистра первсЛ группы, первый, второй и шестой выходы каждого блока выработки управляющих сигналов группы соединены соответственно с управляющим вхоаом соответствующего передающего регистра вторсА группы, с управляющим входом соответствующего блока сравнения адреса.второй группы в с управляющим входомбуферного регистра второй группы, информационный выход каж дого регистра а;феса группы соединен со вторым информационным входом соответствующего блока сравнения адреса второй группы, Ьыходы соответствующих блоков сравнения адреса первой и второй групп соединены с первым ° и вторым входамв соответствующего элемента ИЛИ второй группы, выход каждого элемента ИЛИ второй группы соединен с управляющим входом соответствующего управляющего регистра группы, седьмой выход каждого блока выработкой управляющих сагналов группы соединен со входом соответствующего счетчика сбоев группы, выхся каЖ(

дого счётчнка сбоев соединен с соответ-ствующвм входом дещифратора группы, выход каждого дешифратора группы соединен с третьим входом соответствующего блока вьфаботки управляющих сигналов

группы, информационные выходы каждого передающего регистра первой н второй групп соединены соответственно со входами блоков обнаружения ошибок первой

,и вторсА групп, выходы блоков обнаружения ошибок первой н вторсЛ групп соединены соответс-венно с четвертым и пятым входами соответствующего блока выработ ки управляющих сигналов группы, третий

выход и пятый вход каждого блока коммутации группы образуют соответственно первую группу информационных вьсходов в вторую группу информационных входов ус роАства, выход каждсго буферного регнстра первой группы соединен с информационным входом соответствующего блока обнаружения ошибок третьей группы и с третьим входом соответствующего блока вьфаботки управляющих сигналов группы,

выход каждого блока обнаружения ошиёок третьей группы соединен с шестым входом, соответствующего блока вьфаботкк управляющих сигналов группы.

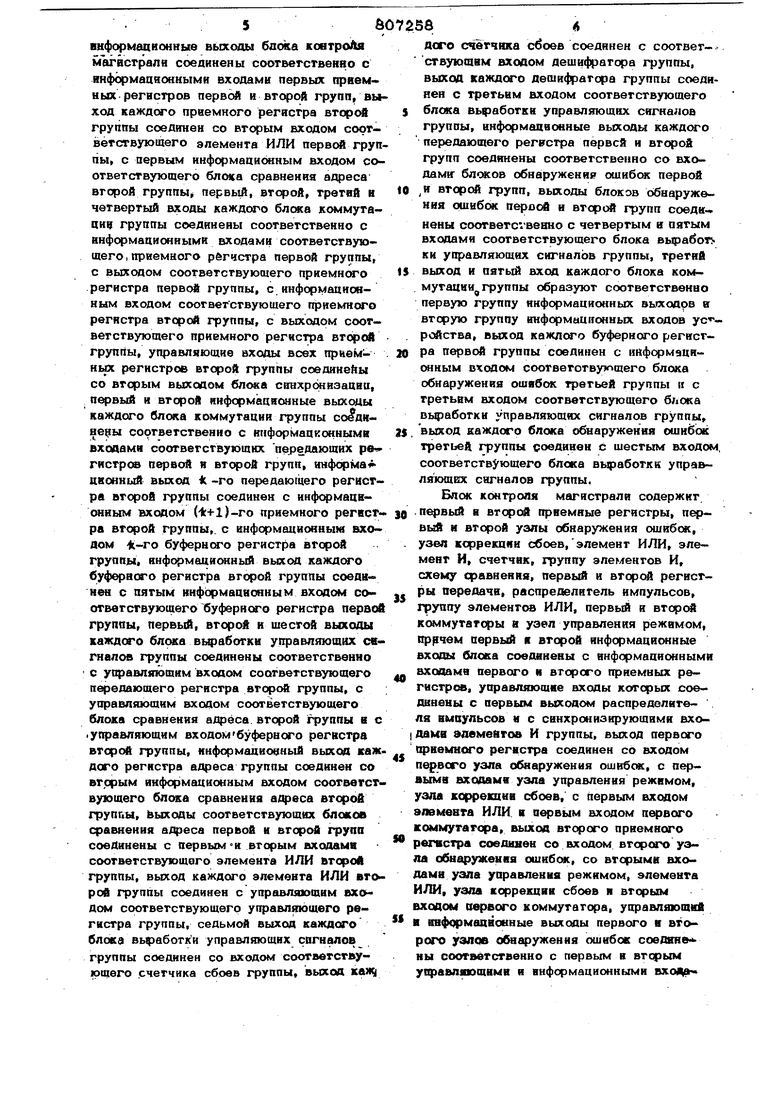

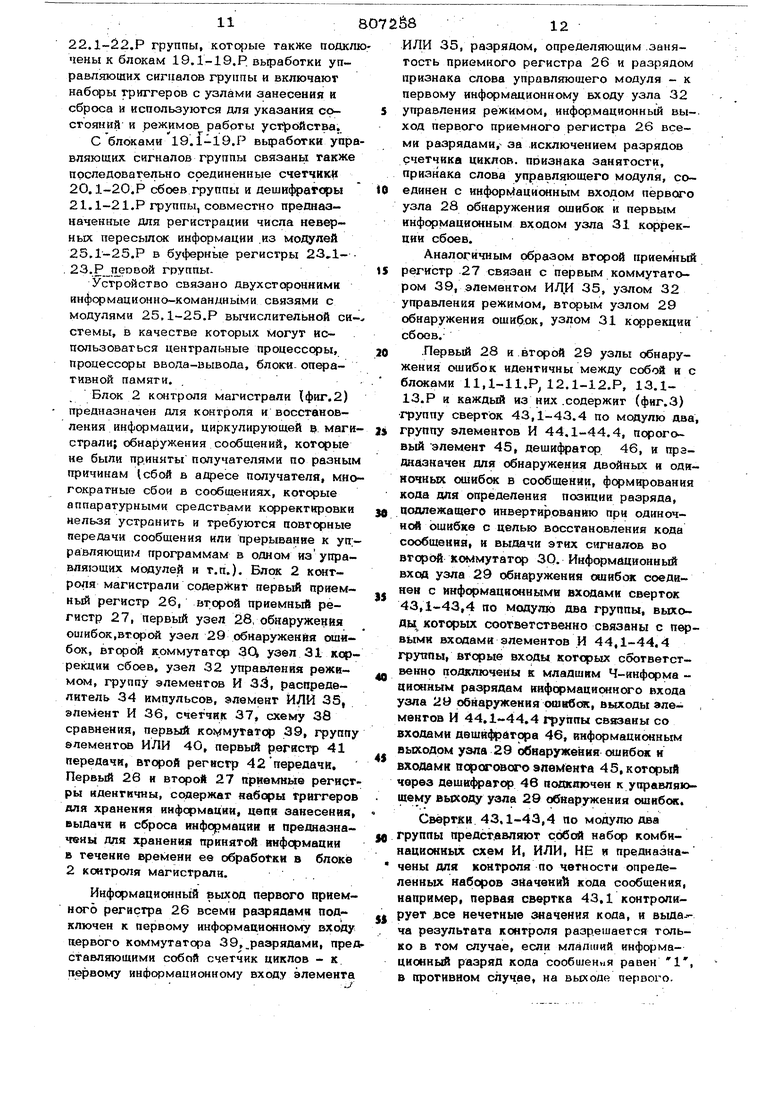

Блок контроля магистрали содержит

первый в второй приемные регистры, первый и второй узлы обнаружения ошибок, узел коррекции сбоев,элемент ИЛИ, элемент И, счетчик, группу элементов И, схему сравнения, первый и второй регистры аередачи, распределитель импульсов.

группу элементов ИЛИ, первый и вторс кснимутатфы в узел управления режимом, пррчем первый н второй информационные входы блока соединены с информационными вхооамв первого в второго приемных регистров, управляющие входы которых соединены с первым выходом распределителя вмаульсов в с синхронизирующими вхо{дамв длемейтов И группы, выход первого (фвемного регистра соединен со входом первого узла обнаружения ошибок, с первыми вхоламв узла управления режимом, узла кч;1рекцив сбоев, с первым входом элемента ИЛИ в первым входом первого коммутатора, выход второго приемного

регвстра соединен со входом вторшх узла обнаружения ошибсж, со втчэымв входамв узла управления режимом, элемента ИЛИ, узла коррекции сбоев в вторым входом первого коммутатора, управляющий

в ввформадвоыные выходы первого в второго узлов обнаружения (хиибок соедяне ны соответственно с первым и вторым у|фавляющвмв в информационными вхоца

и второго коммутатора, первый и второй , правляющие;выходы которого соединены f соответственно с управляющим входом зла кс эрекции сбоев и с первыми управяющими входами элементов И группы, ыход узла кс рекцни сбоев соединен с первыми инф эмационными входами элеентов И группы1 первый и второй выхоы узла управления режимом соединены соотвегственно со вторыми входами элементов И группы, с первыми входами элементов ИЛИ группы, первый ,второй,третий, четвертый н пятый выходы элементов И группы соединены соответственно с первым входом элемента И, с управлящим входом счетчика, со вторыми вхоами элементов ИЛИ группы, с управляющим входом первого и второго регистров передачи, с инфс мационным входом первого и второго регистров передачи, выоды которьрс являются выходами блсжа, выход элемента ИЛИ соединен со входом элемента И, выход которого соединен, со счетным входом счетчика, информационный выход очегчйка соединен со входом схемы сравнения и со вторыми инффмааноннымн входами элементов -И группы, выход схемы сравнения соединен с третьими входами элементов И группы, второй выход распределителя кмпульсоа соединен с управляющим BxoiaoM первого коммутатора, выходы элементов ИЛИ группы соединены с трегьи°м киформационным и вторым управляющим входами пер вого коммутагс а, порвый и вторсЛ выходы которого сЬеДннеиы соогвегственно со вторымв нгнформааионнымя входами первого и второго регистров передачи.

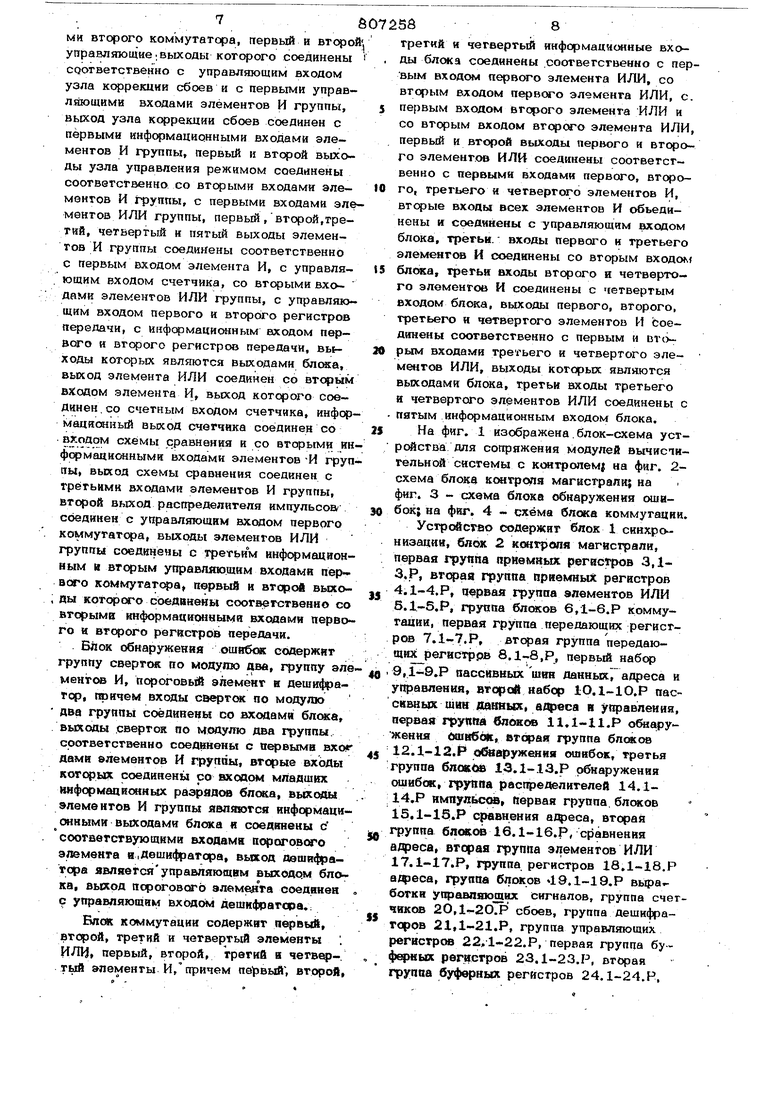

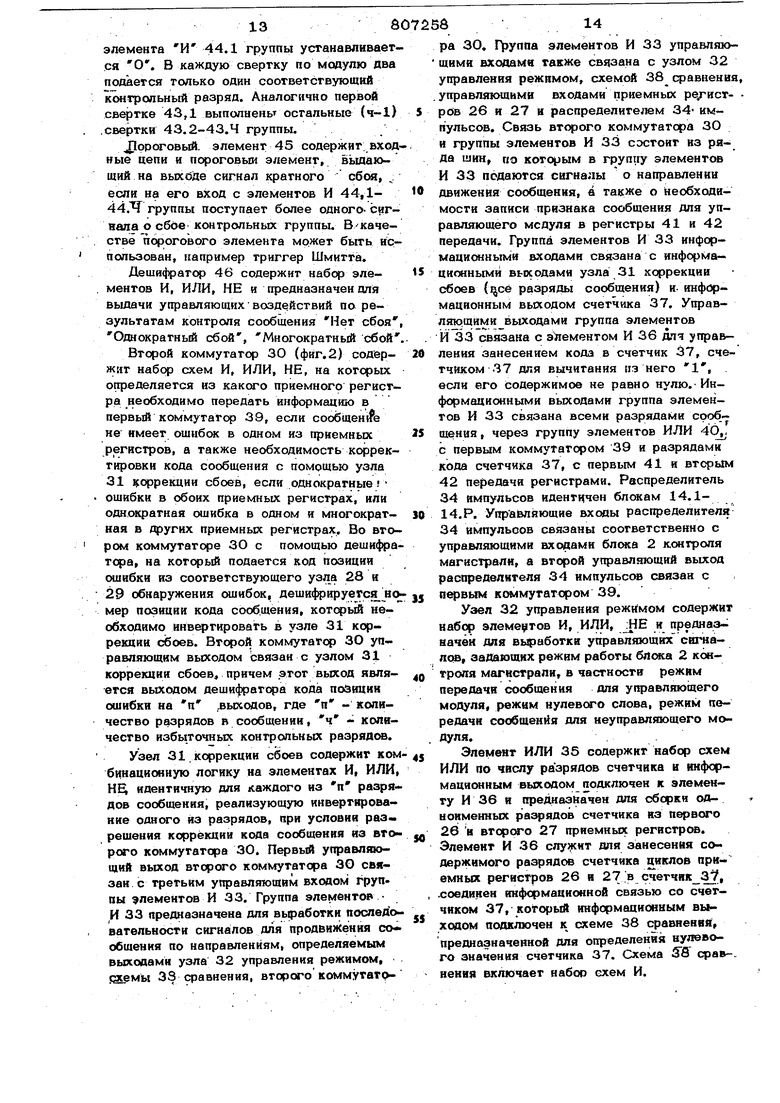

Блок обнаружения ошибок содержит группу сверток по модулю два, группу элементе И, пороговьгй элемент в деши({ратор, причем входы сверток по ыорупю два группы соединены со входами блока, выходы .сверток по модулю две группы, соответственно соединены с первыми вхог дами елементов И группы, вторые входы которых соединены со вхоаом младших ннфор мац ионных блока, выходы элементов И группы являются информационными выходами блока я соедкнены с ° соотввтствующнми входами nqjoroBoro элемента в.Дешифратора, выход оэшифратора являетсяуправляющим выходом блська, выход пороговсгЬ элемента ооедвнеа , с управляющим входом дешифратора.:

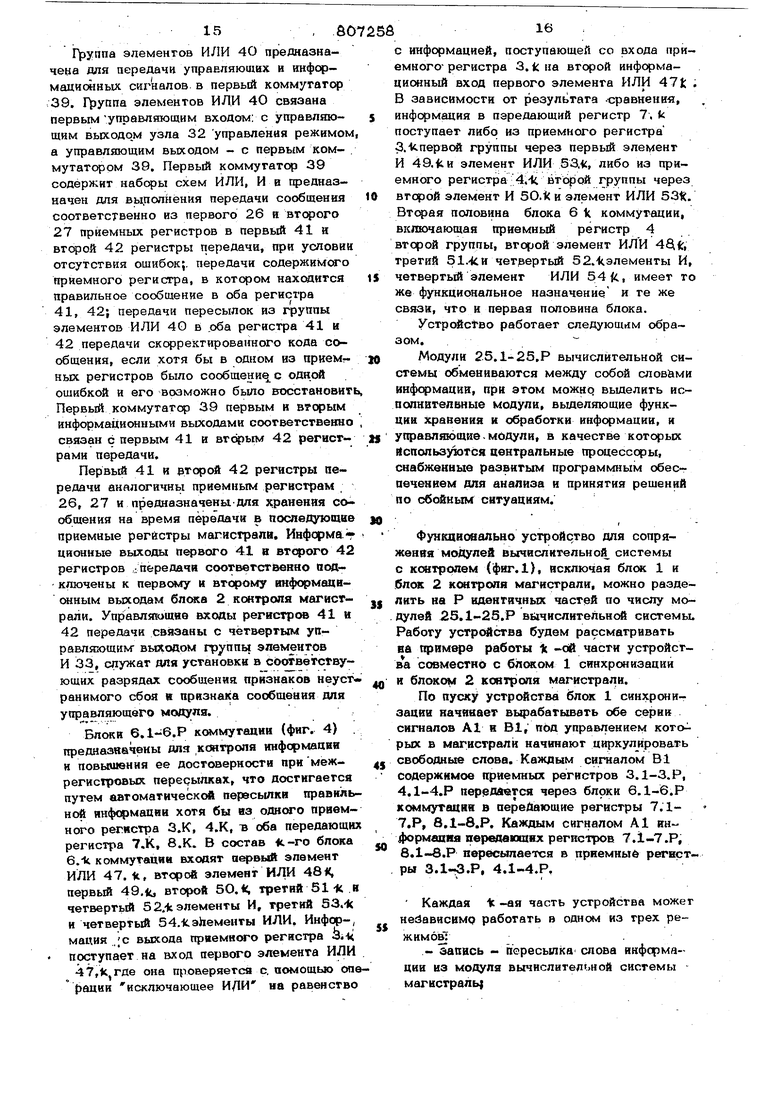

Емюак коммутации содержит первый, второй, третий и четвертый элементы ИЛИ, первый, второй, третий и четвер-. тый элементы И,причем пе1рвый, второй.

третий и четвертый информационные вхо, ды блсжз соединены соответственно с первым входом первого элемента ИЛИ, со вторым входом первого элемента ИЛИ, с.

первым входом второго элемента ИЛИ и со вторым входом втсрого элемента ИЛИ, первый и второй выходы первого и второго элементов ИЛИ соединены соответственно с первыми входами первого, второго, третьего и четвертого элементов И, втсрые входы всех элементов И объединены к соединены с управляющим .входом блока, третьи. входы первого и третьего элементов И соединены со вторым вxoдo

5 блсжа, третьи входы второго и четвертого элементов И соединены с четвертым входом блока, выходы первого, второго, третьего к четвертого элементов И fcoeдинены соответственно с первым и рым входами третьего и четвертого элементов ИЛИ, выходы которых являются выходами блока, третьи входы третьего и четвертого элементов ИЛИ соединены о пятым инфср мац ионным входом блока.

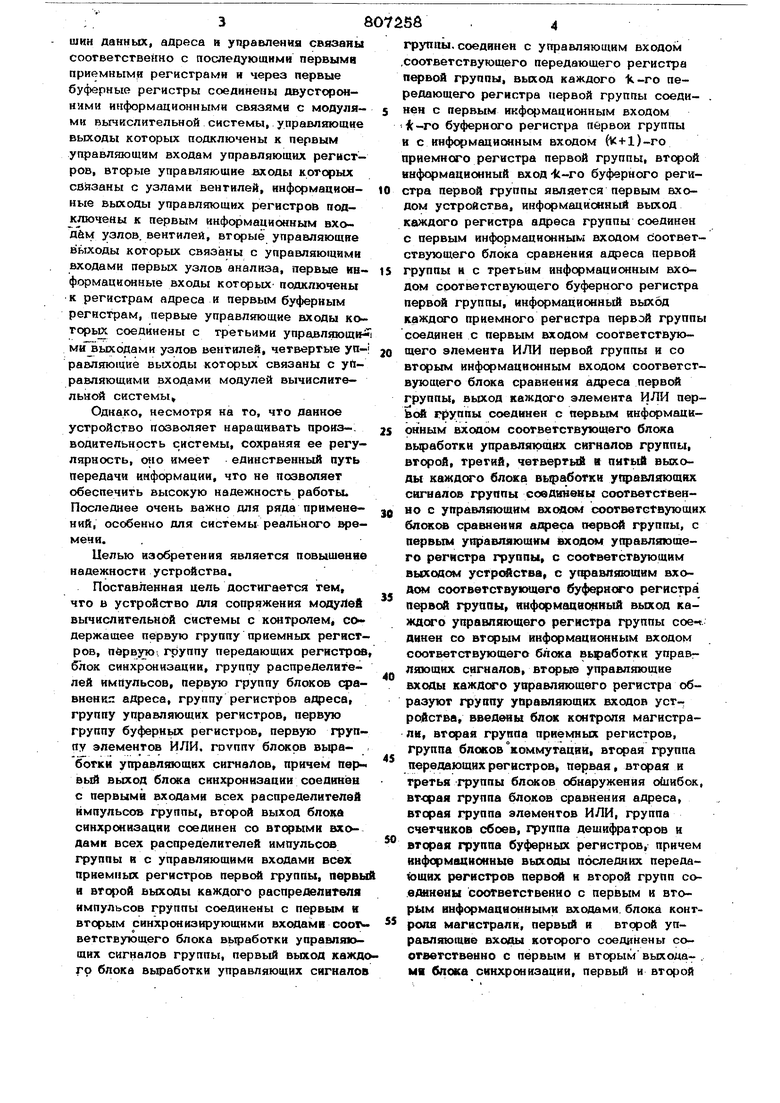

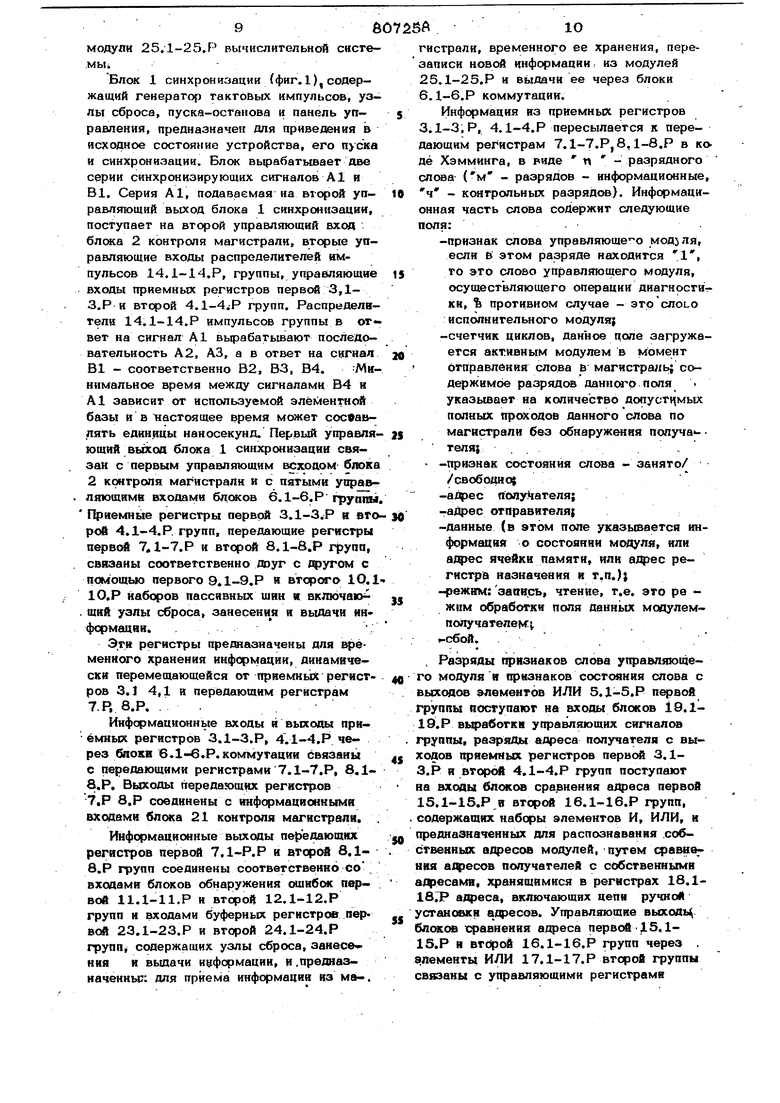

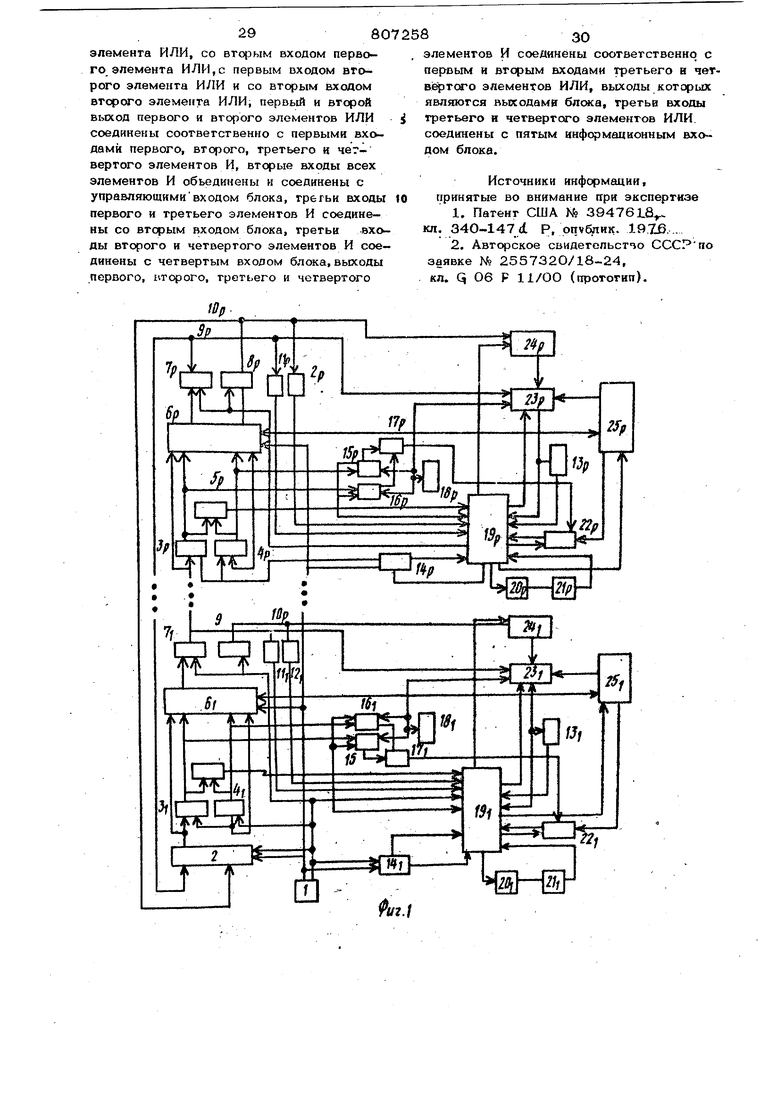

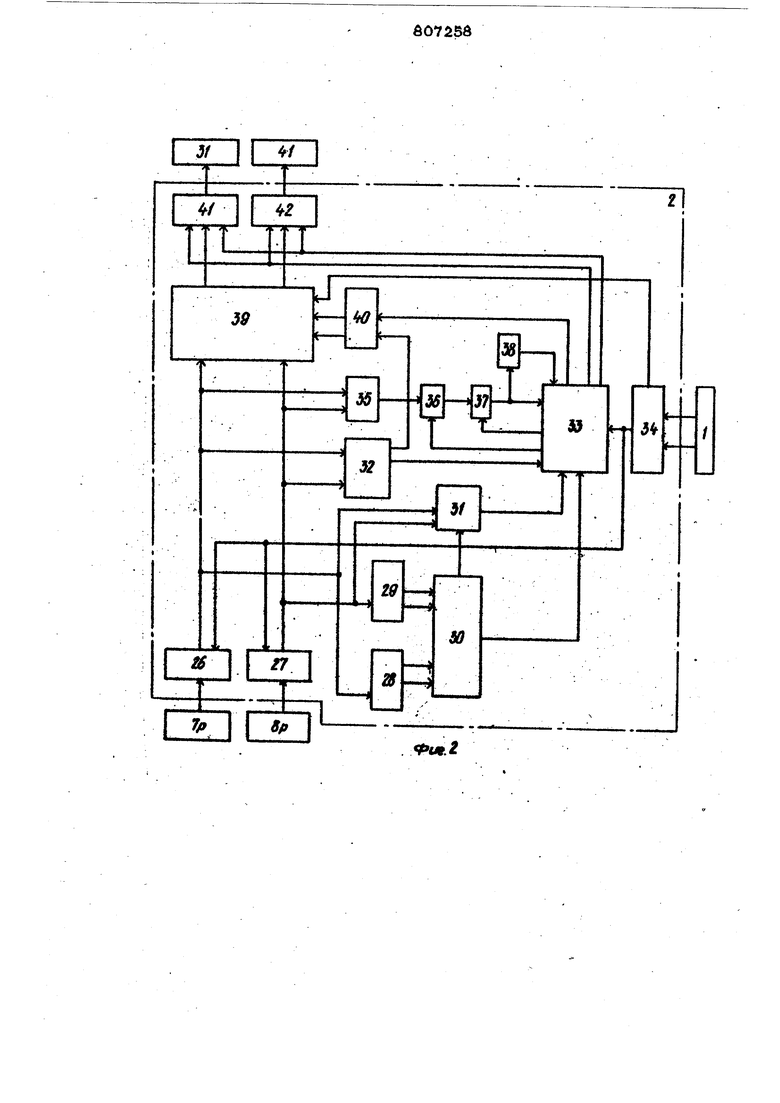

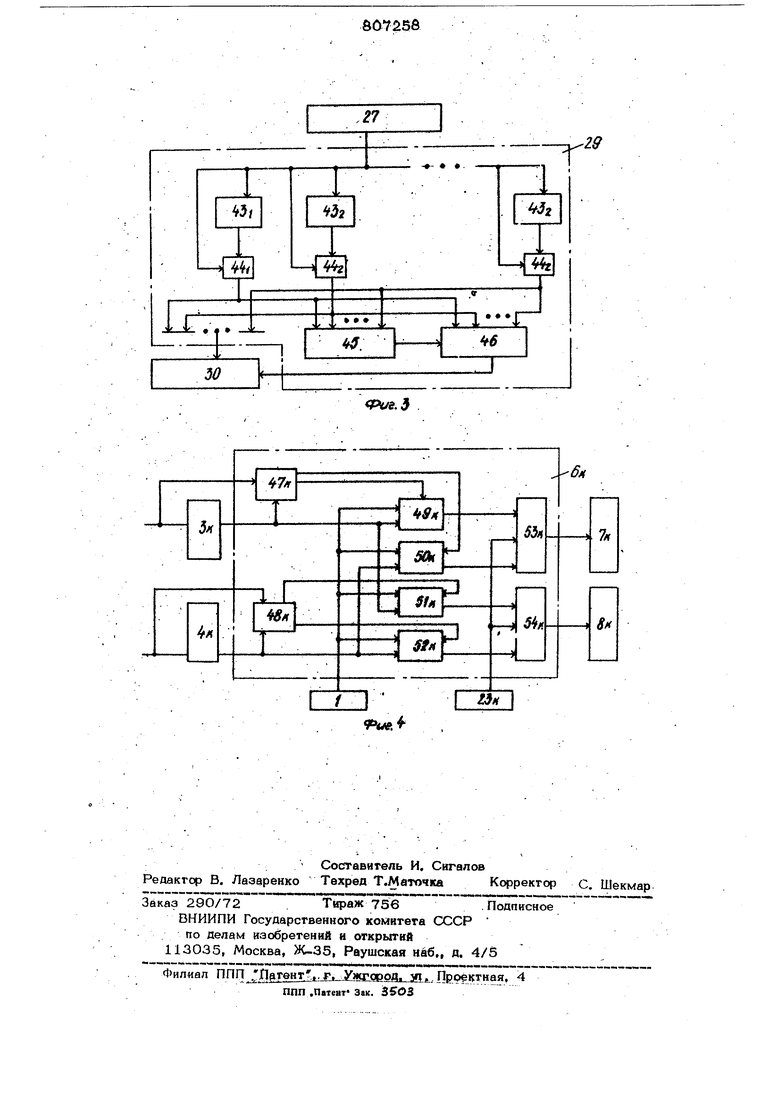

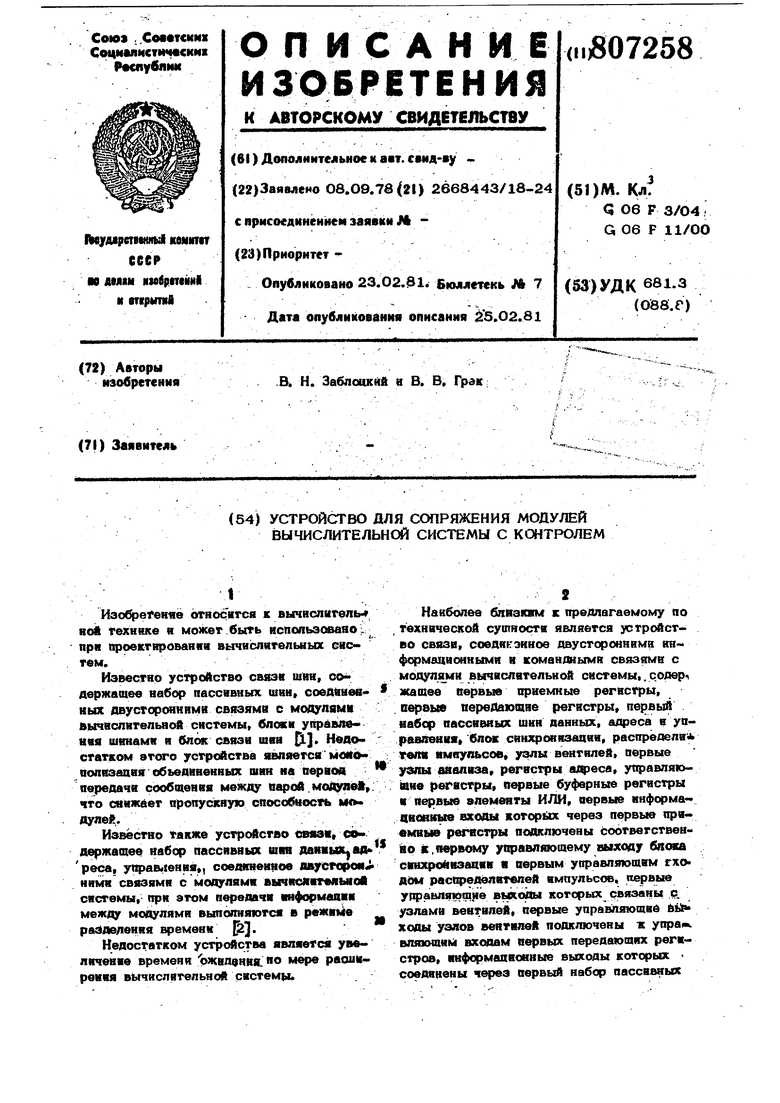

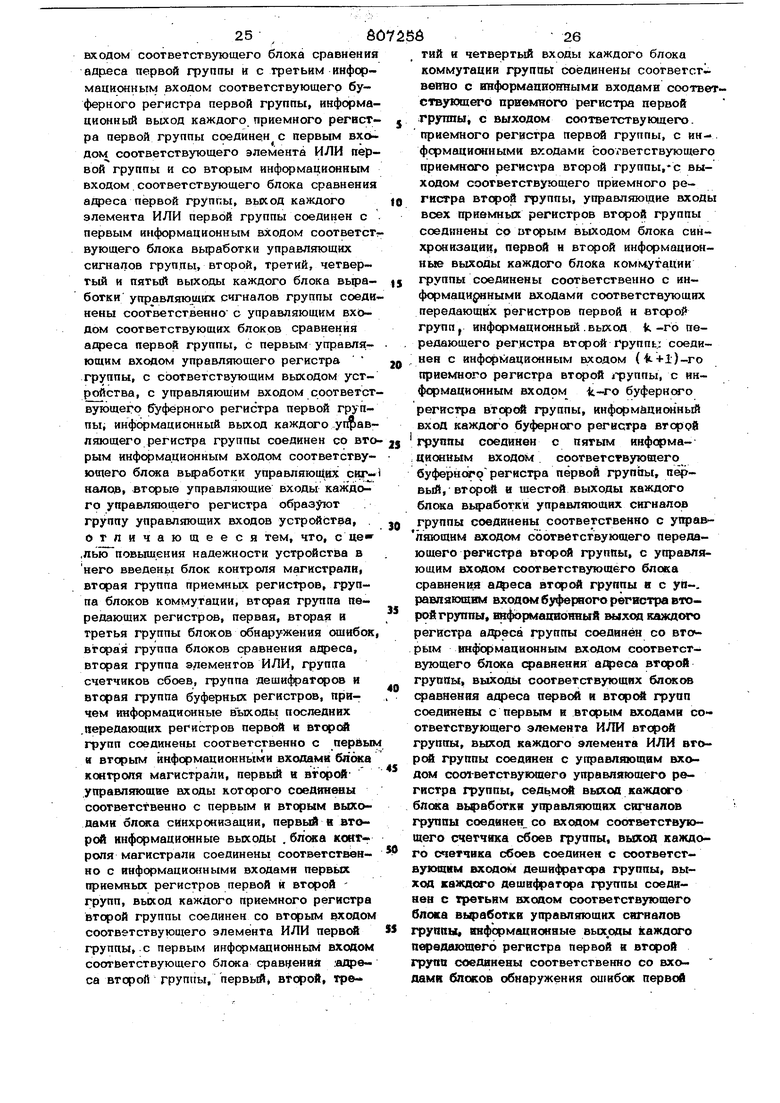

5 На фиг. 1 изображена.блок-схема устройства для сопряжения модулей вычиспительной Системы с к 1тролем| на фиг. 2схема блоке коятроля магистрали; на фиг. 3 - схема блока обнаружения ошио бок; на фиг. 4 - схема блока коммутации.

Устройсуво содержит блок 1 синхронизации, блох 2 KOHTp nfi магистрали, первая группа приемных регистров 3,1З.Р, втфая группа приемных регистров

, 4.1-4.Р, первая элементов ИЛИ 6.1-5.Р, группа блсжов 6,1-6.Р коммутации, первая группа передающих регистров 7Л-7.Р, вторая группа передающих регйСТ|зрв 8.1-8,Р, первый набор

8 пассивных lumi данных адреса и управления, второй набор 1О.1-1О.Р пассивных шин Двнвьес, вфеса и управления, первая группа вткуков И,1-11.Р обнаружевия miti6, втфая группа бпоков

j 12.1-12.Р обваружения ошибок, третья группа 15.1-13.Р обнаружения ошибок, группа распределителей 14.114,Р нмпулыхшг первая группа, блсжов 15. l-lSi.P сравнения , вторая

- ipynna le. 1-16.Р, сравнения адреса, вторая группа элементов ИЛИ 17.1-17.Р, группа регистров 18.1-18.Р , группа блоков 49.1-19.Р вьфа.боткн управашо их сигналов, группа счетчиков 20,1-20.Р сбоев, группа дешифраторов 21,.Р, группа управляющих регистров 22,1-22.Р, первая группа рег.исгров 23.1-23.Р, вторая группа буферных регистров 24.1-24.Р,

модули 25,1-25.F вычислительной систе.MbliБлок 1 синхронизации (фиг.I), содержащий генерат() тактовых импульсов, узлы сброса, пуска-останова н панель управления, предназначен для приведения в исходное состояние устройства, его пуска и синхронизации. Блок вырабатывает две серии синхронизирующих сигналов А1 и В1. Серия А1, подаваемая на второй управляющий выход блока 1 синхронизации, поступает на второй управляющий вход блока 2 контроля магистрали, вторые управляющие входы распределителей импульсов 14.1-14,Р, группы, управляющие входы приемных регистров первсЛ 3,1З.Р и 4.1-4iP групп. Распределители 14.1-14.Р импульсов группы в ответ на сигнал А1 вырабатывают последовательность А2, A3, а в ответ на сигнал В1 - соответственно В2, ВЗ, В4. Минимальное время между сигналами В4 и А1 зависит от используемой элементной базы и в настоящее время может сосфавлять единицы наносекунд. Первый управляющий выход блока 1 синхронизации связан с первым управляющим всхоаом блока 2 контроля магистрали и с пятыми уоравлтощими входами блсжов 6.1-6.Р группй

Г иемные регистры первой 3.1-З.Р и вто рой 4.1-4.Р. групп, передающие регистры первой 7,1-7.Р и второй 8.1-8.Р групп, связаны соответственно доуг с Щ)угам с помощью первого 9.1-9.Р и второго 1О,110,Р наборов пассивных щин и включаю

. щий узлы сброса, занесени я и выдачи информации. ,;

Этн регистры претазначены для временного хранения информации, динамически перемещающейся от приемных регистров 3.1 4,1 и передающим регистрам 7.Р, 8.Р. ..

Информационные входы и выходы при ёмньос регистров 3.1-З.Р, 4.1-4.Р через блоки 6.1-6.Р. коммутации связаны О передающими регистрами 7.1-7.Р, 8.18.Р, Выходы передающих регистров

7,Р 8,Р соединены с информационными входами блсжа 21 контроля магистрали.

Информационные выходы передающих регистров первсй 7.1-Р.Р и вторс 8,18,Р групп соединены соответственно со входами блоков обнаружения ощибсж первой 11.1-11,Р и второй 12.1-12.Р групп и входами буферных регистре первой 23Л-23.Р и второй 24.1-24.Р групп содержащих узлы сброса, занесения и вьшачи информации, и.предназначенньс: для приема информации из ма-.

гистрали, временного ее хранения, перезаписи новой информации из модулей 25.1-25.Р и вь1Дачи ее через блоки 6.1-6.Р коммутации.

Информация из приемных регистров 3.1-3,Р, 4.1-4.Р пересылается к передающим регистрам 7.1-7.Р, 8,1-8.Р в кде Хэмминга, в виде п - разрядного слова См - разрядов - информационные ч - контрольных разрядов). Информационная часть слова содержит следующие поля:

-признак слова управляюще о модуля, если е этом разряде находится , то это слово управляющего модуля, осуществляющего операции диагностики, Ъ противном случае - это слои о исполнительного модуля; -счетчик циклов, данное п.опе загружается активным модулем в момент отправления слова в магистраль; содержимое разрядов даннса-р поля . указывает на количество допустимых полных проходов данного слова по магистрали без обнаружения попуча теля{ ,- -признак состояния слова - занято/

/свободно; -аарес получателя; -аДрес отправителя; -данные (в этом поле указывается информация о состоянии модуля, или ащюс ячейки памяти, или адрес регистра назначения и т.п.)} -режим: запись, чтение, т.е. это ре жнм обработки поля данньис мооулемпопучателек. сбой.

Разряды признаков слова утфавляющего модуля и признаков состояния слова с выходов элементов ИЛИ 5.1-5.Р первой группы поступают на входы блоков 19.119.Р выработки управляющих сигналов группы, разряды адреса получателя с выходов приемных регистров первс 3.1З.Р и вторЫ1 4.1-4.Р групп поступают на входы блоков сравнения адреса первой 15.1-15. второй 16.1-16.Р групп, , содержащих наборы элементов И, ИЛИ, и предназначенных для распознавания .собственных адресов модулей, путем сравне ВИЯ а;Ц}есов получателей с собственными афесами, хранящимися в регистрах 18.118ГР адреса, включающих цеПи ручной установки адресов. Управляющие вьасслц блсжов х:равнения адреса первсА ;15.115.Р и BTdpoft 16.1-16.Р групп через . элементы ИЛИ 17.1-17.Р второй группы связаны с управляющими регистрами 22.1-22.Р группы, котфые также подклю чены к блокам 19.1-19.Р выработки управляющих сигналов группы и включают триггеров с узлами занесения и сброса и используются для указания состояний и режимов работы уст зойства. С блоками 19.1-19.Р выработки упра вляющих сигналов группы связаны также последовательно соединенные счетчики 20.1-20.Р сбоев группы и деши4ч5аторы 21.1-21.Р группы, совместно предназначенные для регистрации числа неверных пересылок информации .из модулей 25Л-25.Р в буферные регистры 23,1- 23.Р пеовой группыУстройство связано двухсторонними информационно-командными связями с модулями 25,1-25.Р вычислительной системы, в качестве которых могут использоваться центральные процессоры, процессоры ввода-иывода, блоки-оперативной памяти. . Блок 2 ко11гроля магистрали 1фиг,2) предназначен для контроля и восстановления информации, циркулирующей е магистрали; обнаружения сообщений, которые не были пр.иняты получателями по разным причинам (сбой в адресе получателя, мно гократные сбои в сообщениях, которые аппаратурными средствами кqэpeктиpoвки нельзя устранить и требуются повторные передачи сообщения или прерывание к уп;равляющим программам в одном изуправляющих модулей и т.п.). Блок 2 контроля магистрали содержит первый приемный регистр 26, второй приемный регистр 27, первый узел 28, обнаружения ошибок,вгорсй узел 29 обнаружения ошибок, второй коммутатор 3Q узел 31 коррекции сбоев, узел 32 управления режимом, группу элементов И ЗЗ, распределитель 34 импульсов, элемент ИЛИ 35, элемент И 36, счетчик 37, схему 3S сравнения, первьй коммутатф 39, группу элементов ИЛИ 40, первый регистр 41 передачи, второй регистр 42передачи. Первый 26 и второй 27 приемные регист ры идентичны, содержат наборы триггеров для хранения информации, цепи занесения, выдачи и сброса информации и предназначены для хранения принятой информации в течение времени ее обработки в блоке 2 контроля магистрали. Информационнь1й выход первого приемнсяб регистра 26 всеми разрядами подключен к первому информационному входу аервого коммутатора 39,раэрядами, пре ставляющими собой счетчик циклов - к первому информационному входу элемента S 812 ИЛИ 35, разрядом, определяющим .занятость приемного регистра 26 и разрядом признака слова управляющего модуля - к первому информационному входу узла 32 управления режимом, информационный вы-, ход первого приемного регистра 26 всеми разрядами, за исключением разрядов счетчика циклов, поизнака занятости, признака слова управляющего модуля, соединен с информационным входом первого узла 28 обнаружения ошибок и первым информацисиным входом узла 31 коррекции сбоев. Аналогичным образом второй приемный регистр 27 связан с первым коммутатором 39, элементом ИЛ.И 35, узлом 32 управления режимом, вторым узлом 29 обнаружения ошиб.ок, узлом 31 коррекции сбоев. .Первый 28 и второй 29 узлы обнаружения ошибок идентичны между собой и с бл{жами И,1-11.Р 12.1-12.Р, 13.113.Р и каждый из них .содержит (фиг.З) группу сверток 43,1-43.4 по модулю два, группу элементов И 44.1-44.4, nqporoвый элемент 45, дeшифpaтqз 46, и прадназначен для обнаружения двойных и одиночньсс ошибок в сообщении, формирования кода для определения позиции разряда, аодлежащего инвертированию при одиночной ошибке с целью восстановления кода сообщения, и выдачи этих сигналов во второй коммутатор 30. Информационный вход узла 29 обнаружения ошибок соединен с информационными входами сверток 43,1-43,4 по модулю два группы, выхоДЬ1 которых соответственно связаны с первыми входами элементов И 44,1-44,4 группы, втсрые входы которых соответственно подключены к младшим Ч-информа аиснным разрядам информацисмнсо о входа узла 29 обнаружения ошкбсж, выходы эле- , ментов И 44.1-44,4 группы связаны со входами двшйфрдгора 46, информационным выходом узла 29 обнаружения ошибок н входамк ворогового элемента 4 5, который через деши4фат 4в поокарчен к уоравлякцшему выходу уэла 29 обнаружения ошибок. Свертки 43.1-43,4 По модулю два группы представляют собой набор комбинационных схем И, ИЛИ, НЕ и предназначаны для контроля по четности определенных наборов зНачениТ кода сообщения, например, первая свертка 43.1 контролирует все нечетные значения кода, и выда-ча результата контроля разрешается только в том случае, если млашний информационный разряд кода сообшення равен , в (фотивном случав, на выходе первого. элемента И 44.1 группы устанавливается О. В каждую свертку по модулю два подается только один соответствующий контрольный разряд. Аналогично первой свертке 43,1 выполнены остальные (ч-1) .свертки 43.2-43.Ч группы. Д1рроговый. элемент 45 содержит вход ные цепи и пороговьш элемент, вьшающий на вькбде сигнал кратного сбоя, : если на его вход с элементов И 44,144 группы поступает более одного- сигнала о сбое контрольных группы. В качестве порогового элемента может быть использован, например триггер Шмитта. Дешифратор 46 содержит набор эле. ментов И, ИЛИ, НЕ и предназначен для выдачи управляющих воздействий по результатам контроля сообщения Нет сбоя Однократный сбой , Многократный сбой Второй коммутатор 30 (фйг.2) содержит набор схем И, ИЛИ, НЕ, на которых определяется из какого приемного регистра необходимо передать информацию в первый коммутатор 39, если сообщен{ е не имеет ошибок в одном из приемных регистров, а также необходимость ко|эректировки кода сообщения с помощью узла 31 коррекции сбоев, если однократньге ошибки в обоих приемных регистрах, или однократная ошибка в одном и многократная в других приемных регистрах. Во втором коммутаторе ЗО с помощью дешифратора, на который подается код позиции ошибки из соответствующего узла 28 и 29 обнаружения ошибок, дешифрируегся 1О мер позиции кода сооб.щения, котсрьй необходимо инвертировать в узле 31 коррекции dSoeB. Второй коммутатор ЗО управляющим выходом связан с узлом 31 коррекции сбоев, причем этот выход является выходом дешифратора кода позиции ошибки на п .выходов, где п - количество разрядов в сообщении, ч - количество избыточных контрольных разрядов. Узел 31 коррекции сбоев содержит ком бинациониую логику иа элементах И, ИЛИ, Н идентичную для каждого из п разрядов сообщения, реализующую инвертирование одного из разрядов, при условии раз. решения коррекции кода сообщения из второго коммутатора 30. Первый управляющий выход второго коммутатора 30 связан с третьим управляющим входом группы элементов И 33. Группа элементов И 33 предназначена для вьгработки послейовательиости сигналов для продвижения со общения по направлениям, определяемым выходами узла 32 управления режимом, гасемы 33 сравнения, второго коммугат 8814 ра 30, Hjynna элементов И 33 управляющими входами также связана с узлом 32 управления режимом, схемой 38 сравнения, .управляющими входами приемных ре/ист- рбв 26 я 27 и распределителем 34- импульсов. Связь второго коммутатора 30 и группы элементов И 33 сэстоит из ряда шин, по которым в группу элементов И 33 подаются сигналы о направлении движения сообщения, а также о необходимости записи признака сообщения для управляющего модуля в регистры 41 и 42 передачи. Группа элементов И 33 информационными входами связана с информа- цитнымй выходами узла 31 коррекции сбоев разряды сообщения) и- информационным выходом счетчика 37. Управпяющамл выходами группа элементов И 33 связана с элементом И 36 длч управ- ления занесением кода в счетчик 37, счетчиком 37 для вычитания нз него , если его содержимое не равно нулю. Информационными выходами группа элементов И 33 связана всеми разрядами сробщення, через группу элементов ИЛИ 4О с первым коммутатором 39 и разрядами кода счетчика 37, с первым 41 и втсрь1м 42 передачи регистрами. Распределитель 34 импульсов идентичен 14.114,Р. Управляющие входы распределителя 34 импульсов связаны соответственно с управляющими входами блока 2 контроля магистрали, а второй управляющий выход распределителя 34 импульссф связан с первым кадлмутатором 39. Узел 32 управления режимом содержит набор элементов И, ИЛИ, ;НЕ и предназначёй для выработки управляющих сигналов, зашющих режим работы блока 2 контроля магистрали,в частности режим передачи сообщения для управляющего модуля, режим нулевого слова, режим передачи сообщения для неуправляющего модуля. Элемент ИЛИ 35 содержит набор схем ИЛИ по числу разрядов счетчика и информационным выходом подключен к элементу И 36 и предказиачен для сборки одноименных счетчика из первого 26 и второго 27 приемных регистров. Элемент И 36 для занесения содержимого разрядов счетчика циклов приемных регистров 26 и 27 в счетчик 37, соединен информационной связью со счетчиком 37, который информационным выходом подключен к схеме 38 сравнения; предназначенной для определения иулевого значения счетчика 37. Схема 5В орав-, нения включает набор схем И.

irjpynna элементов ИЛИ 40 преяназначеиа для передачи управляющих и информационных сигналов в первый коммугагор 39. Г{)уапа элементов ИЛИ 40 связана первымуправлтощим входом; с управляющим выходо.м узла 32 управления режимом а управляющим выходом - с первым коммутатором 39. Первый коммутатор 39 содержит наборы схем ИЛИ, И в предназначен для выполнения передачи сообщения соответственно из первого 26 к втфого 27 приемных регистров в первый 41 и второй 42 регистры передачи, при условии отсутствия ошибок;, передачи содержимсго приемного регистра, в котором находится правильное сообщение в оба регистра 41, 42; передачи пересылок из группы элементов ИЛИ 40 в .оба регистра 41 и 42 передачи скорректированного кода сообщения, если хотя бы в одном из приемных регистров было сообщение с одной ошибкой и его возможно было восстановить Первый коммутатор 39 первым в вгорым информационными выходами соотвегственно связан с первым 41 и вторым 42 регисграми передачи.

Первый 41 и еторой 42 регистры передачи аналогичны приемным регистрам 26, 27 и предназначены для хранения сообщения на время передачи в последующие приемные регистры магисграпи, Информаг цяонкые выходы первого 41 в второго 42 регистров -.передачи соответст)аенно осж- ключены к первому и второму информационным выходам 2 к(жгропя магнатрали. Управляющие входы регистров 41 и 42 передачи связаны с четвертым управл5пощикг выходом группы элементов И 33, служат для установки в соответствующих разрядах сообщения признаков неустранимого сбоя я признака сообщения для управляющего модуля.

Блоки 6.1-6.Р коммутации (фиг. 4) предназначены для контроля инфсрмации и повышения ее достоверности при межрегистровых перерылках, что достигается путем аатоматическсЛ пересылки правильней информации хотя бы из одното приемного регистра З.К, 4.К, IB оба передающих регистра 7.К, 8.К. В состав .-го блока 6.-(с коммутации входят первый элемент ИЛИ 47.1с, второй элемент ИЛИ 48«, первый 49,iLi второй 5О.С, третий 51-К и четвертьй 5 2.1 элементы И, третий ЗЗ.и четвертый 54.tэheмeнты ИЛИ. Инфор-, мация .;с выхода приемнсяго регистра Зi поступает на вход первого элемента ИЛИ 47,k где она проверяется с. помощью опв° рации исключающее ИДИ на равенство

с информацией, поступающей со входа приемного- регистра 3. k на второй информационный вход первого элемента ИЛИ 47J; В зависимости от результата -сравнения, информация в передающий регистр 7. k поступает либо из приемного регистра З. -первсй группы через первый элемент И 49.iiH элемент ИЛИ 53ж, либо из приемного регистра 4.k второй группы через второй элемент И SO.if. и элемент ИЛИ 53. Втсрая половина блока 6 1с коммутации, включающая приемный регистр 4 второй группы, второй элемент ИЛИ 4Sifc третий 5 l.-fc и четвертый 52Аэлементы И, четвертый элемент ИЛИ 54 R, имеет то же функциональное назначение и те же связи, что и первая половина блока.

Устройство работает следующем образом.

Модули 25.1-25.Р вычислительной системы обмениваются между собой слов&ми информации, при этом можнр вьшелить исполнвтелвные модули, выделяющие функции хранения к обработки информации, и усфавляющие.модули, в качестве которых используются центральные прсадессоры, снабженные развитым программным обеспечением для анализа и принятия рещений по сбойным ситуациям.

Функционально устройство для сопряжения модулей вычислительной системы с контролем (фиг. 1), исключая блок 1 и блсж 2 к 1тропя магистрали, можно разделить на Р идентичных частей по числу модулей 25.1-25.Р вычислительной системы. Работу устрсйства будем рассматривать ва примере работы it -ой части устройства совместно с блоком 1 синхронизации и блоком 2 контроля магистрали.

По пуску устройства блок 1 синхронизации начинает вырабатывать обе серии сигналов А1 н В1, под управлением кото рых в магистрали начинают циркулировать свободные слова. Каждым сигналом В1 содержимое приемных регистров 3.1-З.Р, 4.1-4.Р передается через блоки 6.1-6.Р коммутации в передающие регистры 7.17.Р, в.1-8.Р. Каждым сигналом А1 информация передаюшнх регистров 7.1-7.Р, 8.1-8.Р пересылается в приемные регистры 3.1-З.Р, 4.1-4.Р,

Каждая -ая часть устройства может независимо работать в одном из трех режим овТ

- Запись - Пересыпка слова инфq мaции из модуля вычислительной системы магистраль} -чтение (управл5пощий режим) - при слова информации из магистрали управл ющим модулем; -чтение (исполнительный режим) прием слбва информации из магистрали исполнительным модулем. При чтении (исполнительный режим ИСП) по сигналу Сброс управляющий регистр 22.1с устанавливается в состоя ние: СвободноЧСв), Читать(Чт),ИСП По сигналу А1 содержимое передающих регистров 1. -1, 8.fc.-l пересылается соответственно в приемные регистры 3Ji, 4.;. По сигналу А2 и состояниям управляющего регистра 22..-k- Св, Чт, ИСП и отсутствию признака слова управляющего модуля на выходе первого элемента ИЛИ S.ic первой группы произвол дится опрос блоков сравнения адреса 15(, . По сигналу Равно, т.е. сравнению собственногоадреса модуля с адресом получателя, с выхода элемента ИЛИ 17Л устанавливается соответсгбующий тригге в упоа.вляющем регистре 22fc По сигнал Не paako никаких действий не производится. . По сигналу В1 содержимое регистров 3,4с, 4.-k параллельно всеми разрядами через блок коммутации 6. поступает в поредеющие регистры. 7.-fc, 8k. Пересылка в приемные регистры 3k. 4i: контролируется элементами ИЛИ 47.4с и 48.1; при этом, если в обоих регистрах информация верная, то она пересылается в передающие регистры 7.1, 8 k через элементы И 49.S 52jf. Если, например, информация в приемном регистре 3.. t неверная, а в приемном регистре 4.ic- верная, элемент ИЛИ 47.11 своим управляющим бьосодом открывает элемент И 5Qi тем самым в передающий регистр 7.с будет передана верная информация из приемного регистра 4, и осуществляется автоматический обход отказавшего приемного регистра. В случае отказа обоих приемных регистров З, , 4.1с, информация, содержащая в них, пересылается соответственно в передающие регистры 8. fi, 7Л и в Д191льнейшем обрабатывается в блоке 2 контроля магистрали.. ,.: Информация в коде Хэмминга, принята в передающие регистры, 7.1(, 8.1: контро лируется блоками 11.К, 12.k обнаружения ошибсж. Контроль осуществляется следующим образом, i информация изпередающего регистра 8«1(, подается потенциалами всех разрядов-на вход блока 12.if обнаружения ошибок. (фиг. 3), причём в каждую сЪергку 43.143.Ч по модулюдва группы подаются все информационные разряды и один соотвег ствующий контрольный разряд. Младшие ч информационных разрядов подаются, на вторые входы элементов И 44.1-44.4 группы, на первые входы котсрых подаются результаты срерток по чётности соот. ветствующих проверочньЬс групп. При наличии сбоя в одной из ч проверочных трупп э.тот сбой фиксируется дешифратором 46, которьШ вьщает сигнал Однократный сбой , а код позиции слибочного разряда сообщения вьшается со всех элементов И 44,1-44.4 группы на информационный выход блока обнаружения ошибок. .В случае обнаружения несколь.сах ошибок онибудут: зафиксированы в нескольких свертках группы и на выходах соответствующих элементов И 44.1-44.Ч установятся уровни сбоев, которые поступят на поррговьй элемент 45, срабатывающий при поступлении более одного саг. нала с элементов И 44,1-44.Ч/группы. ВьЕхоД порогового . элемента 45 через-дещифратор 46 поступает на выход блока 12,k обнаруисения ощибсж в виде сигнала Мнсяократный сбой В случае приеп4а правильной информации из дешифратс а 46 на вькод блока обнаружения ощибок поступает сигнал Нет сбоя. :Если нет сбоя в одном из передающих регистров 7.11, 8,с(фиг. 1) или вобоих передающих р истрах 7. k, 8. k , то по состоянию Равщо- сигналом В2 производится парафазная передача правильной информации IJ3 одного из передающих регистров 7.1с, It в буферный: регистр 23. -Ц первой группы. Далее производится сброс обоих передающих -р гисгров 7.- и 8.- по сигналу ВЗ, а также перевод управляющего регистра 22.1 в состояние Занято (Знт) и Запись (Зп), в модуль 25.1сс блока 19.Х выработки управляющих сигналов поступает запрос на передачу информации из буферного регнст-. ра 23it. По приему запроса модуль 25 производит сьем информации буферного регистра 23. k. Бели результат ксжтроля - Многократньй сбей в одном из передающих регистров 7., 8. и Однократный сбой в другом передающем регистре, то по сигналу В2 .информация из регистра, в jcoTopoM произошел однократный сбей, пеедается в буферньй регистр 23. It и даее по сигналу A3 парафазно заносится ерез блок 6.fc коммутации в оба передающих регисгра 7. fc и 8. k , состояние Равно снимается. Ec;jH результат контроля - Многократный сбой в обоих передающих регистрах 7.1с , 8. i , то по сигналу В2 в разряды признака слова управляющего модуля и сбоя обоих передающих регистров 7.k, 8. заносятся единицы. Это означает, что принятая сбойная информация адресуется управляющему модулю для дальнейшей обработки. При чтении (управляющий режим Упр) по состояниям Чт, Св, Упр и наличии Г в разрядах признака слова управл5пощего модуля, сигналов А 2 устанавливается триггер управляющего слова (Туе) в управляющем регистре 2i2.1c Сигналом В2 по состояниям Туе, Чт, Св осуществляется передача содержимог обоих передающих регистров 7,1с , 8. 1с без контроля соответственно в буферные регистры первой 23. k, и второй 24, It. групп. Сигналом ВЗ по предыдущим состоянвям осуществляется сброс регистров 7Jfe 8. перевод управляющего регистра 22. к в положение Знт, выработка запроса на передачу информации в 25Л При поступлении сигнала опроса буферног регистра 23. It и состоянием управляющего регистра 22.К - Чт. Знт, Туе содержимое буферного регистра 24. пересылается в буферный регистр 23.-(с, осу-, Ецествляется перевод управляющего регасгра 22.-k в состояние Зп, вырабатывается запрос на передачу, в модуль 25|в второго слова информации. записи - запрос из модуля 25. V на передачу информации в магистраль ус« танааянвает триггер: За tip в управляющем реГ- истре 22. k. Сигналом А2 по со стоядаяям Зп, ЗНТ, Запр информация из модуля 25.1 передается в буферньй регистр 23, поступает также одновременно собственный aPopQO модуля 25. { из рагкстра 18. Мадраса. По сигналу A3 в зависимости от значений рвзрядов режима (запись, чтение), в апове, принятом в буферный регистр 23.t, обработка может выполняться.двояко. Два разряда режима могут быть одновременно установлены только управляющи модулем для целей диагностики магистра ли, .При этом в слове адрес отправителя устанавлявается равным адресу получателя и равным собственному адресу. Слово может содержать правильную или преднамеренно сбойную информацию, что необходимо для целей контроля. В силу сказ нного, при установленных разрядах режима требуется запретить контроль информации по записи, выполняемой блоком 13.1с. обнаружения ошибок, третьей группы. Если разряды режима установлены, то по сигналу A3 и состоянием Зп, Знт, Запр производится анализ на занятость в блоке 19.1с выработки управляющих сигналов. Если слово свободно, то устанавливается триггер Тслв в управляющем регистре 22. fc, с помощью перечисленных выше состояний блокируется сигнал опроса результата контроля информации в буферном регистре 23,1;. Если разряды режама не установлены, то по сигналу A3 в состояниям Зп, Знт, Запр производился анализ слова на занятость и опрос результата контроля информации буферного регистра 23., поступающего в блсж 19,k выработки упраЕШяющих сигналов из 13 . -k обнаружения схиибок. Если слово занято ft нет сбоя, го по сигналу 82 никаких действий не произво двтся. Если слово свободно и нет сбоя, то ио сигналу В2 содержимое буферного регистра 23.-k, парафазно заносится через блок 6.-k коммутации в оба передающих регистра 7. fc,, 8, -fc. Далее по сигналу ВЗ производится сброс буферного регистра 23. fc и перевод управляющего регистра 22. «. в состояние Чт и Св. Если блок 13. обнаружения ошибок выявляет сбой, то по сигналу В2 в счетчик 20, сбоев добавляется , Далее, если содержимое счетчика 2О. t сбоев не равно величине ф, где ф - допустимое число повторных сбойных передач информации из модуля 26.fcB буферньй регистр 23, (с, то по.сигналу ВЗ производится сброс буфернсяо регистра 23. К и отправляется запрос в модуль 25, -fc на повторный прием информации. Если обнаружен сбой и содержимое счетчика 20. k сбоев равно величине ф и слсюо свободно, то по сигналу ВЗ содержимое буферного регистра 23.1с пэредается в оба передающих регистра 7.Ц ,8,1, одновременно устанавливается признак слова управляющего модуля. Эта информация в дальнейшем будет анализироваться .н обрабатываться управляющим модулем. По состояниям Зп, содержимое счетчика 2О.4(. сбоев равно ф и слово свободно сигналом ВЧ производится с ;рос буферного регисгра 23. t и перевод управляощего регистра 22. t в состояние Чт н Св. Модуль передал информацию в магистраль и готов к арному новой информации из магистрали. Информация передаваемая по магистрали контролируется блоком 2 контроля магистрали, (фиг. 1), который работает следующим образом. По сигналу А1 информация передающих регистров 7.Р, 8.Р сдвигается в приемные регистры 2 и 27. Выходы приемных регистров 26 и 27 все ми разрядами поступают в первьгй коммутатор 39, разряды признака состояния слова (занято, свободно) и признака слова управляющего модуля поступают в узел 32 управления режимом, где формируются соответствующие управляющие сигналы Выходы приемньсх регистров 26 и 27 раз рядами счетчика-циклов поступают на элемент ИЛИ 35, остальные разряды приемных регистров 26 и 27, охваченные контролем по коху Хэмминг1а, поступают соответственно в первый 28 и второй 2Q обнаружения ошибок и на входы узла 31 кфрекции сбоев. Комбинационные, схемы узла 32 управления режимом, у;элы 28 и 29 обнаружения ощибок срабатьюают и подают сигналы во второй коммуta, TCf 30, группу элементов 33 и группу элементов ИЛИ 4О. Далее срабатьюаюг схемы второго коммутатора ЗО, выходы KOTopcwo поступают в узел 31 коррекции сбоев и группу элементов И 3.3, Таким образом, комбинационнее схемы настраиваются на режим, соотв етствующий содержимому принятого слова. При этом возКЮжны три режима работы блока 2 кштроля магистрали. Первый режим - режим передачи слова для управляющего модуля.. Разряды призна ка слова управляющего модуля анализируются в узле 32 у правления, режимом. Ес.ли это слова управляющего модуля, то узел 32 управления режимом запрещает работу группы элементов И 33 и разрещает передачу информации через первый коммутатор 39 из приемного регистра 26 в регистр 41 передачи и из приемного регистра 27 в регистр 42 передачи. Передача осуществляется по сигналу В1 ноступающему в первый коммутатор 39 вэ распре делителя 34 импульсов. Содержимое регистров 41 и 42 передачи передается в приемные регистры В1, 4,1 по сигналу А1.- Второй режим - режим передачи слова для неуправляющего модуля. В этом режиме СЛОВ9 поппежит.контролю на наличие сбоев и в случае их обнаружения - :восстановлению. Первый узел 28 обнаружения ошибсж 29 контролирует содержимое приемного регистра 26, второй узел 29 обнаружения ошибок контролирует содержимое приемного регистра 27, результаты контроля подаются во второй коммутатор ЗО. При этом, если нет ошибок ни в одном из приемных регистров 26 н 27, то из второго коммутатора ЗО в группу элементов И 33 подается сигнал прямой передачи информации из приемных регистров 26 и 27через первый коммутатчз 39. В регистры 41 и 42 передачи и из узла 32 управления режимом в группу элементов И 33 такжеПоступает разрешение на та-кую передачу, которая выполняется по сигналу В1, аналогично с первым режимом, ЕсУ1Н один нз узлов 28 и 29 обнаружения ошибок указал на сбой в соответствующем приемном регистре, то нз вто рого коммутатора 30в группу элементов И 33 передается .сигнал на открывание соответствующих схем с тем, чтобы с помощью группы элементов ИЛИ 40 .« . первого коммутатора 39 передать сообшение из приемного регистра, в котором нет ошибки, в оба передающих регистра. Работа блока 2 происходит аналогично и в том случае, если один из узлов 28и 29 Ьбнаружения ошибки зафикс1фовал дверную (кратную) ошибку в соответсгвую шем приемном регистре, а в другом приемном регистре нет ошибки. Такой контроль и передача позволяют удалить из магистрали информацию и заменить ее правильной, тем -самым пс ысить достоверность гтереДачи. Если узлы 2S и 29 обнаружения ошибок зафиксировали сбои, прячем в одном из приемных регистров имеется однократная ошибка, то слова подле |(:ит .восстаовлению. В этом случав второй коммутатор ЗО огбирает из соответствующего уза 28 ипв 29 обнаружения ошибсж код osmiBR ошибке, дешифр1ф у ат его и подает екод(фова1ты(1 номер позиции в узел 31 коррекция о0оев олл инвертирования соответствующего бита Б слове. По второму 1фавл$ао(аему выходу второй коммутатор ЗО предает сигнал в группу элвмбнтов И 33 на открытие соответствующих схем для передачи скорректированного кода слова через группу алемейтов ИЛИ 40 и первьй коммутатор 39 в оба 1)егистра 41 и 42 передачи. М едача осу ществляется по сигналу В1. Если контроль приемных регистров 26 и 27 узлами 28 и 29 обнаружв„ ИИ ошибок показал наличие крат 1ыхсбоев в шибсж показал наличие кратных сбрей в S0 обоих првел ных регистрах 26 и 27, то слово не подлежит восстановленшо и необ-. кодймо его переслать в управляющий модуль. В этом случае второй коммут;агор ЗО передает в группу элементов И 33 управляющий сигнал о прямой передаче слова нз приемных регистров 26 и 27 через первый коммутатор 39 в регистры 41 и 42 передачи по сигналу А2 а запн. си признака слова для управляющего и признака неустранимого сбоя в соответствующие разряды регистров 41 и 42 передачи по сигналу A3. Одновременно, с контролем слов на наличие ошибок и восстановления их в случае одиночных ошибок в блоке контроля магистрали каждое слово для неуправпяюм щего модуля проверяется на число циклов, которые сообщение прошло по магистрали, т.е. сколько раз сообщение прощло через блок 2 контроля магистрали и не было принято получателем. Это число может задаваться произвольным от О до ) где и - количество разрядетз счетчинса 37, Если содержимое счетчика циклов равно нулю, то слово не принято ни одним из модулей системы и возможны недейстйн- тельные адреса получателей, поэтому для определения причины в это слово записывается признак слсжа для управляющего модуля тем самым оно удаляется из ма гистрали. Эта проверка вьшолняегся следующим образом:, значение разрядов счет, чика циклов через элемент ИЛИ 35 и элемент И 36 нз обоих приемных регисТров 26 и 27 заносится в счетчик 37 по сигналу А2, его содержимое анапизируегся на нз ьсхемсй 38 сравнения и, воле совержкмое счетчика 37 равно нулю, то сигналом A3 через группу элемен ов И 33 в регистр 41 и 42 передачи запйсываетсг признакслова для управляющего модуля. Если содержимое счетчика 37 не равно нулю, то по сигналу 42 из соД жимсмго счетчика 37 вычитается единица, а. его нойое содержимое записывается в соответствующие разряды регистров 41 и 42 передали по сигналу A3, Третий режим - режим передачи нуле вого слова, т.е. в данньй отрезов времен ми приемные и перемещающие регистры не хранят информации. В этом случаб в узле 32 управления режимом отсутствует признак занятости, по которому он блетснру ет работу группы элементе И 33 и группы элемент з ИЛИ 4О, тогда по сигналу В1 из распределителя 34 импульсов в регист ры 41 и 42 передачи через твердый ком мутатор 39 заносятся все нули. 24 Устройство Для сопряжения модулей вычислительной системы с контролем позволяет значительно повысить надежность за счет: применения дублирования . Ha6qpa пассивных шин и основньк регистров и узлов; введения поэлементного резервирования в магистрали и аппаратурных блоков, автоматически осуществляющих Bbi6op путей обхода отказавших и элементов; использования общего для всей магистрали, аппаратурнр реализованного блока ксжгроля магистрали, позволяющего контролировать и восстанавливать информацию. Циркулирующую в магистрали; использования одного или нескольких управляющих модулей с развитым программным обеспечением для целей диагностики магистрали и реализации повторнь1Х передач информации. Формула изо б..р е т е н и я 1. Устройство для сопряжения модулей вычислительной системы с контролем, содержащее первую группу приемиых регистров, первую группу передающих регистров, блок синхронизации, группу распредели телей импульсов, первую группу блежов qpeBHeHK9 адреса, группу регистров адреса, группу управляющих регисхров, первую Группу буферных регистров, первую группу элементов ИЛИ| группу блоков выработки управляющих сигналов, причем первый выход блока сиихрон113аиии соединея С входами всех распределителей импульсов группы, вторсй выход блока синхроиизацин соедяяен со вторыми вхойами всех рвспределктелвй импульсов я с управляющими входами всех приемных регистров первой группы, R второй выхоДы каждся о распределителя импульсов группы соединены с первым н вторымг с нхршизирующями вхслами соответствующего блсяса .вь1рабогкй управляющих сигналов группы, первый выход кажд((жа вьфаботки управляющих сигналов группы соединеи с управляющим входом соотввгствуюа{его передающего perftcipa перв( группы, выход каждого {:-го передающего регистра первой группы соединен с перьым информационнь{м . входом б гфёрного регистра nepBt группы и с информацибиным входом (1)-го приемисто регистра первой группы, вгорЫ информааиоиный вход -го буферного регистра первой группы является первым входом устройства, информацио т- кый выход каждого регистры адреса группы соедикеи с первым информацлоньым входом соответствующего блока сравнения адреса первой группы н с третьим кнформационным входом соответствующего бу(|)ерного регистра первой группы, информа ционный выход каждого приемного регвст pa первой группы соединен с первым вхо дом соответствующего элемента ИЛИ пер вой группы и со вторым информационным входом соответствующего блока сравнения адреса первой группы, вькод каждого элемента ИЛИ первой группы соединен с первым информационным входом соответст вующего блока вьфаботки управляющих сигналов группы, второй, третий, четвертый и пятый выходы каждого блока вьфаботки управляющих сигналов группы соеди нены соответственно с управляющим входом соответствующих блоков сравнения адреса первой группы, с первым управляюшим входом управляющего регистра группы, с соответствующим выходом устройства, с управляющим входом соответст вующего буферного регистра первой группы информационный выход каждого-угфавляющего регистра группы соединен со вто рым информационным входом соответсгвующего блсжа выработки управляющих сиг- налоэ вторые управляющие входы каждо го управляющего регистра образ т . группу управляющих входов устройства, , отличающееся тем, что, с це .лью повьпиения надежности устройства в него введены блок контроля магистрали, вторая группа приемных регистров, группа блоков коммутации, вторая группа передающих регистров, первая, вторая и третья группы блоков обнаружения ощибок вгора я группа блоков сравнения , вторая группа элементов ИЛИ, группа счетчиков сбоев, группа дещи(|раторов и вторая группа буферных регистров, причем информационные выходы последних .передающих регистров первой и второй Групп соединены соответственно с первым и вторым информационными входами блока контроля магистрали, первый и вгор(Луправляющие входы которого соединены соответственно с первым и вторым выходами блсжа синхронизации, первый а второй информационные вькоды . контроля магистрали соединены соответственно с информационными входами первых приемных регистров первой и второй групп, вькод каждого приемного регистра второй группы соединен со вторым входом соответствующего элемента ИЛИ первсЛ группы, с первым информационным входом соответствующего блсжа срав(ения .адреса второй группы, первый, второй, третий и четвертый входы каждого блока коммутации группы соединены соответст вевво с информационным и входами соответствувхцего приемного регистра первой группы, с выходом соответствующего. приемного регистра первой группы, с ин-. фсрмационными входами соответствующего ариемн яго регисх-ра второй группы,с выходом соответствующего приемного регистра второй группы, управляющие входы всех приемных регистров второй группы соединены со вторым выходом блока синхронизации, первой и второй информационные выходы каждого блока кoм 4yfaции группы соединены соответственно с информаци ными входами ссютветствующих передающих регистров первой и второй групп J инфqэмaциoнный .выход k-го передающего регистра второй группь; соединен с информационным входом (4t+l)ro приемного регистра тзуппы, с инфсрмационным входом го буферного регистра вторЫ группы, информ&цишный вход каждого буферного регистра второй группы соединен с пятым инфсрмацисжным входом соответствующего буферн Й«орегистра первой группы, первый, втс ей и шестой выходы каждого блока выработки управляющих сигналов группы соединены соответственно с управлярющнм входом соответствующего передающего регистра второй группы, с управляющим входом соответствующего блока сравнения аореса второй группы а с уп-. равляющга входом буферного регистра второй группы, вяфо1 4а1шонный выход каждого регистра адреса группы соединён со вто рым информационным входом соответствующего блсжа сравнения второй группы, выходь соответствующих блакаб сравнения адреса первой и вторЫ( групп соединены с первым и вторым входами соответствующего элемента ИЛИ второй группы, выход каждого элемента ИЛИ вторей группы соединен с управляющим входом сот-ветствующего управляющего регистра группы, седьмсА выход каждого блока выработка управляющих сигналов группы соединен со вхсщом соответствующего счетчика сбоев группы, выхоа каждого счетчика сбоев соединен с соответстаующам входом дешифратора группы, выход кажлого дешифратора группы соединен с третьим Бхсаом соответствующего блока в{фаботкв управляющих сигналов руппы, внформациокные выхлопы каждого предающего регистра первой а второй рупп соединены соответственно со вхоами блоков обнаружения оишбок первой и второй групп, выходы блоков обнаружения ошибок первой н второй групп соеди- , яены соогвотственно с четвертьви и пятйй входами соответствующего блока выработки управляющих сигналов группы, третий выход н пятый вход каждого блмса коммутации группы образуют соответственно первую группу информационных uvoiono к вторую Ypynny информационных входов уст- ройства, выход каждого буферного регистра первой группы соединен с информационным входом соответствующего блока обнаружения ошибок третьей группы я с третьим входом соответствующего блока выработки управляющих сигналов группы, выход каждого блока обнаружения ошибок третьей группы соединен с шестьм входом соответствующего блока выработки управлшощих сигналов -группы. 2. Устройство по п. 1,отличающее с я тем,что блок контроля магистрали содержит первый и второй приемные регистры, первый н вторсй узлы обнаружения ошибок, узел коррекции сбоев, элемент ИЛИ, элемент И, счетчик, группу элементов И, схему сравндаия, первый и второй регистры передачи, распределитель импульсов, группу элементов ИЛИ.. первый н второй ксллмутаторы и узел управления режимом, причем первый и второй информационные входы блока соединены с икформациочнымн входами первого и второго приемных регнстров, управляющие входы которых соединены с первым выходом распределителя импульсов к с синхронизи(руюшими вхо дамв элементов И группы, выход первого приемного регистра соединен со входом первого узла обнаружения ошибсж, с первыми входами узла управления режкмом, узла кфрекциа сбоев, с первым вхо дом элемента ИЛИ и первым входом первого коммутатора, выход второго приемного регистра соединен -со вхоаом вгорсм го узла обнаружения ошибок, со вторым вхооами узла управления режимом, элемента ИЛИ, узла коррекции сбоев и вторым входом первого коммутатора, управлшошнй в информационные выходы первого вторш о узлст обнаружения ошибок соединены соответственно с первь1м и вторым управляющими информационными входами второго коммутатора, первый и втсров управляющие выходы которого соединены соответственно с управляющим «ходом узла коррекции сбоев и с 1(1ервыми управляющими входами элементов И груп1Ш, выход узла коррекции сбоев соединен с оервыми информационными входами элементов И группы, первый и второй выходы узла управления режимом соединены соответственно со вторыми входами эле- ментами И группы, с первь1ми входами элементов ИЛИ группы, первый, второй, третий, четвертый н пятый выходы элементов И группы соединены соответственно с первь1М входом элемента И, с управляющим входом счеТЧика« со вгс ыми вхог. дами элементов ИЛИ группы, с управляющим входом первого и второго регистров передачи, с информационными входами первого и второго регистре передачи, выходы которых являются выходами блска, выход элемента ИЛИ соединен со вторым входом элемента И, выход которого соединен со счетным входом счетчика, информационный выход счетчика соединен со входом схемы сравнения и со вторыми ий- ; формационными входами элементов И группы, выход схемы сравнения соединен с третьими входами элементов И группы, вторЫ выход распределителя импульсов соединен с управляющим входом первого коммутатора, выходы элементов ИЛИ группы соединены с третьими информационными и вторым управляющим входами пзрвого коммутатора, первый и второй выходы которого соединены срответствен о со втq)ымв Кйфбрк АЦ бЬнЬЫ входами первого и второго регистров передачи, Устройство по п. 1, о т л н ч а Щ е е с я тем, что блок С)бнаруже11ия . ошибок содерясЬт группу сверток помодуяю два, группу элементов И, Пороговьй ; элемент и дешифратор, причем входы свер модулю два группы соединены со входами блока, вьгходы сверток по модулю два группы соответственно соединены с первыми входами элементов И группы, вторые входы которых соединены со входом младщих информационных разрядов блока, выходы элементов И явля f информационными выходами блока и соединены соответствующими входами порогового элемента и дешифратора, выхоА Дешифратора является управл51Ю1цим выходом блока, выход порс ового элемента сс единен с управляющим входом дешифратора. 4. Устройство по п. 1, о т л и ч а Ю щ е а с я тем,что блок коммутации содержит первый, второй, третий и чвтвертый элементы ИЛИ, первый второй, третий и четвертый элементы И,, причем первый, второй, третий и четвертый информационные входы блока оединены соответствеино с первым входом первого элемента ИЛИ, со входом первого элемента ИЛИ,с первым входом второго элемента ИЛИ и со вторым входом второго элемента ИЛИ, первый и второй выход аервого и второго элементов ИЛИ соединены соответственно с первыми входами первого, второго, третьего н чег- вертого элементов И, вторые входы всех элементов И объединены и соединены с управляющимивходом блока, третьи входы первого и третьего элементов И соединены со вторым входом блока, третьи вх& ды второго и четвертого элементов И сое динены с четвертым входом блока, выходы первого, второго, третьего и четвертого 80 элементов И соединены соответственно с первым и вторым входами третьего в чегBiepToro элементов ИЛИ, выходы которых являются выходами блока, третьи входы третьего и четвертого элементов ИЛИ. соединены с пятым информационным входом блока. Источники информации, принятые во внимание при экспертизе 1.Патент США NO 3947618. кл. 340-147 d Р, рпублнк. 19716. . 2.Авторское свидетольст-ю СССРпо заявке № 255732О/18-24, кл. q 06 F 11/00 (прототип).

I I

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство связи для вычислительной системы | 1977 |

|

SU734654A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1163361A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

Авторы

Даты

1981-02-23—Публикация

1978-09-08—Подача